Philips PDTA114EU Datasheet

DISCRETE SEMICONDUCTORS

DATA SH EET

ook, halfpage

M3D102

PDTA114EU

PNP resistor-equipped transistor

Product specification

Supersedes data of 1998 May 18

1999 Apr 13

Philips Semiconductors Product specification

PNP resistor-equipped transistor PDTA114EU

FEATURES

• Built-in bias resistors R1 and R2

(typ. 10 kΩ each)

• Simplification of circuit design

• Reduces number of components

and board space.

APPLICATIONS

• Especially suitable for space

reduction in interface and driver

circuits

• Inverter circuit configurations

without use of external resistors.

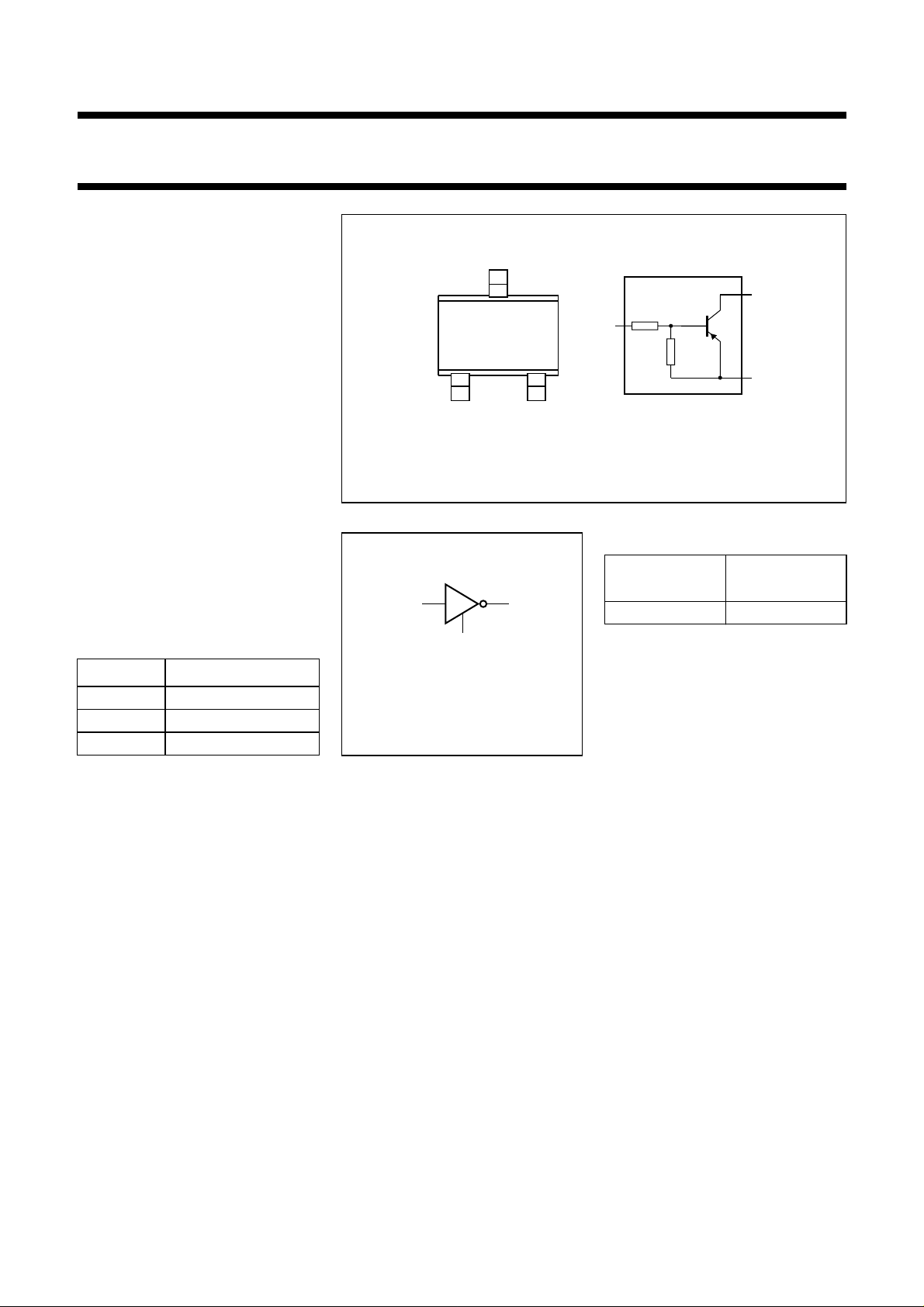

handbook, 4 columns

Top view

Fig.1 Simplified outline (SOT323) and symbol.

3

3

R1

1

R2

2

21

MAM135

DESCRIPTION

PNP resistor-equipped transistor in a

SOT323 plastic package.

NPN complement: PDTC114EU.

PINNING

PIN DESCRIPTION

1 base/input

2 emitter/ground (+)

3 collector/output

1

2

MGA893 - 1

3

Fig.2 Equivalent inverter

symbol.

MARKING

TYPE NUMBER

MARKING

CODE

PDTA114EU ∗03

Note

1. ∗ = - : Made in Hong Kong.

∗ = t : Made in Malaysia.

(1)

1999 Apr 13 2

Philips Semiconductors Product specification

PNP resistor-equipped transistor PDTA114EU

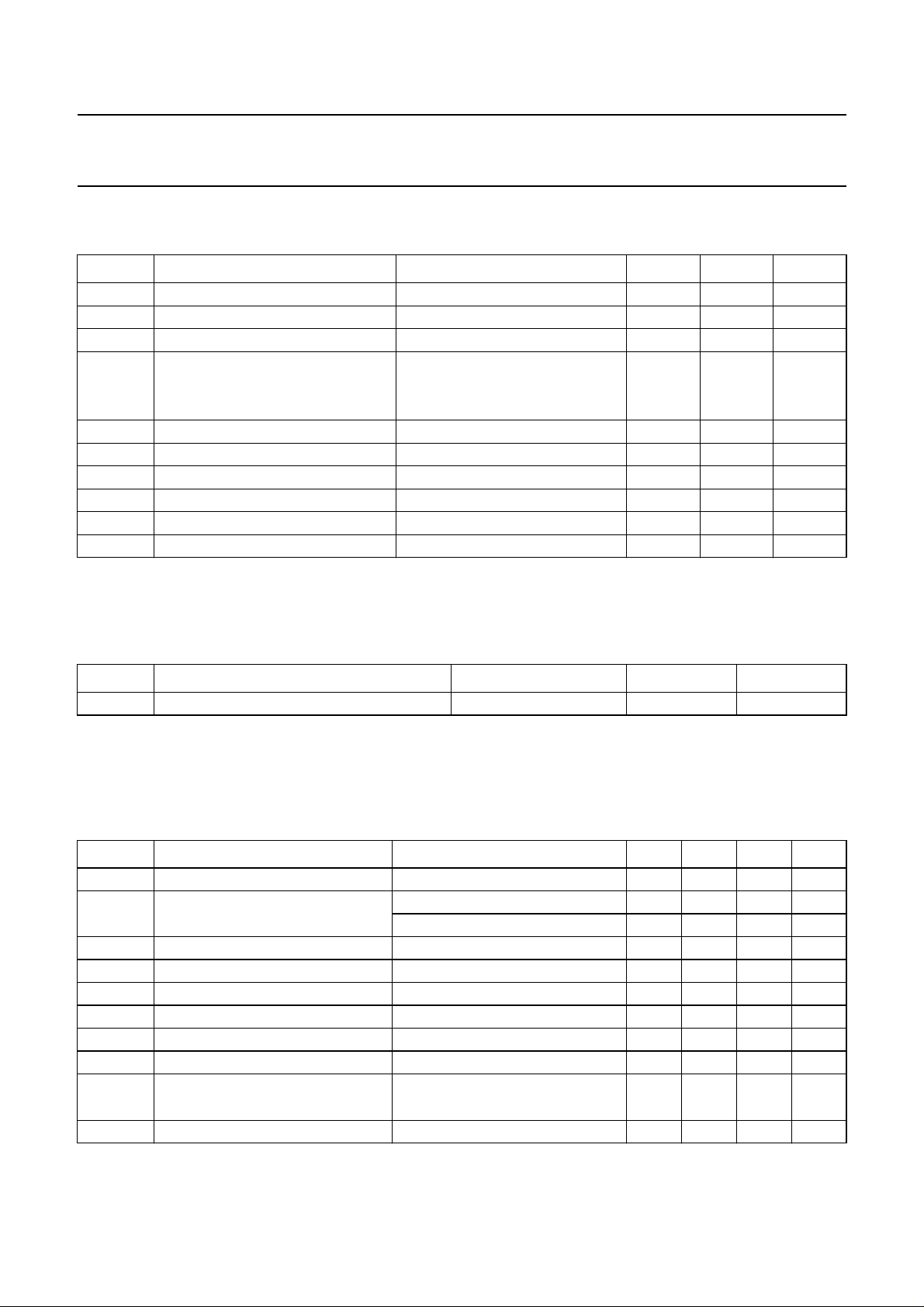

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

V

V

V

I

I

P

T

T

T

O

CM

CBO

CEO

EBO

I

tot

stg

j

amb

collector-base voltage open emitter −−50 V

collector-emitter voltage open base −−50 V

emitter-base voltage open collector −−10 V

input voltage

positive − 10 V

negative −−40 V

output current (DC) −−100 mA

peak collector current −−100 mA

total power dissipation T

≤ 25 °C; note 1 − 200 mW

amb

storage temperature −65 +150 °C

junction temperature − 150 °C

operating ambient temperature −65 +150 °C

Note

1. Transistor mounted on an FR4 printed-circuit board.

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th j-a

thermal resistance from junction to ambient note 1 625 K/W

Note

1. Transistor mounted on an FR4 printed-circuit board.

CHARACTERISTICS

=25°C unless otherwise specified.

T

amb

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

I

CBO

I

CEO

I

EBO

h

FE

V

CEsat

V

i(off)

V

i(on)

collector cut-off current IE= 0; VCB= −50 V −−−100 nA

collector cut-off current IB= 0; VCE= −30 V −−−1µA

I

= 0; VCE= −30 V; Tj= 150 °C −−−50 µA

B

emitter cut-off current IC= 0; VEB= −5V −−−400 µA

DC current gain IC= −5 mA; VCE= −5V 30 −−

collector-emitter saturation voltage IC= −10 mA; IB= −0.5 mA −−−150 mV

input-off voltage IC= −100 µA; VCE= −5V −−1.1 −0.8 V

input-on voltage IC= −10 mA; VCE= −0.3 V −2.5 −1.8 − V

R1 input resistor 7 10 13 kΩ

R2

------- R1

C

c

resistor ratio 0.8 1 1.2

collector capacitance IE=ie= 0; VCB= −10 V; f = 1 MHz −−3pF

1999 Apr 13 3

Loading...

Loading...