查询PCF2104x供应商

INTEGRATED CIRCUITS

DATA SH EET

PCF2104x

LCD controller/driver

Product specification

Supersedes data of 1997 Apr 01

File under Integrated Circuits, IC12

1997 Dec 16

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

3.1 Packages

3.2 Available types

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 PINNING

7 PIN FUNCTIONS

7.1 RS: register select (parallel control)

7.2 R/W: read/write (parallel control)

7.3 E: data bus clock (parallel control)

7.4 DB0 to DB7: data bus (parallel control)

7.5 C1 to C60: column driver outputs

7.6 R1 to R32: row driver outputs

7.7 VLCD: LCD power supply

7.8 OSC: oscillator

7.9 SCL: serial clock line

7.10 SDA: serial data line

7.11 SA0: address pin

7.12 T1: test pad

8 FUNCTIONAL DESCRIPTION

8.1 LCD bias voltage generator

8.2 Oscillator

8.3 External clock

8.4 Power-on reset

8.5 Registers

8.6 Busy Flag

8.7 Address Counter (AC)

8.8 Display data RAM (DDRAM)

8.9 Character generator ROM (CGROM)

8.10 Character generator RAM (CGRAM)

8.11 Cursor control circuit

8.12 Timing generator

8.13 LCD row and column drivers

8.14 Programming of MUX 1 : 16 displays with

PCF2104x

8.15 Programming of MUX 1 : 32 displays with

PCF2104x

8.16 Reset function

9 INSTRUCTIONS

9.1 Clear display

9.2 Return home

9.3 Entry mode set

9.3.1 I/D

9.3.2 S

9.4 Display on/off control

9.4.1 D

9.4.2 C

9.4.3 B

9.5 Cursor/display shift

9.6 Function set

9.6.1 DL (parallel mode only)

9.6.2 N, M

9.7 Set CGRAM address

9.8 Set DDRAM address

9.9 Read busy flag and address

9.10 Write data to CGRAM or DDRAM

9.11 Read data from CGRAM or DDRAM

10 INTERFACE TO MICROCONTROLLER

(PARALLEL INTERFACE)

11 INTERFACE TO MICROCONTROLLER

(I2C-BUS INTERFACE)

11.1 Characteristics of the I2C-bus

11.2 Bit transfer

11.3 Start and stop conditions

11.4 System configuration

11.5 Acknowledge

11.6 I2C-bus protocol

12 LIMITING VALUES

13 HANDLING

14 DC CHARACTERISTICS

15 AC CHARACTERISTICS

16 TIMING DIAGRAMS

17 APPLICATION INFORMATION

17.1 8-bit operation, 2 × 12 display using internal

reset

17.2 4-bit operation, 2 × 12 display using internal

reset

17.3 8-bit operation, 2 × 24 display

17.4 I2C operation, 2 × 12 display

17.5 Initializing by instruction

18 BONDING PAD LOCATIONS

19 DEFINITIONS

20 LIFE SUPPORT APPLICATIONS

21 PURCHASE OF PHILIPS I2C COMPONENTS

1997 Dec 16 2

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

1 FEATURES

• Single chip LCD controller/driver

• 1 or 2-line display of up to 24 characters per line, or

2 or 4 lines of up to 12 characters per line

• 5 × 7 character format plus cursor; 5 × 8 for kana

(Japanese syllabary) and user-defined symbols

• On-chip:

– generation of intermediate LCD bias voltages

– oscillator requires no external components (external

clock also possible)

• Display data RAM: 80 characters

• Character generator ROM: 240 characters

• Character generator RAM: 16 characters

2

• 4 or 8-bit parallel bus or 2-wire I

C-bus interface

• CMOS/TTL compatible

• 32 row, 60 column outputs

• MUX rates 1 : 32 and 1 : 16

• Uses common 11 code instruction set

• Logic supply voltage range, VDD− VSS: 2.5 to 6 V

• Display supply voltage range, VDD− V

: 3.5 to 9 V

LCD

• Low power consumption.

• I2C-bus address: 011101 SA0.

2 APPLICATIONS

• Telecom equipment

• Portable instruments

• Point-of-sale terminals.

3 GENERAL DESCRIPTION

but does not contain the high voltage generator of that

device.

The PCF2104x is optimized for chip-on-glass applications.

The ‘x’ in ‘PCF2104x’ represents a specific letter code for

a character set in the character generator ROM (CGROM).

Two standard character sets are currently available,

specified by the letters ‘C’ and ‘L’ (see Figs 5 and 6).

Other character sets are available on request.

The PCF2104x is a low-power CMOS LCD controller and

driver, designed to drive a split screen dot matrix LCD

display of 1 or 2 lines by 24 characters or 2 or 4 lines by

12 characters with a 5 × 8 dot format. All necessary

functions for the display are provided in a single chip,

including on-chip generation of LCD bias voltages which

results in a minimum of external components and lower

system power consumption. To allow partial V

shutdown

DD

the ESD protection system of the SCL and SDA pins does

not use a diode connected to VDD.

The chip contains a character generator and displays

alphanumeric and kana characters. The PCF2104x

interfaces to most microcontrollers via a 4 or 8-bit bus, or

via the 2-wire I2C-bus.

3.1 Packages

• PCF2104xU/2; chip with bumps in tray

• PCF2104xU/7; chip with bumps on tape.

For further details see Chapter 18.

3.2 Available types

• PCF2104CU/x: character set ‘C’ in CGROM

• PCF2104LU/x: character set ‘L’ in CGROM

• PCF2104NU/x: character set ‘N’ in CGROM.

The PCF2104x integrated circuit is similar to the

PCF2114x (described in the

“PCF2116 family”

data sheet)

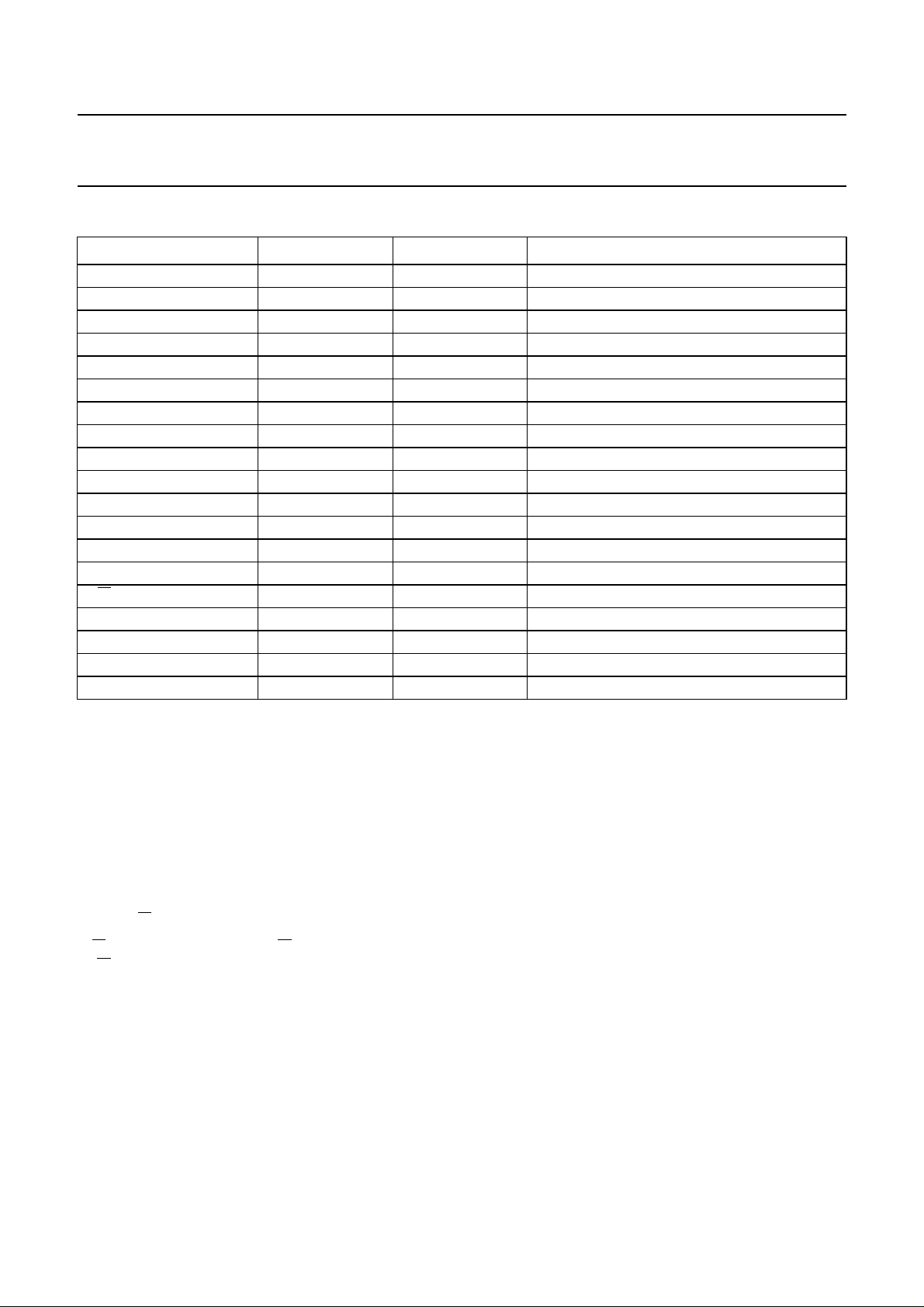

4 ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

PCF2104CU/2 − chip with bumps in tray −

PCF2104CU/7 − chip with bumps on tape −

PCF2104LU/2 − chip with bumps in tray −

PCF2104LU/7 − chip with bumps on tape −

PCF2104NU/2 − chip with bumps in tray −

PCF2104NU/7 − chip with bumps on tape −

1997 Dec 16 3

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

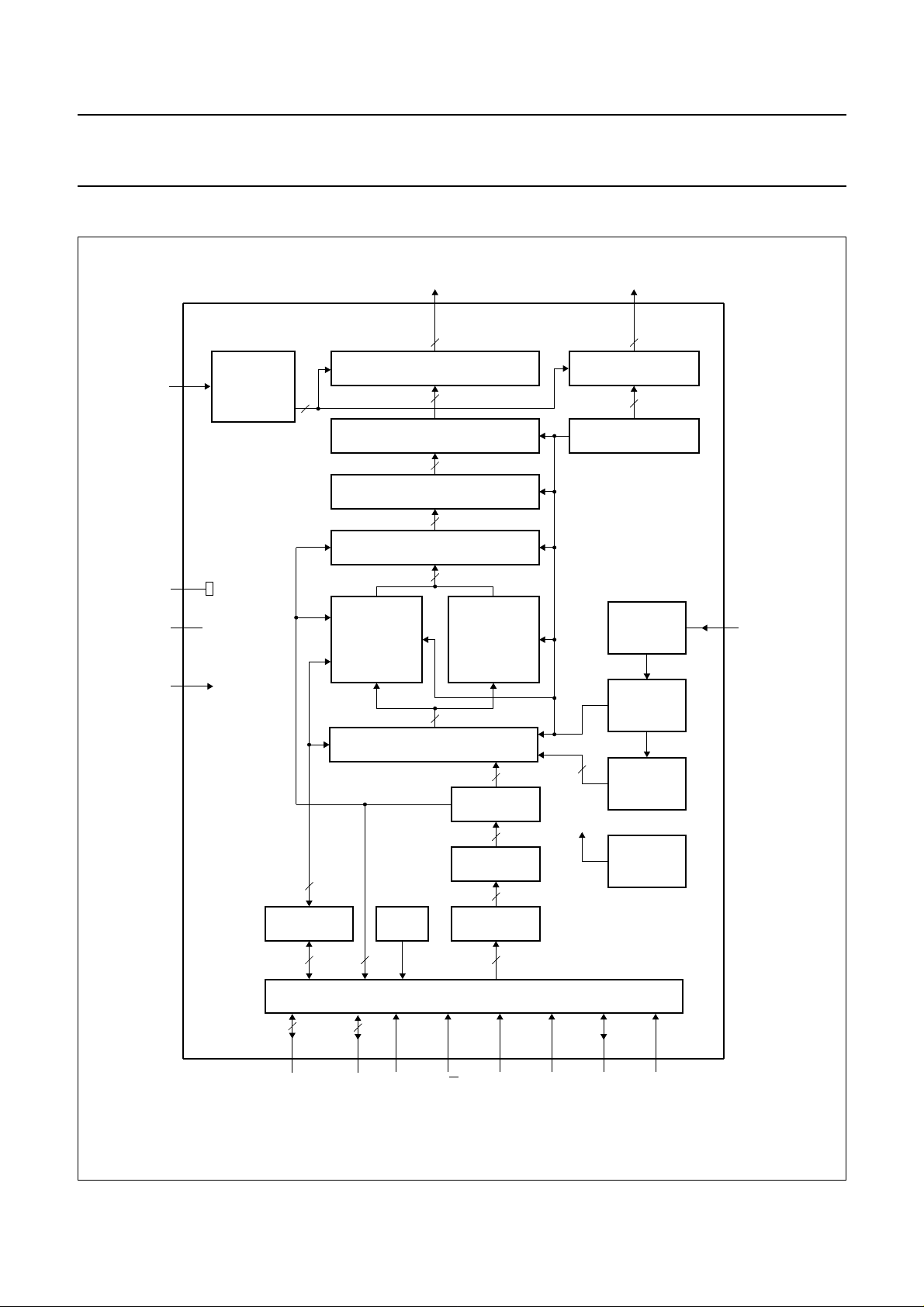

5 BLOCK DIAGRAM

handbook, full pagewidth

V

LCD

V

DD

V

SS

T1

111

2

4

101

BIAS

VOLTAGE

GENERATOR

REGISTER (DR)

6

DATA

COLUMN DRIVERS

DATA LATCHES

SHIFT REGISTER

CURSOR + DATA CONTROL

CHARACTER

GENERATOR

RAM

(CGRAM)

16

CHARACTERS

DISPLAY DATA RAM

(DDRAM) 80 CHARACTERS

8

BUSY

FLAG

C1 to C60

80-21

60

60

60

5 x 12-bit

5

5

8

CHARACTER

GENERATOR

ROM

(CGROM)

240

CHARACTERS

7

ADDRESS

COUNTER (AC)

7

INSTRUCTION

DECODER

8

INSTRUCTION

REGISTER (IR)

R1 to R32

5-20

81-96

32

ROW DRIVERS

32

SHIFT REGISTER

32-BIT

PCF2104x

OSCILLATOR

TIMING

GENERATOR

7

DISPLAY

ADDRESS

COUNTER

POWER - ON

RESET

1

OSC

78 8

4

109-106

DB0 to DB3 DB4 to DB7 E

105-102

4

98 100 99

R/W

Fig.1 Block diagram.

1997 Dec 16 4

I/O BUFFER

RS

SCL

97

110

MGC627

SDA3SA0

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

6 PINNING

SYMBOL FFC PAD TYPE DESCRIPTION

OSC 1 I oscillator/external clock input

V

DD

SA0 3 I I

V

SS

R8 to R5 5 to 8 O LCD row driver outputs

R32 to R29 9 to12 O LCD row driver outputs

R24 to R17 13 to 20 O LCD row driver outputs

C60 to C1 21 to 80 O LCD column driver outputs

R9 to R16 81 to 88 O LCD row driver outputs

R25 to R28 89 to 92 O LCD row driver outputs

R1 to R4 93 to 96 O LCD row driver outputs

SCL 97 I I

E 98 I data bus clock input

RS 99 I register select input

W 100 I read/write input

R/

T1 101 I test pad input

DB7 to DB0 102 to 109 I/O 8-bit bidirectional data bus input/output

SDA 110 I/O I

V

LCD

2 P logic supply voltage

2

C-bus address pin input

4 P ground

2

C-bus serial clock input

2

C-bus serial data input/output

111 I LCD supply voltage input

7 PIN FUNCTIONS

7.1 RS: register select (parallel control)

RS selects the register to be accessed for read and write

when the device is controlled by the parallel interface.

RS = logic 0 selects the instruction register for write and

the Busy Flag and Address Counter for read. RS = logic 1

selects the data register for both read and write. There is

an internal pull-up on pin RS.

7.2 R/

W: read/write (parallel control)

R/W selects either the read (R/W = logic 1) or write

(R/W = logic 0) operation when control is by the parallel

interface. There is an internal pull-up on this pin.

7.3 E: data bus clock (parallel control)

The E pin is set HIGH to signal the start of a read or write

operation when the device is controlled by the parallel

interface. Data is clocked in or out of the chip on the

negative edge of the clock. Note that this pin must be tied

to logic 0 (V

) when I2C-bus control is used.

SS

7.4 DB0 to DB7: data bus (parallel control)

The bidirectional, 3-state data bus transfers data between

the system controller and the PCF2104x. DB7 may be

used as the Busy Flag, signalling that internal operations

are not yet completed. In 4-bit operations the 4 higher

order lines DB4 to DB7 are used; DB0 to DB3 must be left

open circuit. There is an internal pull-up on each of the

data lines. Note that these pins must be left open circuit

2

when I

C-bus control is used.

7.5 C1 to C60: column driver outputs

These pins output the data for pairs of columns.

This arrangement permits optimized chip-on-glass (COG)

layout for 4-line by 12 characters.

7.6 R1 to R32: row driver outputs

These pins output the row select waveforms to the left and

right halves of the display.

7.7 V

: LCD power supply

LCD

Negative power supply for the liquid crystal display.

1997 Dec 16 5

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

7.8 OSC: oscillator

When the on-chip oscillator is used, this pin must be

connected to VDD. An external clock signal, if used, is input

at this pin.

7.9 SCL: serial clock line

Input for the I

2

C-bus clock signal.

7.10 SDA: serial data line

Input/output for the I

2

C-bus data line.

7.11 SA0: address pin

The hardware sub-address line is used to program the

device sub-address for 2 different PCF2104xs on the

2

same I

C-bus.

7.12 T1: test pad

Must be connected to V

. Not user accessible.

SS

8 FUNCTIONAL DESCRIPTION (see Fig.1)

8.1 LCD bias voltage generator

The intermediate bias voltages for the LCD display are

also generated on-chip. This removes the need for an

external resistive bias chain and significantly reduces the

system power consumption. The optimum levels depend

on the multiplex rate and are selected automatically when

the number of lines in the display is defined.

The optimum value of V

depends on the multiplex rate,

OP

the LCD threshold voltage (Vth) and the number of bias

levels. The relationships are given in Table 1.

Using a 5-level bias scheme for 1 : 16 MUX rate allows

VOP< 5 V for most LCD liquids. The effect on the display

contrast is negligible.

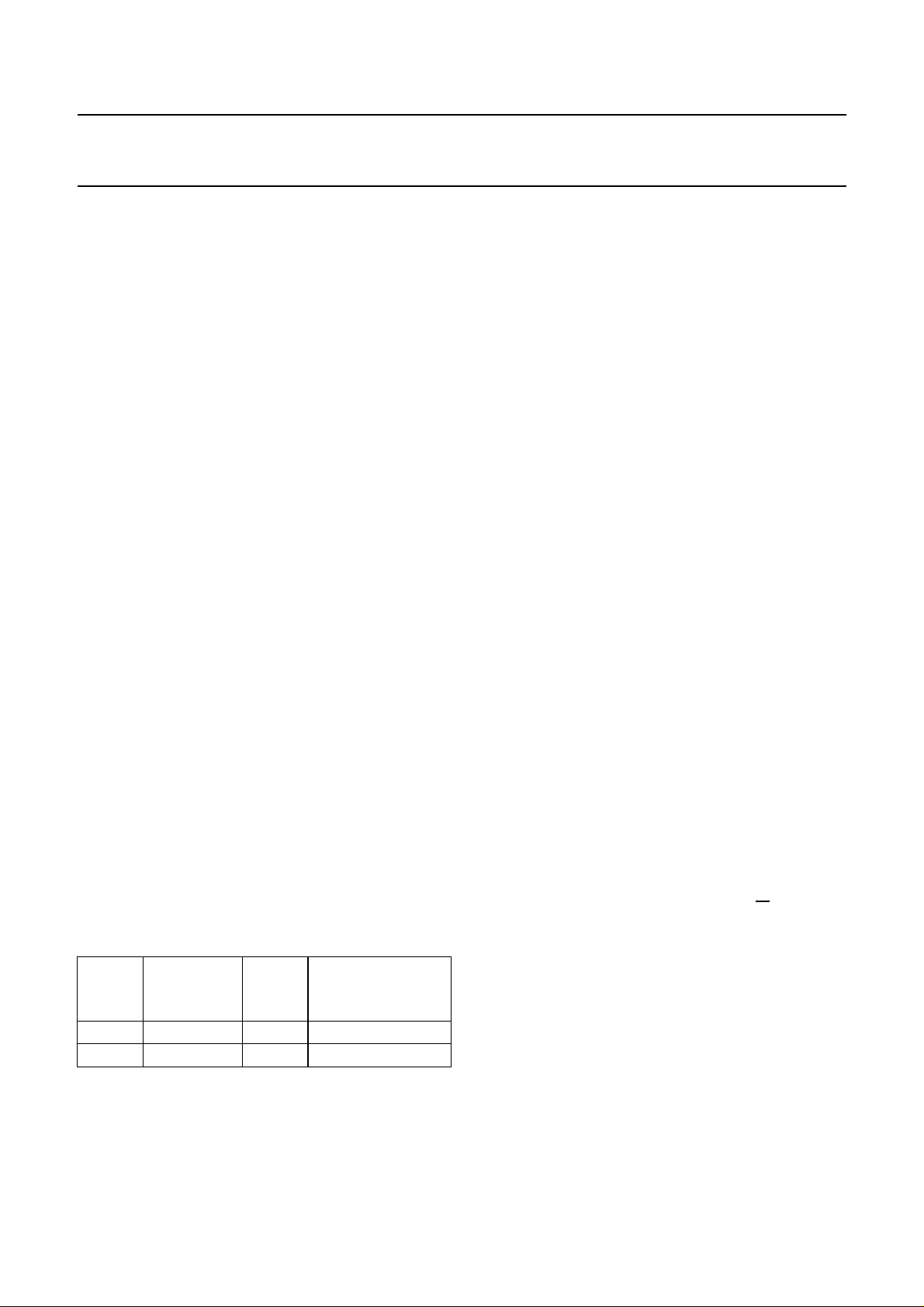

Table 1 Optimum values for V

MUX

RATE

NUMBER

OF BIAS

LEVELS

VOP/V

OP

DISCRIMINATION

th

Von/V

off

1 : 16 5 3.67 1.277

1 : 32 6 5.19 1.196

8.2 Oscillator

The on-chip oscillator provides the clock signal for the

display system. No external components are required.

Pin OSC must be connected to VDD.

8.3 External clock

If an external clock is to be used, it must be input at

pin OSC. The resulting display frame frequency is given by

f

frame

=1⁄

. A clock signal must always be present,

2304fosc

otherwise the LCD may be frozen in a DC state.

8.4 Power-on reset

The Power-on reset block initializes the chip after

power-on or power failure.

8.5 Registers

The PCF2104x has two 8-bit registers, an instruction

register (IR) and a data register (DR). The register select

signal (RS) determines which register will be accessed.

The instruction register stores instruction codes such as

display clear and cursor shift, and address information for

the Display Data RAM (DDRAM) and Character Generator

RAM (CGRAM). The instruction register can be written to,

but not read from, by the system controller.

The data register temporarily stores data to be read from

the DDRAM and CGRAM. When reading, data from the

DDRAM or CGRAM (corresponding to the address in the

Address Counter) is written to the data register prior to

being read by the ‘Read data’ instruction.

8.6 Busy Flag

The Busy Flag indicates the free/busy status of the

PCF2104x. Logic 1 indicates that the chip is busy and

further instructions will not be accepted. The Busy Flag is

output at pin DB7 when RS = logic 0 and R/

W = logic 1.

Instructions should only be written after checking that the

Busy Flag is at logic 0 or waiting for the required number

of clock cycles.

1997 Dec 16 6

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

8.7 Address Counter (AC)

The Address Counter assigns addresses to the DDRAM

and CGRAM for reading and writing and is set by the

instructions ‘Set CGRAM address’ and

‘Set DDRAM address’. After a read/write operation the

Address Counter is automatically incremented or

decremented by 1. The Address Counter contents are

output to the bus (DB0 to DB6) when RS = logic 0 and

R/W = logic 1.

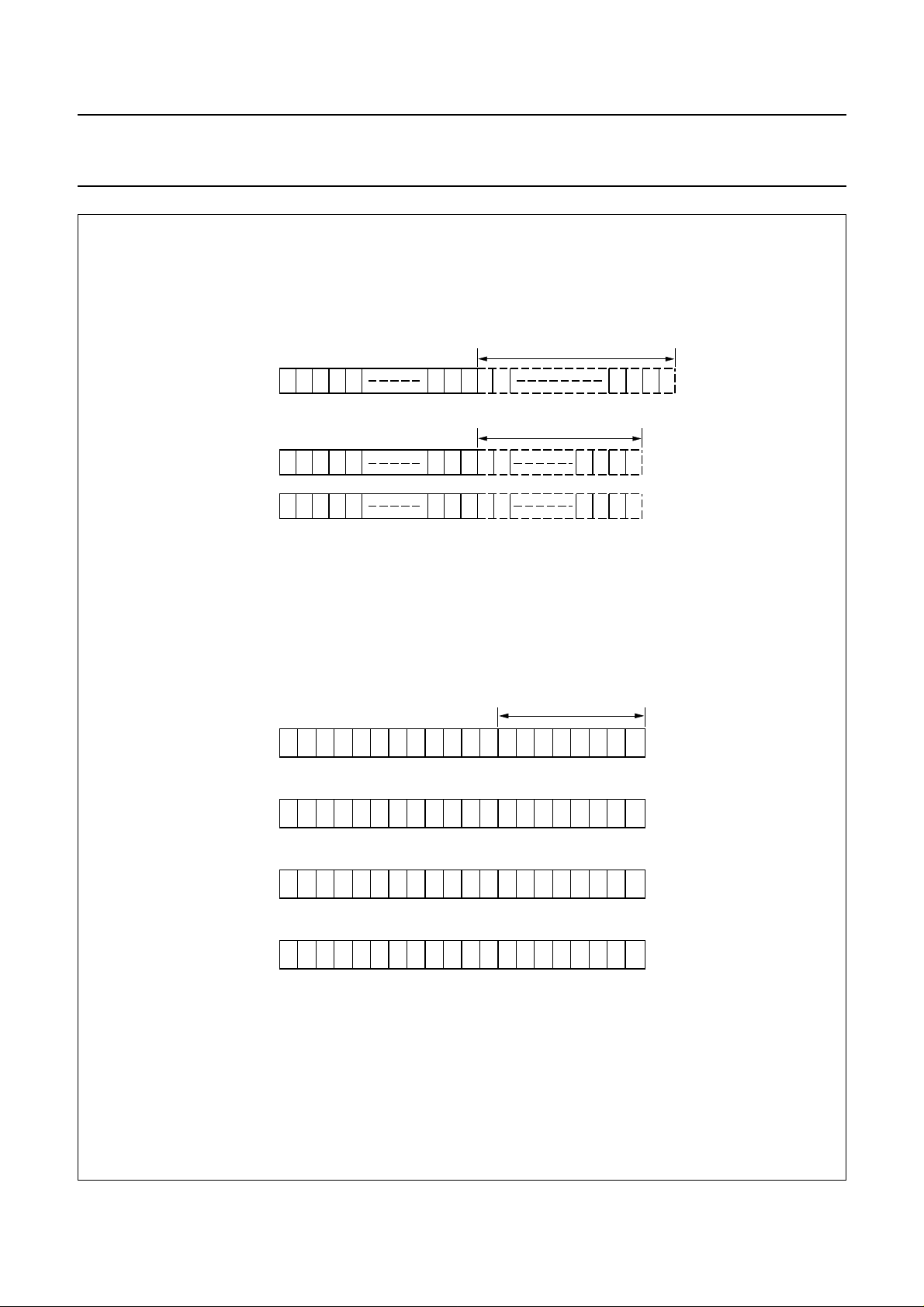

8.8 Display data RAM (DDRAM)

The DDRAM stores up to 80 characters of display data,

represented by 8-bit character codes. DDRAM locations

not used for storing display data can be used as general

purpose RAM. The basic DDRAM-to-display mapping

scheme is shown in Fig.2. With no display shift, the

characters represented by the codes in the first 12 or 24

RAM locations, starting at address 00 in line 1, are

displayed. Subsequent lines display data starting at

addresses 20, 40, or 60 Hex. Figures 3 and 4 show the

DDRAM-to-display mapping scheme when the display is

shifted.

The address range for a 1-line display is 00 to 4F; for a

2-line display from 00 to 27 (line 1) and 40 to 67 (line 2);

for a 4-line display from 00 to 13, 20 to 33, 40 to 53 and

60 to 73 for lines 1, 2, 3 and 4 respectively. For 2 and

4-line displays the end address of one line and the start

address of the next line are not consecutive. When the

display is shifted each line wraps around independently of

the others (see Figs 3 and 4).

When data is written to the DDRAM wrap-around occurs

from 4F to 00 in 1-line mode and from 27 to 40 and

67 to 00 in 2-line mode; from 13 to 20, 33 to 40, 53 to 60

and 73 to 00 in 4-line mode.

8.10 Character generator RAM (CGRAM)

Up to 16 user-defined characters may be stored in the

character generator RAM. The CGROM and CGRAM use

a common address space, of which the first column is

reserved for the CGRAM (see Fig.5). Figure 8 shows the

addressing principle for the CGRAM.

8.11 Cursor control circuit

The cursor control circuit generates the cursor (underline

and/or character blink as shown in Fig.9) at the DDRAM

address contained in the Address Counter. When the

Address Counter contains the CGRAM address the cursor

will be inhibited.

8.12 Timing generator

The timing generator produces the various signals

required to drive the internal circuitry. Internal chip

operation is not disturbed by operations on the data buses.

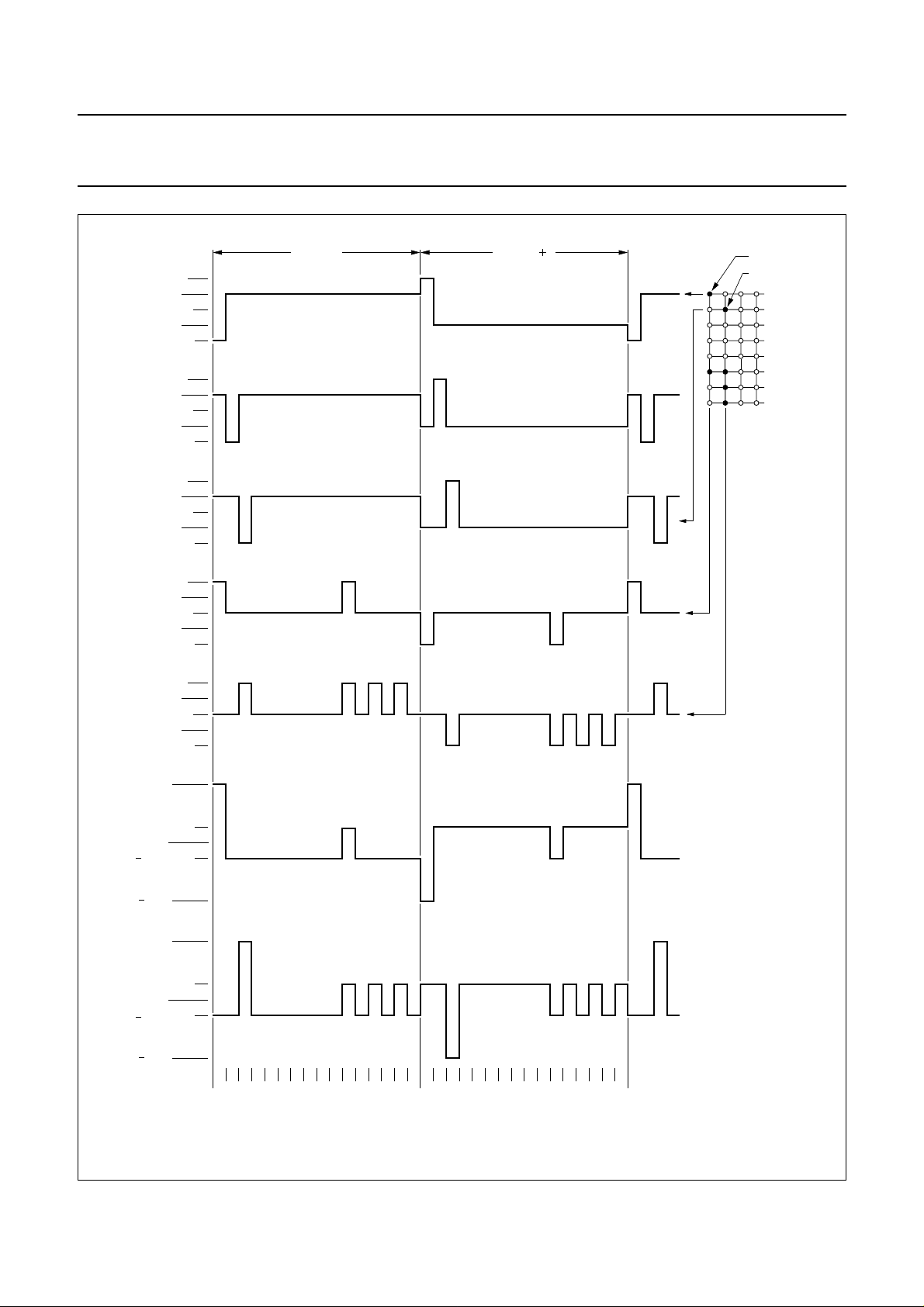

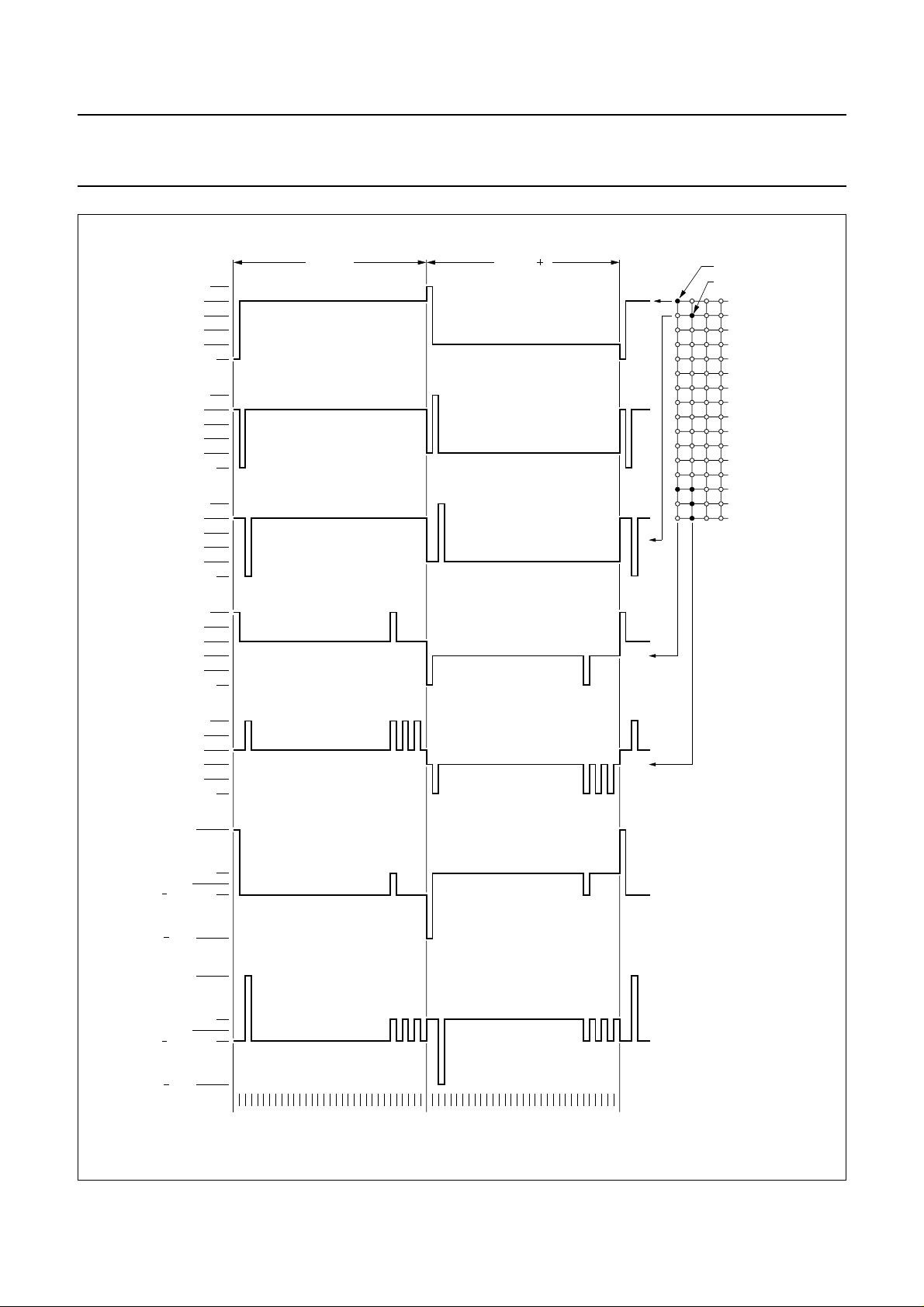

8.13 LCD row and column drivers

The PCF2104x contains 32 row and 60 column drivers,

which connect the appropriate LCD bias voltages in

sequence to the display, in accordance with the data to be

displayed. The bias voltages and the timing are selected

automatically when the number of lines in the display is

selected. Figures 10 and 11 show typical waveforms.

In the 1-line mode (1 : 16) the row outputs are driven in

pairs: R1/R17, R2/R18 for example. This allows the output

pairs to be connected in parallel, thereby providing greater

drive capability.

Unused outputs should be left unconnected.

8.9 Character generator ROM (CGROM)

The character generator ROM generates 240 character

patterns in 5 × 8 dot format from 8-bit character codes.

Figures 5 and 6 show the character sets currently

available.

1997 Dec 16 7

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

Display

handbook, 4 columns

Position

(decimal)

DDRAM

Address

(hex)

DDRAM

Address

(hex)

handbook, 4 columns

12345 222324

00 01 02 03 04 15 16 17 18 19 4C 4D 4E 4F

non-displayed DDRAM addresses

1-line display

non-displayed DDRAM address

00 01 02 03 04 15 16 17 18 19

2-line display

24 25 26 27

64 65 66 6740 41 42 43 44 55 56 57 58 59

MLA792

line 1

line 2

non-displayed DDRAM addresses

123456789101112

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13

line 1

20 21 22 23 24 25 26 27 28 29 2A 2B 2C 2D 2E 2F 30 31 32 33

DDRAM

Address

(hex)

40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53

60 61 62 63 64 65 66 67 68 69 6A 6B 6C 6D 6E 6F 70 71 72 73

4 line display

Fig.2 DDRAM-to-display mapping; no shift (PCF2104x).

1997 Dec 16 8

line 2

line 3

line 4

MLA793

Philips Semiconductors Product specification

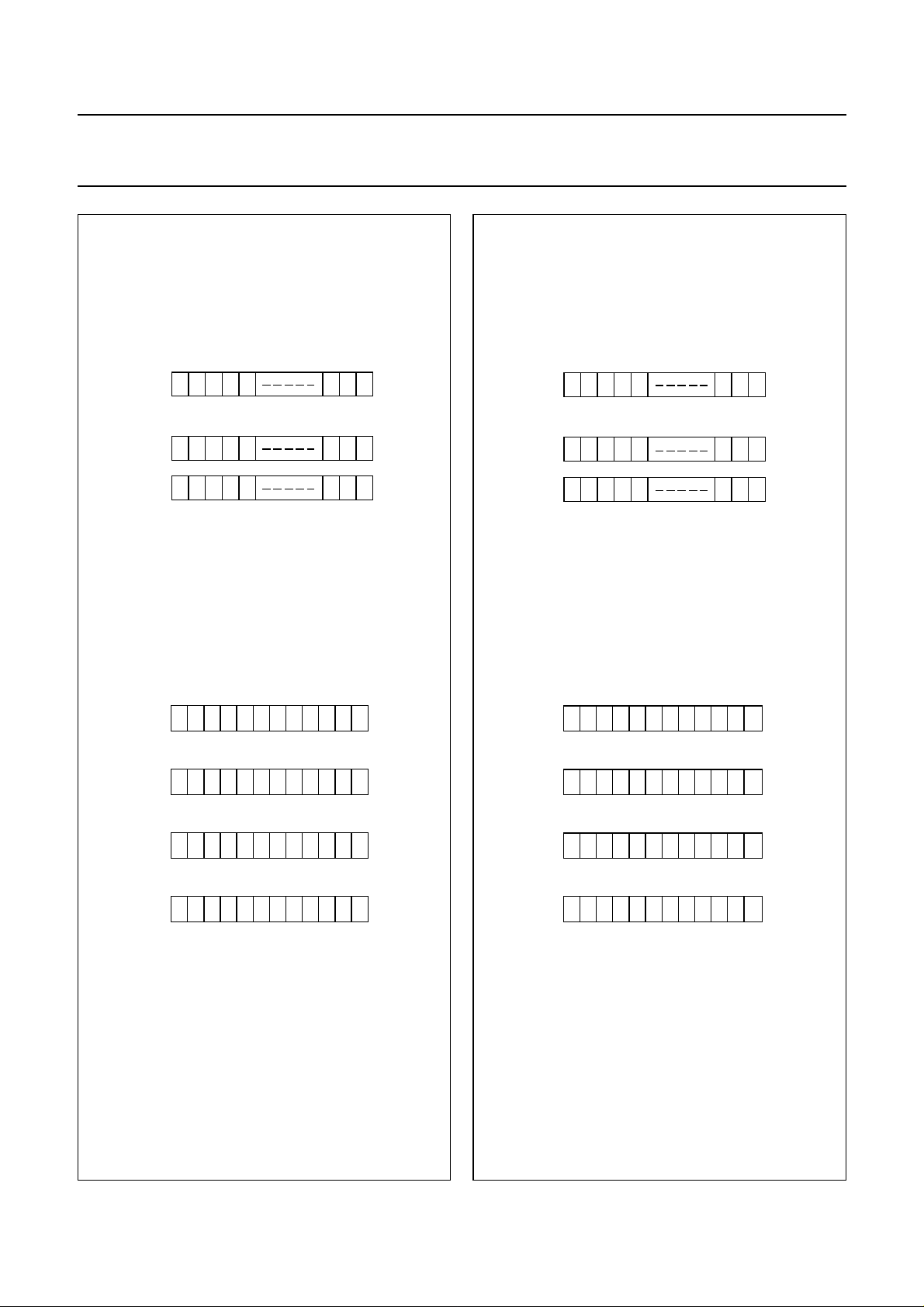

LCD controller/driver PCF2104x

Display

Position

(decimal)

DDRAM

Address

(hex)

DDRAM

Address

(hex)

DDRAM

Address

(hex)

1 2 3 4 5 22 23 24

4F 00 01 02 03 14 15 16

1-line display

27 00 01 02 03

67 40 41 42 43

2-line display

14 15 16

54 55 56

MLA802

123456789101112

13 01 02 03 04 05 06 07 08 09 0A

00

20 21 22 23 24 25 26 27 28 29 2A33

40 41 42 43 44 45 46 47 48 49 4A53

line 1

line 2

line 1

line 2

line 3

Display

Position

(decimal)

DDRAM

Address

(hex)

DDRAM

Address

(hex)

DDRAM

Address

(hex)

1 2 3 4 5 22 23 24

0501 02 03 04

16 17 18

1-line display

0501 02 03 04

41 42 43 44 45 56 57 58

2-line display

16 17 18

MLA815

123456789101112

01 02 03 04 05 06 07 08 09 0A 0B 0C

21 22 23 24 25 26 27 28 29 2A 2B 2C

41 42 43 44 45 46 47 48 49 4A 4B 4C

line 1

line 2

line 1

line 2

line 3

60 61 62 63 64 65 66 67 68 69 6A73

4-line display

MLA803

line 4

Fig.3 DDRAM-to-display mapping; right shift

(PCF2104x).

1997 Dec 16 9

61 62 63 64 65 66 67 68 69 6A 6B 6C

4-line display

MLA816

Fig.4 DDRAM-to-display mapping; left shift

(PCF2104x).

line 4

Philips Semiconductors Product specification

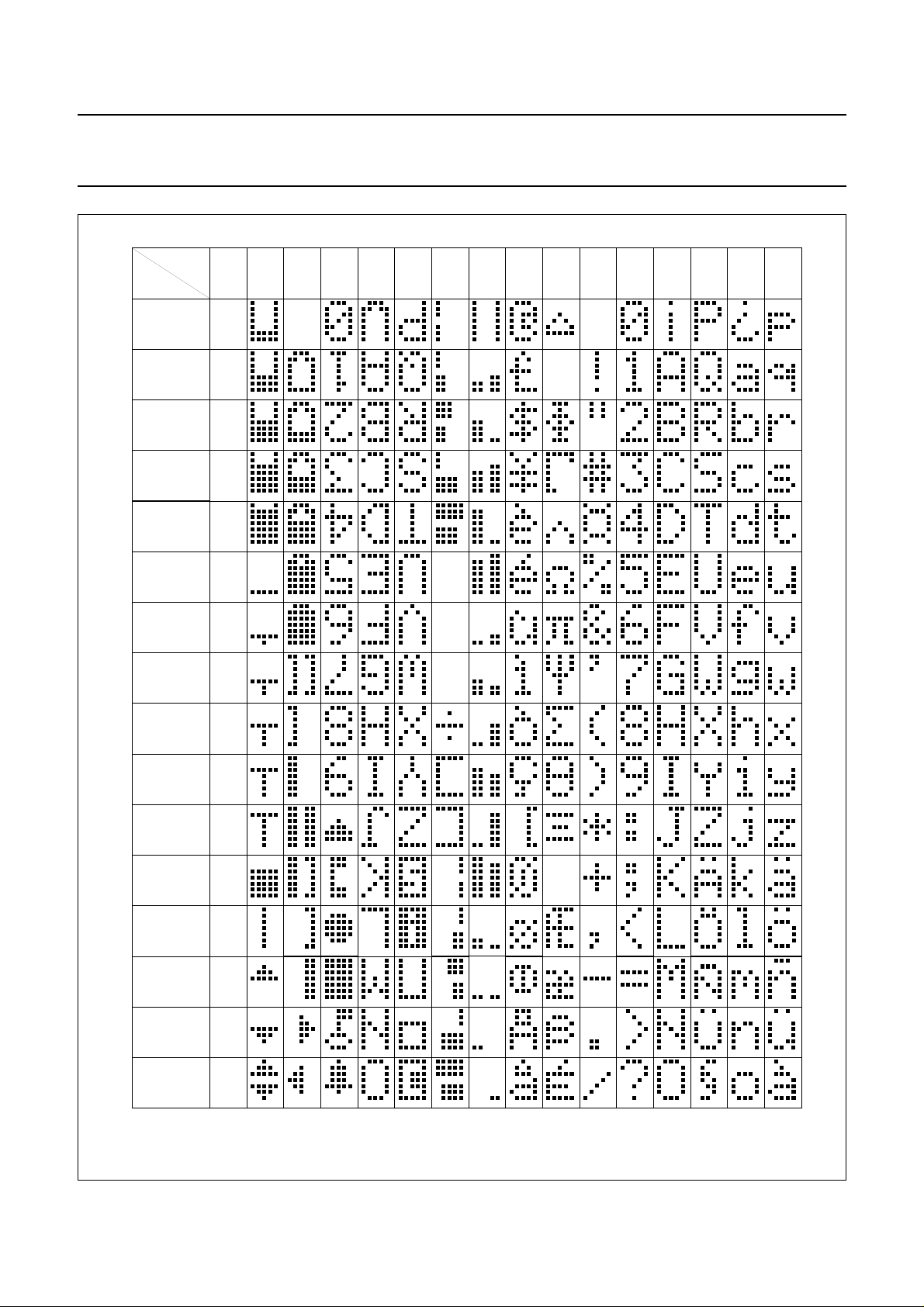

LCD controller/driver PCF2104x

handbook, full pagewidth

lower

4 bits

xxxx 0000

xxxx 0001

xxxx 0010

xxxx 0011

xxxx 0100

xxxx 0101

xxxx 0110

xxxx 0111

upper

4 bits

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

CG

RAM 1

2

3

4

5

6

7

8

xxxx 1000

xxxx 1001

xxxx 1010

xxxx 1011

xxxx 1100

xxxx 1101

xxxx 1110

xxxx 1111 16

9

10

11

12

13

14

15

MLB895

Fig.5 Character set ‘C’ in CGROM; PCF2104C.

1997 Dec 16 10

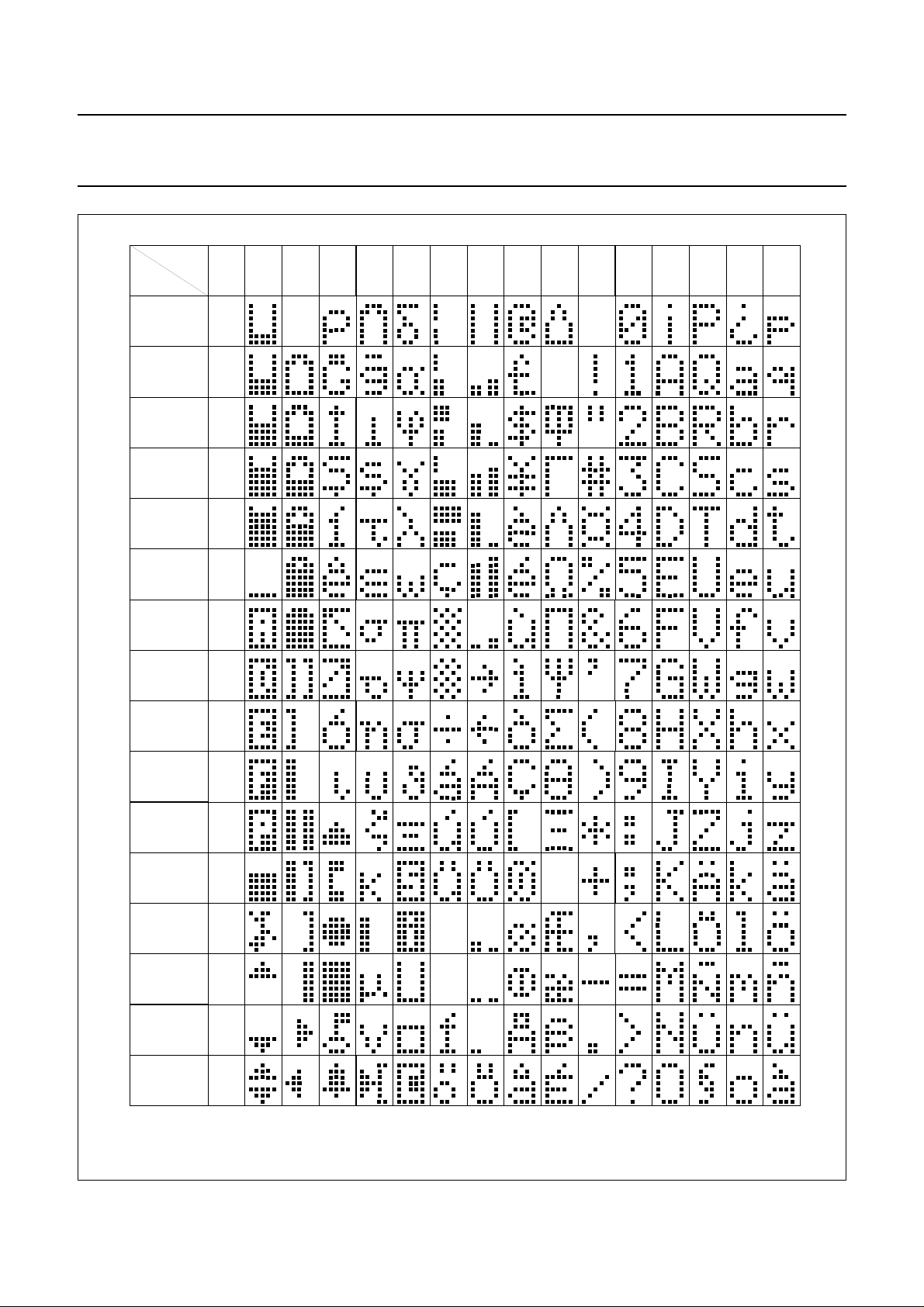

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

lower

6 bits

xxxx 0000

xxxx 0001

xxxx 0010

xxxx 0011

xxxx 0100

xxxx 0101

xxxx 0110

xxxx 0111

upper

4 bits

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

CG

RAM 1

2

3

4

5

6

7

8

xxxx 1000

xxxx 1001

xxxx 1010

xxxx 1011

xxxx 1100

xxxx 1101

xxxx 1110

xxxx 1111 16

9

10

11

12

13

14

15

MGC629

Fig.6 Character set ‘L’ in CGROM; PCF2104L.

1997 Dec 16 11

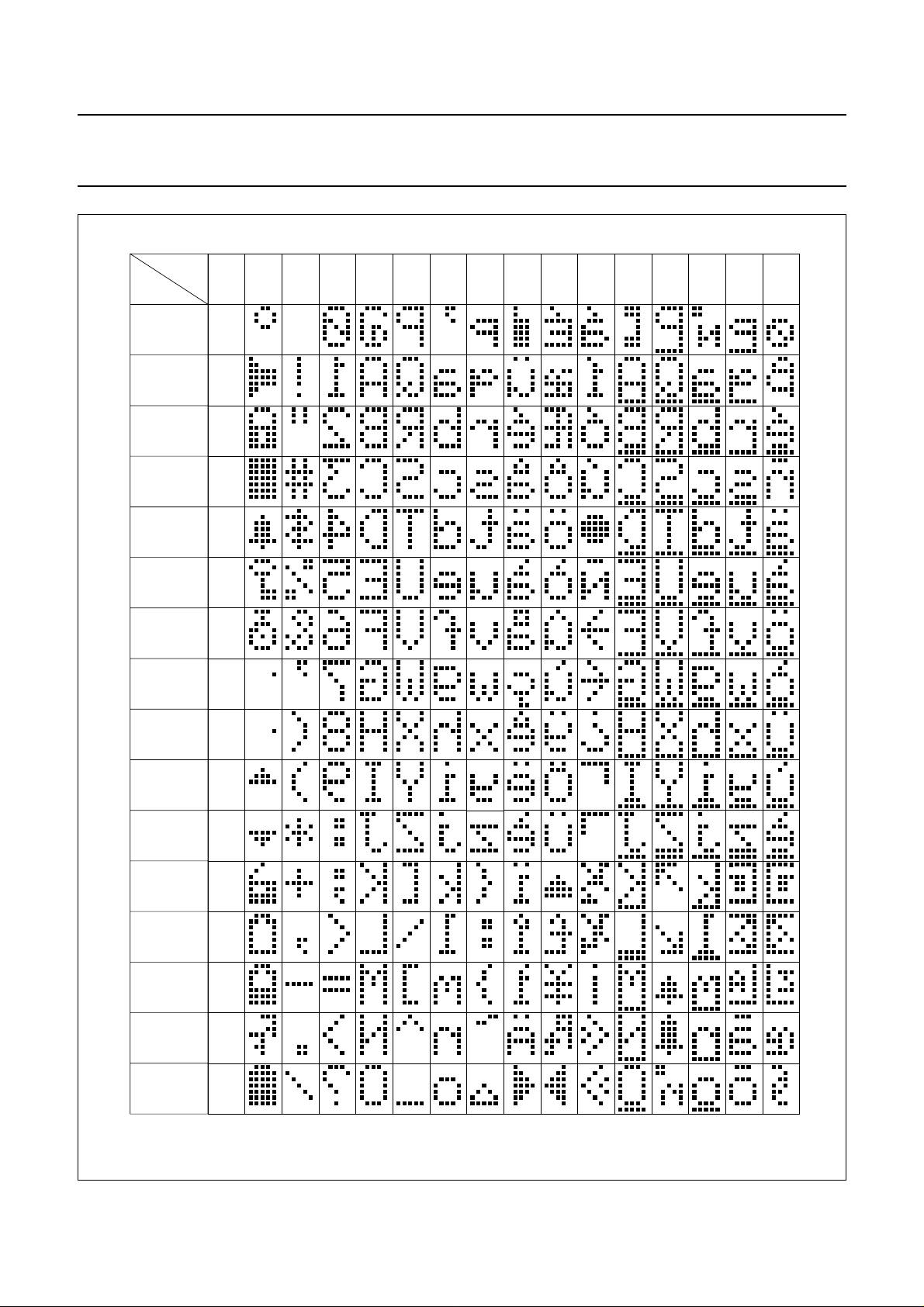

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

lower

4 bits

xxxx 0000

xxxx 0001

xxxx 0010

xxxx 0011

xxxx 0100

xxxx 0101

xxxx 0110

xxxx 0111

upper

4 bits

0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 11110000

CG

RAM 1

2

3

4

5

6

7

8

xxxx 1000

xxxx 1001

xxxx 1010

xxxx 1011

xxxx 1100

xxxx 1101

xxxx 1110 15

xxxx 1111 16

9

10

11

12

13

14

MGM134

Fig.7 Character set ‘N’ in CGROM; PCF2104N.

1997 Dec 16 12

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

76543210 6543210 43210

00000000 0000000 0

00000001 0001

00000010

00001111

00001111

00001111

00001111

character codes

(DDRAM data)

higher

order

bits

lower

order

bits

CGRAM

address

higher

order

bits

010 0000

1

1

1

1

1

1

1

1

1

111

1

1

lower

order

bits

001 000

010 000

011 0

100 0 00

101 00 0

110 000

111 00000

000 000

001 0 0 0

010

100

101 00 00

110 00 00

111 00000

001

1

100

1

101

1

110

1

1

higher

order

bits

character patterns

(CGRAM data)

lower

order

bits

00 00011

MGA800 - 1

character

pattern

example 1

cursor

position

character

pattern

example 2

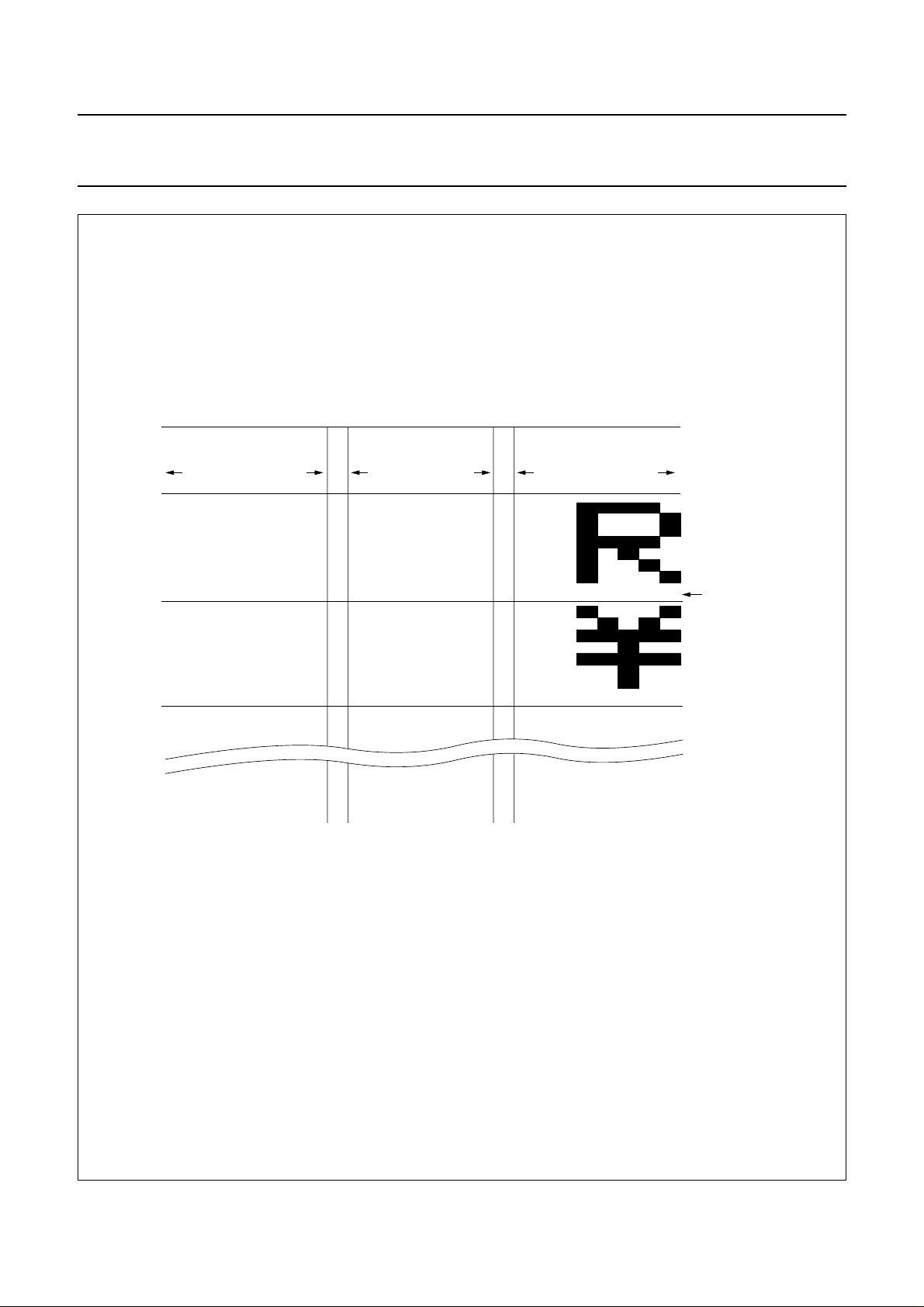

Character code bits 0to 3 correspond to CGRAM address bits 3 to 6.

CGRAM address bits 0 to 2 designate character pattern line position. The 8th line is the cursor position and display is performed by logical OR with the

cursor. Data in the 8

Character pattern column positions correspond to CGRAM data bits 0 to 4; bit 4 being at the left end, as shown in the figure.

CGRAM character patterns are selected when character code bits 4 to 7 are all logic 0. CGRAM data = logic 1 corresponds to selection for display.

Only bits 0 to 5 of the CGRAM address are set by the ‘Set CGRAM address’ instruction. Bit 6 can be set using the ‘Set DDRAM address’ instruction or

by using the auto-increment feature during CGRAM write. All bits 0 to 6 can be read using the ‘Read Busy Flag and address’ instruction.

th

line will appear in the cursor position.

Fig.8 Relationship between CGRAM addresses, data and display patterns.

1997 Dec 16 13

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

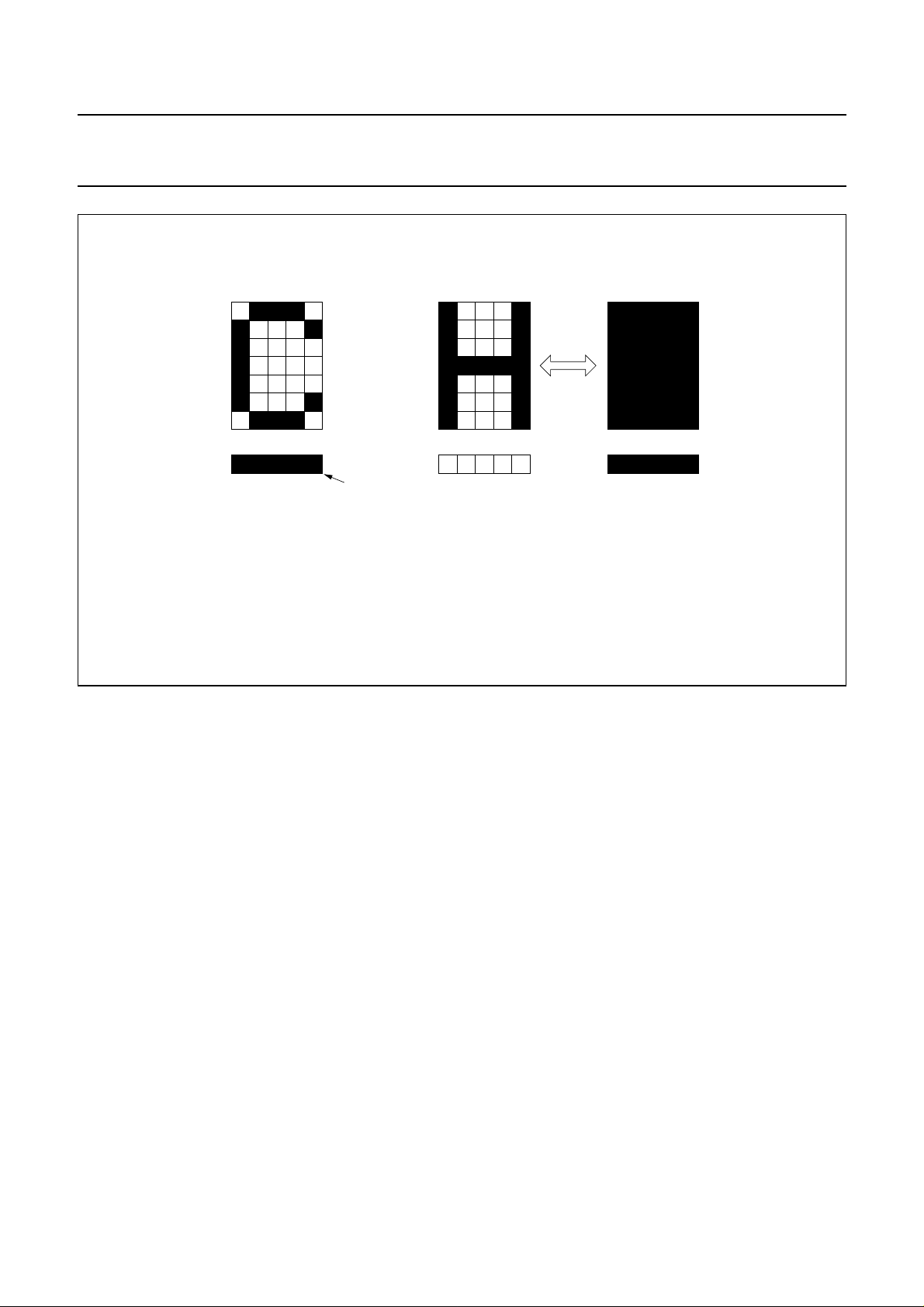

cursor

5 x 7 dot character font alternating display

cursor display example blink display example

Fig.9 Cursor and blink display examples.

MGA801

1997 Dec 16 14

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

V

DD

V

2

ROW 1

ROW 9

ROW 2

COL 1

COL 2

V /V

34

V

5

V

LCD

V

DD

V

2

V /V

34

V

5

V

LCD

V

DD

V

2

V /V

34

V

5

V

LCD

V

DD

V

2

V /V

34

V

5

V

LCD

V

DD

V

2

V /V

3

V

5

V

LCD

frame n 1frame n

4

state 1 (ON)

state 2 (ON)

1-line display

(1:16)

V

OP

0.25 V

OP

0 V

state 1

0.25 V

OP

V

OP

V

OP

0.25 V

0 V

0.25 V

V

OP

OP

OP

123 16123 16

state 2

Fig.10 Typical LCD waveforms; 1-line mode.

1997 Dec 16 15

MGA802 - 1

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

ROW 1

ROW 9

ROW 2

COL 1

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

frame n

frame n 1

state 1 (ON)

state 2 (ON)

2-line display

(1:32)

COL 2

state 1

state 2

V

V

V

V

V

V

V

OP

0.15 V

0 V

0.15 V

V

OP

V

OP

0.15 V

0 V

0.15 V

V

OP

DD

2

3

4

5

LCD

OP

OP

OP

OP

123 3212 3 32

Fig.11 Typical LCD waveforms; 2-line mode.

MGA803 - 1

1997 Dec 16 16

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

8.14 Programming of MUX 1 : 16 displays with

PCF2104x

The PCF2104x can be used in the following ways:

• 1-line mode to drive a 2-line display

• 2 × 12 characters with MUX rate 1 : 16, resulting in

better contrast. The internal data flow of the chip is

optimized for this purpose.

handbook, full pagewidth

display position

DDRAM address

display position

DDRAM address

1

00

13

0C

23

01 02

14 15

0D 0E

Fig.12 DDRAM-to-display mapping; no shift (PCF2104x).

4

03

16

0F

Using the ‘Function set’ instruction, M and N are set to 0, 0

(respectively). Figures 12, 13 and 14 show the DDRAM

addresses of the display characters. The second row of

each table corresponds to either the right half of a 1-line

display or to the second line of a 2-line display. Wrap

around of data during display shift or when writing data is

non-standard.

5

04

17

10

67

05 06

18 19

11 12

8

07

20

13

9

08

21

14

10 11

09 0A

22 23

15 16

12

0B

24

17

MLB899

handbook, full pagewidth

handbook, full pagewidth

display position

DDRAM address

display position

DDRAM address

Fig.13 DDRAM-to-display mapping; right shift (PCF2104x).

display position

DDRAM address

display position

DDRAM address

1

4F

13

0B

1

01

13

0D

23

00 01

14 15

0C 0D

23

02 03

14 15

0E 0F

4

02

16

0E

4

04

16

10

5

03

17

0F

5

05

17

11

67

04 05

18 19

10 11

67

06 07

18 19

12 13

8

06

20

12

8

08

20

14

9

07

21

13

9

09

21

15

10 11

08 09

22 23

14 15

10 11

0A 0B

22 23

16 17

12

0A

24

16

MLB900

12

0C

24

18

MLB901

Fig.14 DDRAM-to-display mapping; left shift (PCF2104x).

1997 Dec 16 17

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

8.15 Programming of MUX 1 : 32 displays with

PCF2104x

To drive a 2-line by 24 characters MUX 1 : 32 display, use

instruction ‘Function set’ to set M, N to 0, 1 (respectively).

To drive a 4-line by 12 characters MUX 1:32 display, use

instruction ‘Function set’ to set M, N to 1, 1 (respectively).

8.16 Reset function

The PCF2104 automatically initializes (resets) when

power is turned on. The state after reset is given in

Table 2.

Table 2 State after reset

STEP DESCRIPTION

1 Display clear.

2 Function set:

DL = 1: 8-bit interface

M, N = 0 1-line display

G = 0: not used

3 Display on/off control:

D = 0: display off

C = 0: cursor off;

B = 0: blink off;

4 Entry mode set:

I/D = 1: +1 (increment)

G = 0: not used

5 Default address pointer to DDRAM. The Busy

Flag (BF) indicates the busy state (BF = logic 1)

until initialization ends. The busy state lasts

2 ms. The chip may also be initialized by

software. See Tables 10 and 11.

2

6I

C-bus interface reset.

9 INSTRUCTIONS

Only two PCF2104x registers, the instruction register (IR)

and the data register (DR) can be directly controlled by the

microcontroller. Before internal operation, control

information is stored temporarily in these registers to allow

interface to various types of microcontrollers which

operate at different speeds or to allow interfacing to

peripheral control ICs.

The PCF2104x operation is controlled by the instructions

shown in Table 3 together with their execution time.

Details are explained in subsequent sections.

Instructions are of 4 categories, those that:

1. Designate PCF2104x functions such as display

format, data length, etc.

2. Set internal RAM addresses

3. Perform data transfer with internal RAM

4. Others.

In normal use, category 3 instructions are used most

frequently. However, automatic incrementing by 1

(or decrementing by 1) of internal RAM addresses after

each data write lessens the microcontroller program load.

The display shift in particular can be performed

concurrently with display data write, thus enabling the

designer to develop systems in minimum time with

maximum programming efficiency.

During internal operation, no instruction other than the

Busy Flag/address read instruction will be executed.

Because the Busy Flag is set to logic 1 while an instruction

is being executed, it is advisable to ensure that the flag it

is at logic 0 before sending the next instruction or wait for

the maximum instruction execution time, as given in

Table 3. An instruction sent while the Busy Flag is HIGH

will not be executed.

1997 Dec 16 18

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

(2)

CLOCK

CYCLES

REQUIRED

165

3

address 0 in Address Counter.

3

Also returns shifted display to original position

DDRAM contents remain unchanged.

3

3

3

of display. These operations are performed

during data write and read.

and blink of cursor position character (B).

changing DDRAM contents.

display lines (N, M) and voltage generator

Sets CGRAM address. 3

control (G).

0

Sets DDRAM address. 3

Reads Busy Flag (BF) indicating internal

operation is being performed and reads

Address Counter contents.

Table 3 Instructions (note 1)

W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 DESCRIPTION

INSTRUCTION RS R/

NOP 0000000000No operation. 0

Clear display 0 000000001Clears entire display and sets DDRAM

Return home 0 000000010Sets DDRAM address 0 in Address Counter

Entry mode set 0 0000001I/DSSets cursor move direction and specifies shift

Display control 0 000001DCBSets entire display on/off (D), cursor on/of f (C)

CG

C

DD

001 A

0001 A

Cursor/display shift 0 00001S/CR/L00Moves cursor and shifts display without

Function set 0 0001DLNMG0Sets interface data length (DL), number of

Set CGRAM

address

0 1 BF A

Set DDRAM

address

Read busy flag and

address

6.67 µs==

1

osc

f

---------

cy

T

= 150 kHz, ; 3 cycles = 20 µs, 165 cycles = 1.1 ms.

osc

C-bus mode the DL bit is don't care. 8-bit mode is assumed.

C-bus mode a control byte is required when RS or R/W is changed; control byte: Co, RS, R/W, 0, 0, 0, 0, 0; command byte: DB7 to DB0.

2

2

In the I

Read data 1 1 read data Reads data from CGRAM or DDRAM. 3

Write data 1 0 write data Writes data to CGRAM or DDRAM. 3

Notes

1. In the I

2. Example: f

1997 Dec 16 19

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

Table 4 Command bit identities

BIT LOGIC 0 LOGIC 1

I/D decrement increment

S display freeze display shift

D display off display on

C cursor off cursor on

B character at cursor position does not blink character at cursor position blinks

S/C cursor move display shift

R/L left shift right shift

DL 4 bits 8 bits

N (M = 0) 2 line × 12 characters; MUX 1 : 16 2 lines × 24 characters; MUX 1 : 32

N (M = 1) reserved 4 lines × 12 characters; MUX 1 : 32

BF end of internal operation internal operation in progress

Co last control byte, only data bytes to follow next two bytes are a data byte and another control byte

RS

R/W

E

DB7

DB6

DB5

DB4

IR7 IR3 BF AC3 DR7 DR3

IR6 IR2 AC6 AC2 DR6 DR2

IR5 IR1 AC5 AC1 DR5 DR1

IR4 IR0 AC4 AC0 DR4 DR0

instruction

write

busy flag and

address counter read

data register

read

Fig.15 4-bit transfer example.

MGA804

1997 Dec 16 20

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

RS

R/W

E

internal

DB7

IR7, IR3: instruction 7th bit, 3rd bit.

AC3: Address Counter 3rd bit.

RS

R/W

internal operation

IR7 IR3 AC3 D7 D3

instruction

write

busy

busy flag

AC3

check

not

busy

busy flag

check

instruction

write

Fig.16 An example of 4-bit data transfer timing sequence.

MGA805

E

internal

DB7

data busy busy

instruction

write

internal operation

busy flag

check

Fig.17 Example of Busy Flag check timing sequence.

1997 Dec 16 21

busy flag

check

not

busy

busy flag

check

data

instruction

write

MGA806

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

9.1 Clear display

‘Clear display’ writes space code 20 (hexadecimal) into all

DDRAM addresses (the character pattern for character

code 20 must be a blank pattern), sets the DDRAM

Address Counter to logic 0 and returns the display to its

original position if it was shifted. Consequently, the display

disappears and the cursor or blink position goes to the left

edge of the display (the first line if 2 or 4 lines are

displayed) and sets the entry mode to I/D = logic 1

(increment mode). S of entry mode does not change.

The instruction ‘Clear display’ requires extra execution

time. This may be allowed for by checking the Busy Flag

(BF) or by waiting until 2 ms has elapsed. The latter must

be applied where no read-back options are foreseen, as in

some chip-on-glass (COG) applications.

9.2 Return home

‘Return home’ sets the DDRAM Address Counter to

logic 0 and returns the display to its original position if it

was shifted. DDRAM contents do not change. The cursor

or blink position goes to the left of the display (the first line

if 2 or 4 lines are displayed). I/D and S of entry mode do

not change.

9.3 Entry mode set

9.3.1 I/D

When I/D = logic 1 (0) the DDRAM or CGRAM address

increments (decrements) by 1 when data is written to or

read from the DDRAM or CGRAM. The cursor or blink

position moves to the right when incremented and to the

left when decremented. The cursor and blink are inhibited

when the CGRAM is accessed.

9.3.2 S

When S = logic 1, the entire display shifts either to the right

(I/D = logic 0) or to the left (I/D = logic 1) during a DDRAM

write. Consequently, it looks as if the cursor stands still and

the display moves. The display does not shift when

reading from the DDRAM, or when writing to or reading

from the CGRAM. When S = logic 0 the display does not

shift.

9.4 Display on/off control

9.4.1 D

The display is on when D = logic 1 and off when

D = logic 0. Display data in the DDRAM is not affected and

can be displayed immediately by setting D to logic 1.

9.4.2 C

The cursor is displayed when C = logic 1 and inhibited

when C = logic 0. Even if the cursor disappears, the

display functions I/D, etc. remain in operation during

display data write. The cursor is displayed using 5 dots in

the 8th line (see Fig.9).

9.4.3 B

The character indicated by the cursor blinks when

B = logic 1. The blink is displayed by switching between

display characters and all dots on with a period of

1 second when f

frequencies the blink period is equal to 150 kHz/f

= 150 kHz (see Fig.9). At other clock

osc

osc

.

The cursor and the blink can be set to display

simultaneously.

9.5 Cursor/display shift

‘Cursor/display shift’ moves the cursor position or the

display to the right or left without writing or reading display

data. This function is used to correct a character or move

the cursor through the display. In 2 or 4-line displays, the

cursor moves to the next line when it passes the last

position of the line (40 or 20 decimal). When the displayed

data is shifted repeatedly all lines shift at the same time;

displayed characters do not shift into the next line.

The Address Counter (AC) content does not change if the

only action performed is shift display, but increments or

decrements with the cursor shift.

9.6 Function set

9.6.1 DL (

PARALLEL MODE ONLY)

Sets interface data width. Data is sent or received in bytes

(DB7 to DB0) when DL = logic 1 or in two nibbles

(DB7 to DB4) when DL = logic 0. When 4-bit width is

selected, data is transmitted in two cycles using the

parallel bus

(1)

.

Function set from I2C-bus interface: DL bit can not bet set

to logic 0 from the I2C-bus interface. If bit DL has been set

to logic 0 via the parallel bus, programming via the I2C-bus

interface is complicated.

9.6.2 N, M

Sets number of display lines.

(1) In a 4-bit application DB3 to DB0 are left open (internal

pull-ups). Hence in the first function set instruction after

power-on G and H are set to 1. A second function set must

then be sent (2 nibbles) to set G and H to their required

values.

1997 Dec 16 22

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

9.7 Set CGRAM address

‘Set CGRAM address’ sets bits 0 to 5 of the CGRAM

address (ACG in Table 3) into the Address Counter

(binary A[5] to A[0]). Data can then be written to or read

from the CGRAM.

Only bits 0 to 5 of the CGRAM address are set by the

‘Set CGRAM address’ instruction. Bit 6 can be set using

the ‘Set DDRAM address’ instruction or by using the

auto-increment feature during CGRAM write. All bits 0 to 6

can be read using the ‘Read busy flag and address’

instruction.

9.8 Set DDRAM address

Set DDRAM address sets the DDRAM address (A

Table 3) into the Address Counter (binary A[6] to A[0).

Data can then be written to or read from the DDRAM.

Table 5 Hexadecimal address ranges

ADDRESS FUNCTION

00 to 4F 1-line by 24

00 to 0B and 0C to 4F 2-line by 12

00 to 27 and 40 to 67 2-line by 24

00 to 13, 20 to 33, 40 to 53

and 60 to 73

9.9 Read busy flag and address

‘Read busy flag and address’ reads the Busy Flag (BF).

When BF = logic 1 it indicates that an internal operation is

in progress. The next instruction will not be executed until

BF = logic 0, so BF should be checked before sending

another instruction.

At the same time, the value of the Address Counter

expressed in binary A[6] to A[0] is read out. The Address

Counter is used by both CGRAM and DDRAM and its

value is determined by the previous instruction.

9.10 Write data to CGRAM or DDRAM

Writes binary 8-bit data D[7] to D[0] to the CGRAM or the

DDRAM.

4-line by 12

DD

in

9.11 Read data from CGRAM or DDRAM

Reads binary 8-bit data D[7] to D[0] from the CGRAM or

DDRAM.

The most recent ‘Set address’ instruction determines

whether the CGRAM or DDRAM is to be read.

The ‘Read data’ instruction gates the content of the data

register (DR) to the bus while E = HIGH. After E goes

LOW again, internal operation increments (or decrements)

the AC and stores RAM data corresponding to the new AC

into the DR.

Remark: the only three instructions that update the data

register (DR) are:

• ‘Set CGRAM address’

• ‘Set DDRAM address’

• ‘Read data’ from CGRAM or DDRAM.

Other instructions (e.g. ‘Write data, ‘Cursor/display shift’,

‘Clear display’, ‘Return home’) will not modify the data

register content.

10 INTERFACE TO MICROCONTROLLER

(PARALLEL INTERFACE)

The PCF2104x can send data in either two 4-bit operations

or one 8-bit operation and can thus interface to 4-bit or

8-bit microcontrollers.

In the 8-bit mode data is transferred as 8-bit bytes using

the 8 data lines DB0 to DB7. Three further control lines E,

RS, and R/

In the 4-bit mode data is transferred in two cycles of 4-bits

each. The higher order bits (corresponding to DB4 to DB7

in 8-bit mode) are sent in the first cycle and the lower order

bits (DB0 to DB3 in 8-bit mode) in the second cycle.

Data transfer is complete after two 4-bit data transfers.

It should be noted that two cycles are also required for the

Busy Flag check. 4-bit operation is selected by instruction.

See Figs 15, 16 and 17 for examples of bus protocol.

In the 4-bit mode pins DB3 to DB0 must be left

open-circuit. They are pulled up to VDD internally.

W are required.

Whether the CGRAM or DDRAM is to be written to is

determined by the previous specification of CGRAM or

DDRAM address setting. After writing, the address

automatically increments or decrements by 1, in

accordance with the entry mode. Only bits D0 to D4 of

CGRAM data are valid, bits D5 to D7 are ‘don't care’.

1997 Dec 16 23

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

11 INTERFACE TO MICROCONTROLLER

2

C-BUS INTERFACE)

(I

2

11.1 Characteristics of the I

C-bus

The I2C-bus is for bidirectional, two-line communication

between different ICs or modules. The two lines are a

serial data line (SDA) and a serial clock line (SCL).

Both lines must be connected to a positive supply via a

pull-up resistor. Data transfer may be initiated only when

the bus is not busy.

11.2 Bit transfer

One data bit is transferred during each clock pulse.

The data on the SDA line must remain stable during the

HIGH period of the clock pulse as changes in the data line

at this time will be interpreted as a control signal.

11.3 Start and stop conditions

Both data and clock lines remain HIGH when the bus is not

busy. A HIGH-to-LOW transition of the data line, while the

clock is HIGH is defined as the START condition (S).

A LOW-to-HIGH transition of the data line while the clock

is HIGH is defined as the STOP condition (P).

11.4 System configuration

A device generating a message is a ‘transmitter’, a device

receiving a message is the ‘receiver’. The device that

controls the message is the ‘master’ and the devices which

are controlled by the master are the ‘slaves’.

11.5 Acknowledge

The number of data bytes transferred between the start

and stop conditions from transmitter to receiver is

unlimited. Each byte of eight bits is followed by an

acknowledge bit. The acknowledge bit is a HIGH level

signal put on the bus by the transmitter during which time

the master generates an extra acknowledge related clock

pulse. A slave receiver which is addressed must generate

an acknowledge after the reception of each byte. Also a

master receiver must generate an acknowledge after the

reception of each byte that has been clocked out of the

slave transmitter. The device that acknowledges must

pull-down the SDA line during the acknowledge clock

pulse, so that the SDA line is stable LOW during the HIGH

period of the acknowledge related clock pulse (set-up and

hold times must be taken into consideration). A master

receiver must signal an end of data to the transmitter by

not generating an acknowledge on the last byte that has

been clocked out of the slave. In this event the transmitter

must leave the data line HIGH to enable the master to

generate a stop condition.

11.6 I

2

C-bus protocol

Before any data is transmitted on the I2C-bus, the device

which should respond is addressed first. The addressing is

always carried out with the first byte transmitted after the

start procedure. The I2C-bus configuration for the different

PCF2104x READ and WRITE cycles is illustrated in

Figs 22, 23 and 24.

handbook, full pagewidth

SDA

SCL

data line

stable;

data valid

Fig.18 Bit transfer.

1997 Dec 16 24

change

of data

allowed

MBC621

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

SDA

SDA

SDA

SCL

SCL

MASTER

TRANSMITTER/

RECEIVER

S

START condition

Fig.19 Definition of START and STOP conditions.

SLAVE

RECEIVER

SLAVE

TRANSMITTER/

RECEIVER

STOP condition

MASTER

TRANSMITTER

P

TRANSMITTER/

SCL

MBC622

MASTER

RECEIVER

MGA807

Fig.20 System configuration.

handbook, full pagewidth

DATA OUTPUT

BY TRANSMITTER

DATA OUTPUT

BY RECEIVER

SCL FROM

MASTER

S

START

condition

Fig.21 Acknowledgement on the I2C-bus.

1997 Dec 16 25

not acknowledge

acknowledge

acknowledgement

9821

clock pulse for

MBC602

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

P

update

data pointer

n 0 bytes1 byte

from PCF2104x

acknowledgement

S

CONTROL BYTE A

0

CONTROL BYTE A DATA A DATA A

1

0

A

011101 0A

S

Co

2n 0 bytes

Co

R/W

slave address

MGC617

0

S

A

011101 0

R/W

PCF2104x

slave address

handbook, full pagewidth

Fig.22 Master transmits to slave receiver; WRITE mode.

1997 Dec 16 26

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

A

(1)

DATA

P

MGC618

from PCF2104x

acknowledgement

S

A

1 1 CONTROL

0

A

DATA

A

CONTROL BYTE

1

0A

A

0

2 bytes2n 0 bytes

Co

Co

R/W

from master

no acknowledgement

from PCF2104x

acknowledgement

S

SLAVE

DATA

1A DATA A 1

0

A

ADDRESS

S

n bytes last byte

R/W

update

data pointer

handbook, full pagewidth

Fig.23 Master reads after setting word address; write word address, set RS/RW; READ data.

slave address

011101

S

1997 Dec 16 27

(1) Last data byte is a dummy byte (may be omitted).

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

Fig.24 Master reads slave immediately after first byte; READ mode (RS previously defined).

S

SLAVE

ADDRESS

acknowledgement

from PCF2104x

S

A

1A DATA A 1

0

R/W

n bytes

acknowledgement

from master

DATA

last byte

update

data pointer

no acknowledgement

from master

P

MGC619

1997 Dec 16 28

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

SU;STO

t

(P)

STOP

CONDITION

MGA811 - 1

.

IH

(A)

ACKNOWLEDGE

LSB

R/W

BIT 0

(A6)

BIT 6

(A7)

MSB

BIT 7

(S)

START

CONDITION

r

t

LOW

t

BUF

t

f

t

HD;STA

t

t/f

SCL

HIGH

t

and V

IL

handbook, full pagewidth

C-bus timing diagram; rise and fall times refer to V

2

Fig.25 I

PROTOCOL

SDA

1997 Dec 16 29

SCL

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

12 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER MIN. MAX. UNIT

V

V

V

V

I

I

I

O

I

DD

P

P

T

DD

LCD

I

O

, ISS, I

tot

O

stg

supply voltage −0.5 +8.0 V

LCD supply voltage VDD− 11 V

DD

input voltage OSC, RS, R/W, E and DB0 to DB7 VSS− 0.5 VDD+ 0.5 V

output voltage R1 to R32, C1 to C60 and V

LCD

V

− 0.5 VDD+ 0.5 V

LCD

DC input current −10 +10 mA

DC output current −10 +10 mA

LCDVDD

, VSS or V

current −50 +50 mA

LCD

total power dissipation − 400 mW

power dissipation per output − 100 mW

storage temperature −65 +150 °C

V

13 HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is

desirable to take normal precautions appropriate to handling MOS devices (see

“Handling MOS Devices”

).

14 DC CHARACTERISTICS

= 2.5 to 6 V; VSS=0V;V

V

DD

LCD=VDD

− 3.5 to VDD− 9V;T

= −40 to +85 °C; unless otherwise specified.

amb

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DD

V

LCD

I

DD

I

DD1

I

DD2

I

DD3

I

LCD

V

POR

supply voltage 2.5 − 6.0 V

LCD supply voltage VDD− 9 − VDD− 3.5 V

supply current external V

LCD

note 1 −−−

supply current 1 − 200 500 µA

supply current 2 VDD=5V; VOP=9V;

f

= 150 kHz;

osc

T

=25°C

amb

supply current 3 VDD=3V; VOP=5V;

f

= 150 kHz;

osc

T

=25°C

amb

V

input current notes 1 and 6 − 50 100 µA

LCD

− 200 300 µA

− 150 200 µA

Power-on reset voltage level note 2 − 1.3 1.8 V

1997 Dec 16 30

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Logic

V

IL1

V

IH1

V

IL(osc)

V

IH(osc)

I

pu

I

OL(DB)

I

OH(DB)

I

L1

2

I

C-bus

LOW level input voltage pins E, RS,

R/W, DB0 to DB7 and SA0

HIGH level input voltage pins E, RS,

R/W, DB0 to DB7 and SA0

LOW level input voltage pin OSC V

HIGH level input voltage pin OSC VDD− 0.1 − V

pull-up current at pins DB0 to DB7,

RS and R/

W

LOW level output current pins

V

I=VSS

VOL= 0.4 V; VDD=5V 1.6 −− mA

DB0 to DB7

HIGH level output current pins

VOH=4V; VDD=5V −1.0 −− mA

DB0 to DB7

leakage current pins OSC, E, RS,

VI=VDD or V

SS

R/W, DB0 to DB7 and SA0

V

SS

0.7V

SS

DD

− 0.3V

− V

DD

DD

− VDD− 1.5 V

DD

V

V

V

0.04 0.15 1.00 µA

−1 − +1 µA

SDA, SCL

V

IL2

V

IH2

I

L2

C

i

I

OL(SDA)

LOW level input voltage note 3 V

SS

HIGH level input voltage note 3 0.7V

leakage current VI=VDD or V

SS

−1 − +1 µA

DD

− 0.3V

− V

DD

DD

V

V

input capacitance note 4 −−7pF

LOW level output current (SDA) VOL= 0.4 V; VDD=5V 3 −− mA

LCD outputs

R

ROW

row output resistance pins

note 5 − 1.5 3 kΩ

R1 to R32

R

COL

column output resistance pins

note 5 − 36 kΩ

C1 to C60

V

tol1

bias voltage tolerance pins

note 6 −±20 ±130 mV

R1 to R32 and C1 to C60

Notes

1. LCD outputs are open-circuit; inputs at VDD or VSS; V0=VDD; bus inactive; internal or external clock with duty cycle

50% (I

2. Resets all logic when VDD<V

DD1

only).

POR

.

3. When the voltages are above or below the supply voltages VDD or VSS, an input current may flow; this current must

not exceed ±0.5 mA.

4. Tested on sample basis.

5. Resistance of output terminals (R1 to R32 and C1 to C60) with load current I

= 150 µA; VOP=VDD− V

load

LCD

=9V;

outputs measured one at a time.

6. LCD outputs open-circuit.

1997 Dec 16 31

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

15 AC CHARACTERISTICS

V

= 2.5 to 6.0 V; VSS=0V; V

DD

LCD=VDD

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

f

f

FR

osc

LCD frame frequency (internal clock) note 1 40 65 100 Hz

external clock frequency 90 150 225 kHz

Bus timing characteristics: Parallel Interface; notes 1 and 2

W

RITE OPERATION (WRITING DATA FROM MICROCONTROLLER TO PCF2104X)

T

cy

PW

t

ASU

t

AH

t

DSW

t

HD

EH

enable cycle time 500 −−ns

enable pulse width 220 −−ns

address set-up time 50 −−ns

address hold time 25 −−ns

data set-up time 60 −−ns

data hold time 25 −−ns

READ OPERATION (READING DATA FROM PCF2104X TO MICROCONTROLLER)

T

cy

PW

EH

t

ASU

t

AH

t

DHD

t

HD

Timing characteristics: I

f

SCL

t

SW

t

BUF

t

SU;STA

t

HD;STA

t

LOW

t

HIGH

t

r

t

f

t

SU;DAT

t

HD;DAT

t

SU;STO

enable cycle time 500 −−ns

enable pulse width 220 −−ns

address set-up time 50 −−ns

address hold time 25 −−ns

data delay time −−150 ns

data hold time 20 − 100 ns

2

C-bus interface; note 2

SCL clock frequency −−100 kHz

tolerable spike width on bus −−100 ns

bus free time 4.7 −−µs

set-up time for a repeated START condition 4.7 −−µs

start condition hold time 4 −−µs

SCL LOW time 4.7 −−µs

SCL HIGH time 4 −−µs

SCL and SDA rise time −−1µs

SCL and SDA fall time −−0.3 µs

data set-up time 250 −−ns

data hold time 0 −−ns

set-up time for STOP condition 4 −−µs

− 3.5VtoVDD− 9V;T

= −40 °Cto+85°C; unless otherwise specified.

amb

Notes

1. V

= 5.0 V.

DD

2. All timing values are valid within the operating supply voltage and ambient temperature range and are referenced to

VIL and VIH with an input voltage swing of VSSto VDD.

1997 Dec 16 32

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

16 TIMING DIAGRAMS

handbook, full pagewidth

Fig.26 Parallel bus write operation sequence; writing data from microcontroller to PCF2104x.

RS

R/W

DB0 to DB7

V

IH1

V

IL1

t

AS

V

IL1

PW

EH

V

E

IH1

V

IL1

V

V

V

IH1

V

t

DSW

IH1

IL1

IL1

V

IH1

V

IL1

Valid Data

T

cy

t

t

AH

AH

t

V

IL1

V

IL1

H

V

IH1

V

IL1

MLA798 - 1

handbook, full pagewidth

RS

R/W

E

DB0 to DB7

V

IH1

V

IL1

t

AS

V

IH1

PW

EH

V

V

IL1

IH1

t

Fig.27 Parallel bus read operation sequence; reading data from PCF2104x to microcontroller.

1997 Dec 16 33

V

DDR

V

OH1

V

OL1

IH1

V

IH1

V

IL1

t

AH

V

IH1

t

AH

V

IL1

t

DHR

V

OH1

V

OL1

T

cy

V

IL1

MLA799 - 1

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

17 APPLICATION INFORMATION

handbook, 4 columns

Fig.28 Direct connection to 8-bit microcontroller; 8-bit bus.

handbook, 4 columns

P80CL51

P10 to P17

P80CL51

P14 to P17

P20

P21

P22

P10

P11

P12

RS

R/W

R1 to R32

E

PCF2104x

8

RS

E

C1 to C60

DB0 to DB7

R1 to R32

R/W

MGC620

PCF2104x

4

C1 to C60

DB4 to DB7

32

to

LCD

60

32

to

LCD

60

handbook, full pagewidth

MGC621

Fig.29 Direct connection to 8-bit microcontroller; 4-bit bus.

V

LCD

V

V

DD

SS

100 nF

100

nF

V

LCD

V

DD

OSC

PCF2104x

V

SS

DB0 to DB7 E RS R/W

R7 to R16

R25 to R32

R1 to R8

R17 to R24

16

C1 to C60

2 x 24 CHARACTER

Fig.30 Typical application using parallel interface.

16

LCD DISPLAY

(SPLIT SCREEN)

60

MGC624

60

1997 Dec 16 34

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

handbook, full pagewidth

VDDV

DD

V

V

LCD

V

V

LCD

V

V

DD

SS

DD

SS

100 nF

100

nF

100 nF

100

nF

V

LCD

V

DD

OSC

PCF2104x

V

SS

V

LCD

V

DD

OSC

PCF2104x

V

SS

SA0

V

SA0

V

DD

SS

R1 to R16

R17 to R24

16

C1 to C60

R1 to R16

16

C1 to C60

16

2 x 24 CHARACTER

LCD DISPLAY

(SPLIT SCREEN)

60

2 x 12 CHARACTER

LCD DISPLAY

MGC625

60

60

SCL SDA

MASTER TRANSMITTER

PCF84C81

Fig.31 Application using I2C-bus interface.

1997 Dec 16 35

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

17.1 8-bit operation, 2 × 12 display using internal

reset

Table 7 shows an example of a 1-line display in 8-bit

operation. The PCF2104x functions must be set by the

function set instruction prior to display. Since the display

data RAM can store data for 80 characters, the RAM can

be used for advertising displays when combined with

display shift operation. Since the display shift operation

changes the display position only and DDRAM contents

remain unchanged. Display data entered first can be

displayed when the ‘Return home’ instruction is

performed.

17.2 4-bit operation, 2 × 12 display using internal

reset

The program must set functions prior to 4-bit operation.

Table 6 shows an example. When power is turned on, 8-bit

operation is automatically selected and the PCF2104x

attempts to perform the first write as an 8-bit operation.

Since nothing is connected to DB0 to DB3, a rewrite is

then required. However, since one operation is completed

in two accesses of 4-bit operation, a rewrite is required to

set the functions (see Table 6 step 3).

17.3 8-bit operation, 2 × 24 display

For a 2-line display, the cursor automatically moves from

the first to the second line after the 40th digit of the first line

has been written. Thus, if there are only 8 characters in the

first line, the DDRAM address must be set after the eighth

character is completed (see Table 8). It should be noted

that both lines of the display are always shifted together,

data does not shift from one line to the other.

17.4 I

A control byte is required with most instructions

(see Table 9).

17.5 Initializing by instruction

If the power supply conditions for correctly operating the

internal reset circuit are not met, the PCF2104x must be

initialized by instruction. Tables 10 and 11 show how this

may be performed for 8-bit and 4-bit operation.

2

C operation, 2 × 12 display

Thus, DB4 to DB7 of the function set are written twice.

1997 Dec 16 36

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

Table 6 4-bit operation, 1-line display example; using internal reset

STEP INSTRUCTION DISPLAY OPERATION

1 Power supply on (PCF2104x is

initialized by the internal reset circuit).

2 Function set:

RS = 0; R/

DB5 = 1; DB4 = 0

3 Function set:

RS = 0; R/W = 0; DB7 = 0; DB6 = 0;

DB5 = 1; DB4 = 0

RS = 0; R/

DB5 = 0; DB4 = 0

4 Display on/off control:

RS = 0; R/W = 0; DB7 = 0; DB6 = 0;

DB5 = 0; DB4 = 0

RS = 0; R/

DB5 = 1; DB4 = 0

5 Entry mode set:

RS = 0; R/W = 0; DB7 = 0; DB6 = 0;

DB5 = 0; DB4 = 0

RS = 0; R/

DB5 = 1; DB4 = 0

6 Write data to CGRAM/DDRAM:

RS = 1; R/W = 0; DB7 = 0; DB6 = 1;

DB5 = 0; DB4 = 1

RS = 1; R/

DB5 = 1; DB4 = 0

W = 0; DB7 = 0; DB6 = 0;

W = 0; DB7 = 0; DB6 = 0;

W = 0; DB7 = 1; DB6 = 1;

W = 0; DB7 = 0; DB6 = 1;

W = 0; DB7 = 0; DB6 = 1;

_ Sets mode to increment the address by 1 and to shift the

P_ Writes ‘P’. The DDRAM has already been selected by

Initialized. No display appears.

Sets to 4-bit operation. In this instance operation is

handled as 8-bits by initialization and only this

instruction completes with one write.

Sets to 4-bit operation, selects 2 × 12 display.

4-bit operation starts from this point and resetting is

needed.

Turns on display and cursor.

Entire display is blank after initialization.

cursor to the right at the time of write to the DD/CGRAM.

Display is not shifted.

initialization at power-on.

The cursor is incremented by 1 and shifted to the right.

1997 Dec 16 37

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

Sets to 8-bit operation, selects 2 × 12 display.

Initialized. No display appears.

W = 0; DB7 = 0; DB6 = 0; DB5 = 1; DB4 = 1;

initialization.

_ Turns on display and cursor. Entire display is blank after

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

cursor to the right at the time of the write to the

_ Sets mode to increment the address by 1 and to shift the

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

DD/CGRAM. Display is not shifted.

initialization at power-on. The cursor is incremented by 1

and shifted to the right.

|

|

P_ Writes ‘P’. The DDRAM has already been selected by

PH_ Writes ‘H’.

W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 1;

W = 0; DB7 = 0; DB6 = 1; DB5 = 1; DB4 = 1;

PHILIPS_ Writes ‘S’.

PHILIPS_ Sets mode for display shift at the time of write.

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

HILIPS _ Writes space.

ILIPS M_ Writes ‘M’.

W = 0; DB7 = 0; DB6 = 0; DB5 = 1; DB4 = 0;

|

|

W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0;

DB3 = 0; DB2 = 0; DB1 = 0; DB0 = 0

RS = 0; R/

DB3 = 1; DB2 = 1; DB1 = 1; DB0 = 0

RS = 0; R/

DB3 = 0; DB2 = 1; DB1 = 1; DB0 = 0

RS = 1; R/

DB3 = 0; DB2 = 0; DB1 = 0; DB0 = 0

reset function).

RS = 0; R/

1 Power supply on (PCF2104x is initialized by the internal

STEP INSTRUCTION DISPLAY OPERATION

Table 7 8-bit operation, 1-line display example; using internal reset (character set ‘A’)

1997 Dec 16 38

2 Function set:

3 Display mode on/off control:

4 Entry mode set:

5 Write data to CGRAM/DDRAM:

RS = 1; R/

6 Write data to CGRAM/DDRAM:

DB3 = 1; DB2 = 0; DB1 = 0; DB0 = 0

7 |

RS = 1; R/W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 1;

DB3 = 0; DB2 = 0; DB1 = 1; DB0 = 1

RS = 0; R/

8 Write data to CGRAM/DDRAM:

9 Entry mode set:

RS = 1; R/

DB3 = 0; DB2 = 1; DB1 = 1; DB0 = 1

DB3 = 0; DB2 = 0; DB1 = 0; DB0 = 0

RS = 1; R/

DB3 = 1; DB2 = 1; DB1 = 0; DB0 = 1

10 Write data to CGRAM/DDRAM:

11 Write data to CGRAM/DDRAM:

12 |

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

MICROKO Writes ‘O’.

MICROKO Shifts only the cursor position to the left.

MICROKO Shifts only the cursor position to the left.

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 1;

ICROCO Writes ‘C’ correction. The display moves to the left.

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 1;

MICROCO Shifts the display and cursor to the right.

W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0;

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 1;

MICROCO_ Shifts only the cursor to the right.

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 1;

ICROCOM_ Writes ‘M’.

W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0;

(address 0).

|

|

PHILIPS M Returns both display and cursor to the original position

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

RS = 1; R/W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0;

13 Write data to CGRAM/DDRAM:

STEP INSTRUCTION DISPLAY OPERATION

1997 Dec 16 39

RS = 0; R/

DB3 = 1; DB2 = 1; DB1 = 1; DB0 = 1

DB3 = 0; DB2 = 0; DB1 = 0; DB0 = 0

RS = 0; R/

14 Cursor or display shift:

15 Cursor or display shift:

RS = 1; R/

DB3 = 0; DB2 = 0; DB1 = 0; DB0 = 0

DB3 = 0; DB2 = 0; DB1 = 1; DB0 = 1

RS = 0; R/

DB3 = 1; DB2 = 1; DB1 = 0; DB0 = 0

16 Write data to CGRAM/DDRAM:

17 Cursor or display shift:

18 Cursor or display shift:

DB3 = 0; DB2 = 1; DB1 = 0; DB0 = 0

RS = 0; R/

RS = 1; R/

DB3 = 1; DB2 = 1; DB1 = 0; DB0 = 1

19 Write data to CGRAM/DDRAM:

20 |

RS = 0; R/

DB3 = 0; DB2 = 0; DB1 = 1; DB0 = 0

21 Return home:

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

Sets to 8-bit operation, selects 2 × 24 display

Initialized. No display appears.

W = 0; DB7 = 0; DB6 = 0; DB5 = 1; DB4 = 1;

initialization.

_ Turns on display and cursor. Entire display is blank after

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

cursor to the right at the time of write to the CG/DDRAM.

_ Sets mode to increment the address by 1 and to shift the

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

Display is not shifted.

initialization at power-on. The cursor is incremented by 1

and shifted to the right.

|

|

P_ Writes ‘P’. The DDRAM has already been selected by

W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 1;

PHILIPS_ Writes ‘S’.

the 2nd line.

PHILIPS Sets DDRAM address to position the cursor at the head of

_

PHILIPS Writes ‘M’.

M_

W = 0; DB7 = 1; DB6 = 1; DB5 = 0; DB4 = 0;

W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0;

|

|

PHILIPS Writes ‘O’.

MICROCO_

PHILIPS Sets mode for display shift at the time of write.

MICROCO_

W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0;

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

DB3 = 1; DB2 = 0; DB1 = 0; DB0 = 0

RS = 0; R/

DB3 = 1; DB2 = 1; DB1 = 1; DB0 = 0

RS = 0; R/

DB3 = 0; DB2 = 1; DB1 = 1; DB0 = 0

RS = 1; R/

reset function).

1 Power supply on (PCF2104x is initialized by the internal

STEP INSTRUCTION DISPLAY OPERATION

Table 8 8-bit operation, 2-line display example; using internal reset

1997 Dec 16 40

RS = 0; R/

2 Function set:

3 Display on/off control:

4 Entry mode set:

DB3 = 0; DB2 = 0; DB1 = 0; DB0 = 0

5 Write data to CGRAM/DDRAM:

6 |

RS = 1; R/W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 1;

DB3 = 0; DB2 = 0; DB1 = 1; DB0 = 1

RS = 0; R/

DB3 = 0; DB2 = 0; DB1 = 0; DB0 = 0

RS = 1; R/

DB3 = 1; DB2 = 1; DB1 = 0; DB0 = 1

7 Write data to CGRAM/DDRAM:

8 Set DDRAM address:

9 Write data to CGRAM/ DDRAM:

RS = 1; R/

DB3 = 1; DB2 = 1; DB1 = 1; DB0 = 1

RS = 0; R/

DB3 = 0; DB2 = 1; DB1 = 1; DB0 = 1

10 |

11 Write data to CGRAM/ DDRAM:

12 Write data to CGRAM/ DDRAM:

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

second lines shift together.

|

HILIPS Writes ‘M’. Display is shifted to the left. The first and

ICROCOM_

(address 0).

|

PHILIPS Returns both display and cursor to the original position

MICROCOM

W = 0; DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0;

RS = 1; R/W = 0; DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0;

DB3 = 1; DB2 = 1; DB1 = 0; DB0 = 1

13 Write data to CGRAM/ DDRAM:

STEP INSTRUCTION DISPLAY OPERATION

1997 Dec 16 41

14 |

RS = 0; R/

DB3 = 0; DB2 = 0; DB1 = 1; DB0 = 0

15 Return home:

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

; note 1)

SS

C-BUS BYTE DISPLAY OPERATION

2

During the acknowledge cycle SDA will be pulled-down by

the PCF2104x.

Selects 1-line display; SCL pulse during acknowledge

Control byte sets RS and R/W for following data bytes.

cycle starts execution of instruction.

character Hex 20 (blank in ASCII-like character sets).

_ Turns on display and cursor. Entire display shows

cursor to the right at the time of write to the DDRAM or

_ Sets mode to increment the address by 1 and to shift the

Therefore a control byte is needed.

CGRAM. Display is not shifted.

_

W = 0; Ack = 1

The cursor is incremented by 1 and shifted to the right.

|

|

|

_

P_ Writes ‘P’. The DDRAM has been selected at power-up.

PH_ Writes ‘H’.

PHILIPS_ Writes ‘S’.

W = 0; Ack = 1

C-bus operation; 1-line display (using internal reset, assuming SA0 = V

2

C-bus start Initialized. No display appears.

2

1I

W = 0; Ack = 1

SA6 = 0; SA5 = 1; SA4 = 1; SA3 = 1; SA2 = 0; SA1 = 1;

SA0 = 0; R/

Co = 0; RS = 0; R/

DB7 = 0; DB6 = 0; DB5 = 1; DB4 = X; DB3 = 0; DB2 = 0;

DB1 = 0; DB0 = 0; Ack = 1

2 Slave address for write:

3 Send a control byte for function set:

4 Function set:

DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0; DB3 = 1; DB2 = 1;

DB1 = 1; DB0 = 0; Ack = 1

5 Display on/off control:

C-bus start _ For writing data to DDRAM, RS must be set to 1.

2

DB7 = 0; DB6 = 0; DB5 = 0; DB4 = 0; DB3 = 0; DB2 = 1;

DB1 = 1; DB0 = 0; Ack = 1

6 Entry mode set:

7I

STEP I

Table 9 Example of I

1997 Dec 16 42

W = 0; Ack = 1

Co = 0; RS = 1; R/

DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 1; DB3 = 0; DB2 = 0;

SA6 = 0; SA5 = 1; SA4 = 1; SA3 = 1; SA2 = 0; SA1 = 1;

SA0 = 0; R/

8 Slave address for write:

9 Send a control byte for write data:

DB1 = 0; DB0 = 0; Ack = 1

10 Write data to DDRAM:

DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 0; DB3 = 1; DB2 = 0;

DB1 = 0; DB0 = 0; Ack = 1

11 Write data to DDRAM:

12 to 15 |

DB7 = 0; DB6 = 1; DB5 = 0; DB4 = 1; DB3 = 0; DB2 = 0;

DB1 = 1; DB0 = 1; Ack = 1

16 Write data to DDRAM:

Philips Semiconductors Product specification

LCD controller/driver PCF2104x

C-bus

2

C-bus

C-bus write

2

C-bus interface to be shifted out.

2

2

C-bus interface.

2

shifted display to original position. DDRAM contents

unchanged). This instruction does not update the Data

Register (DR).

PHILIPS_

PHILIPS_

C-bus start + slave address for write

C-BUS BYTE DISPLAY OPERATION

2

2

PHILIPS Sets DDRAM address 0 in Address Counter. (Also returns

W = 0; Ack = 1

C-bus stop) I

2

The R/W has to be set to 1 while still in I

mode.

PHILIPS DDRAM content will be read from following instructions.

In the previous instruction neither a ‘Set address’ nor a

‘Read data’ has been performed. Therefore the content of

loaded into the internal I

PHILIPS During the acknowledge cycle the content of the DR is

acknowledge cycle is shifted out over SDA. MSB is DB7.

During master acknowledge content of DDRAM

the DR was unknown.

address 01 is loaded into the I

ILIPS 8 × SCL; content loaded into interface during previous

PH

interface.

acknowledge code of ‘I’ is loaded into the I

LIPS 8 × SCL; code of letter ‘H’ is read first. During master

PHI

interface register is shifted out no internal action is

LIPS No master acknowledge; After the content of the I

PHI

W = 1; Ack = 1

W = 1; Ack = 1

performed. No new data is loaded to the interface register,

Data Register (DR) is not updated, Address Counter (AC)

is not incremented and cursor is not shifted.

C-bus start PHILIPS

2

Co = 0; RS = 1; R/

20 Control byte for read:

SA6 = 0; SA5 = 1; SA4 = 1; SA3 = 1; SA2 = 0; SA1 = 1;

SA0 = 0; R/

21 I

22 Slave address for read:

17 (optional I

STEP I

(as step 8)