Philips p80cl410, p83cl410 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

P80CL410; P83CL410

Low voltage 8-bit microcontrollers

with I

Product specification

Supersedes data of 1995 Jan 20

File under Integrated circuits, IC20

2

C-bus

1997 Apr 10

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

2.1 ROMless version: P80CL410

3 APPLICATIONS

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 FUNCTIONAL DIAGRAM

7 PINNING INFORMATION

7.1 Pinning

7.2 Pin description

8 FUNCTIONAL DESCRIPTION OVERVIEW

8.1 General

8.2 CPU timing

9 MEMORY ORGANIZATION

9.1 Program Memory

9.2 Data Memory

9.3 Special Function Registers (SFRs)

9.4 Addressing

10 I/O FACILITIES

10.1 Ports

10.2 Port options

10.3 Port 0 options

10.3.1 External memory accesses

10.3.2 I/O Accesses

10.4 SET/RESET options

11 TIMERS/EVENT COUNTERS

12 REDUCED POWER MODES

12.1 Idle mode

12.2 Power-down mode

12.3 Wake-up from Power-down mode

12.3.1 Wake-up using INT2 to INT9

12.3.2 Wake-up using RST

12.4 Power Control Register (PCON)

12.5 Status of external pins

13 I2C-BUS SERIAL I/O

13.1 Serial Control Register (S1CON)

13.2 Serial Status Register (S1STA)

13.3 Data Shift Register (S1DAT)

13.4 Address Register (S1ADR)

14 INTERRUPT SYSTEM

14.1 External interrupts INT2 to INT9

14.2 Interrupt priority

14.3 Interrupt registers

14.3.1 Interrupt Enable Register (IEN0)

P80CL410; P83CL410

14.3.2 Interrupt Enable Register (IEN1)

14.3.3 Interrupt Priority Register (IP0)

14.3.4 Interrupt Priority Register (IP1)

14.3.5 Interrupt Polarity Register (IX1)

14.3.6 Interrupt Request Flag Register (IRQ1)

15 OSCILLATOR CIRCUITRY

16 RESET

16.1 External reset using the RST pin

16.2 Power-on-reset

17 SPECIAL FUNCTION REGISTERS

OVERVIEW

18 INSTRUCTION SET

19 LIMITING VALUES

20 DC CHARACTERISTICS

21 AC CHARACTERISTICS

22 P85CL000HFZ ‘PIGGY-BACK’

SPECIFICATION

22.1 General description

22.2 Feature differences/additional features of

P85CL000HFZ with respect to P83CL410

22.3 Common specification/feature differences

between P85CL000HFZ and

P83CL410/P80CL51

23 PACKAGE OUTLINES

24 SOLDERING

24.1 Introduction

24.2 DIP

24.2.1 Soldering by dipping or by wave

24.2.2 Repairing soldered joints

24.3 QFP

24.3.1 Reflow soldering

24.3.2 Wave soldering

24.3.3 Repairing soldered joints

24.4 Reflow soldering

24.5 Wave soldering

24.6 Repairing soldered joints

25 DEFINITIONS

26 LIFE SUPPORT APPLICATIONS

27 PURCHASE OF PHILIPS I2C COMPONENTS

1997 Apr 10 2

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

1 FEATURES

• Full static 80C51 Central Processing Unit

• 8-bit CPU, ROM, RAM, I/O in a 40-lead DIP,

40-lead VSO or 44-lead QFP package

• 128 bytes on-chip RAM Data Memory

• 4 kbytes on-chip ROM Program Memory for P83CL410

• External memory expandable up to 128 kbytes: RAM up

to 64 kbytes and ROM up to 64 kbytes

• Four 8-bit ports; 32 I/O lines

• Two 16-bit Timer/Event counters

• On-chip oscillator suitable for RC, LC, quartz crystal or

ceramic resonator

• Thirteen source, thirteen vector, nested interrupt

structure with two priority levels

2

C-bus interface for serial transfer on two lines

• I

• Enhanced architecture with:

– non-page oriented instructions

– direct addressing

– four 8-byte RAM register banks

– stack depth limited only by available internal RAM

(maximum 128 bytes)

– multiply, divide, subtract and compare instructions

• Reduced power consumption through Power-down and

Idle modes

• Wake-up via external interrupts at Port 1

• Frequency range: DC to 12 MHz

• Supply voltage: 1.8 to 6.0 V

• Very low current consumption

• Operating ambient temperature range: −40 to +85 °C.

2 GENERAL DESCRIPTION

The P80CL410; P83CL410 (hereafter generally referred to

as the P8xCL410) is manufactured in an advanced CMOS

technology that allows the device to operate at voltages

down to 1.8 V and at frequencies down to DC.

The P8xCL410 has the same instruction set as the 80C51.

P80CL410; P83CL410

The 8xCL410 has two reduced power modes that are the

same as those on the standard 80C51.

The special reduced power feature of this device is that it

can be stopped and then restarted. Running from an

external clock source, the clock can be stopped and after

a period of time restarted. The 8xCL410 will resume

operation from where it was when the code stopped with

no loss of internal state, RAM contents, or Special

Function Register contents.

If the internal oscillator is used the device cannot be

stopped and started, but the Power-down mode can be

used to achieve similar power savings, without loss of

on-chip RAM and Special Function Register values.

The Power-down mode can be terminated via an interrupt.

This data sheet details the specific properties of the

P80CL410; P83CL410. For details of the 80C51 core see

“Data Handbook IC20”

For emulation purposes, the P85CL000 (piggy-back

version) with 256 bytes of RAM is recommended. Details

are given in Chapter 22.

2.1 ROMless version: P80CL410

The P80CL410 is the ROMless version of the P83CL410.

The mask options on the P80CL410 are fixed as follows:

• All ports have option ‘1S’ (standard port, HIGH after

reset), except ports P1.6 and P1.7 which have option

‘2S’ (open-drain, HIGH after reset)

• Oscillator option: Oscillator 3

• Power-on-reset option: OFF.

3 APPLICATIONS

The P8xCL410 is an 8-bit general purpose microcontroller

especially suited for battery-powered applications.

The P8xCL410 also functions as an arithmetic processor

having facilities for both binary and BCD arithmetic plus

bit-handling capabilities.

.

The P8xCL410 features 4 kbyte ROM (83CL410),

128 bytes RAM (both ROM and RAM are externally

expandable to 64 kbytes), four 8-bit ports, two 16-bit

timer/counter, an I

priority level nested interrupt structure, and on-chip

oscillator circuitry suitable for quartz crystal, ceramic

resonator, RC, or LC. The device operates over a wide

range of supply voltages and has low power consumption.

1997 Apr 10 3

2

C serial interface, a thirteen source two

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

4 ORDERING INFORMATION

TYPE NUMBER

(1)

PACKAGE

ROMless ROM NAME DESCRIPTION VERSION

P80CL410HFP P83CL410HFP DIP40 plastic dual in-line package; 40 leads (600 mil) SOT129-1

P80CL410HFT P83CL410HFT VSO40 plastic very small outline package; 40 leads SOT158-1

− P83CL410HFH QFP44 plastic quad flat package; 44 leads (lead length 1.3 mm);

body 10 × 10 × 1.75 mm

Note

1. Refer to the Order Entry Form (OEF) for this device for the full type number, including options/program.

5 BLOCK DIAGRAM

frequency

reference

XTAL2 XTAL1

P80CL410; P83CL410

SOT307-2

counter (1)

T0 T1

OSCILLATOR

AND

TIMING

CPU

10 3

internal

interrupts

external interrupts (1)

(1) Pins shared with parallel port pins.

PROGRAM

MEMORY

(4K x 8 ROM)

64 kbyte BUS

EXPANSION

CONTROL

control parallel ports,

DATA

MEMORY

(128 x 8 RAM)

PROGRAMMABLE I/O

address/data bus

and I/O pins

P80CL410

P83CL410

TWO 16-BIT

TIMER/EVENT

COUNTERS

I2C-BUS

SERIAL I/O

SDA SCL

(1)

MBK018

Fig.1 Block diagram.

1997 Apr 10 4

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

6 FUNCTIONAL DIAGRAM

V

handbook, full pagewidth

XTAL1

XTAL2

EA

PSEN

ALE

SS

V

DD

P80CL410

P83CL410

RST

P80CL410; P83CL410

port 0

port 1

address and

data bus

INT2

INT3

INT4

INT5

INT6

INT7

INT8/SCL

INT9/SDA

INT0

INT1

alternative

functions

T0

T1

WR

RD

port 3

Fig.2 Functional diagram.

1997 Apr 10 5

MBK019

port 2

address bus

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

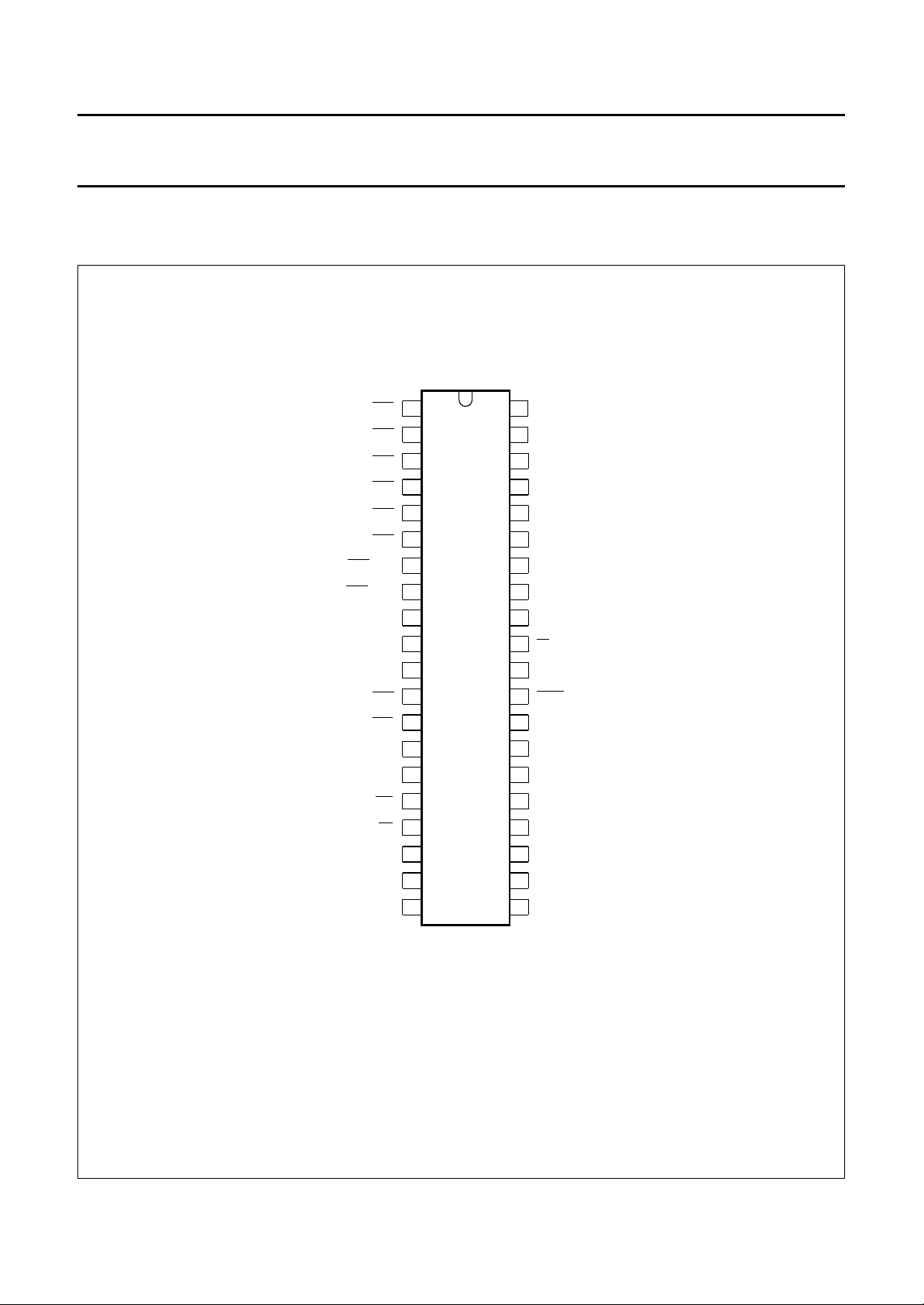

7 PINNING INFORMATION

7.1 Pinning

handbook, halfpage

P1.0/INT2

P1.1/INT3

P1.2/INT4

P1.3/INT5

P1.4/INT6

P1.5/INT7

P1.6/INT8/SCL

P1.7/INT9/SDA

RST

P3.0

P3.1

P3.2/INT0

1

2

3

4

5

6

7

8

9

10

11

12

P80CL410

P83CL410

40

39

38

37

36

35

34

33

32

31

30

29

V

DD

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA

ALE

PSEN

P80CL410; P83CL410

P3.3/INT1

P3.4/T0

P3.5/T1

P3.6/WR

P3.7/RD

XTAL2

XTAL1

V

SS

13

14

15

16

17

18

19

20

MBK017

28

27

26

25

24

23

22

21

P2.7/A15

P2.6/A14

P2.5/A13

P2.4/A12

P2.3/A11

P2.2/A10

P2.1/A9

P2.0/A8

Fig.3 Pin configuration for DIP40 and VSO40 packages.

1997 Apr 10 6

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

handbook, full pagewidth

P1.1/INT3

P1.2/INT4

P1.3/INT5

P1.4/INT6

44

43

42

41

1P1.5/INT7

RST

P3.0

n.c.

P3.1

2

3

4

5

6

7

8

9

10

11

P83CL410HFH

P1.6/INT8/SCL

P1.7/INT9/SDA

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

n.c.

P1.0/INT2

40

39

DD

V

38

P0.1/AD1

P0.0/AD0

37

36

P80CL410; P83CL410

P0.3/AD3

P0.2/AD2

35

34

P0.4/AD4

33

32

P0.5/AD5

31

P0.6/AD6

30

P0.7/AD7

29

EA

n.c.

28

27

ALE

PSEN

26

25

P2.7/A15

24

P2.6/A14

23

P2.5/A13

12

13

14

15

16

SS

P3.7/RD

P3.6/WR

XTAL2

XTAL1

V

Fig.4 Pin configuration for QFP44 package.

1997 Apr 10 7

17

n.c.

18

19

P2.0/A8

P2.1/A9

20

21

P2.2/A10

P2.3/A11

22

MBK016

P2.4/A12

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

7.2 Pin description Table 1 Pin description for DIP40 (SOT190-1), VSO40 (SOT319-2) and QFP44 (SOT307-2) packages

For more extensive description of the port pins see Chapter 10 “I/O facilities”.

PIN

SYMBOL

INT2 1 40 • Port 1: 8-bit bidirectional I/O port (P1.0 to P1.7). Port pins that have

P1.0/

P1.1/

INT3 2 41

INT4 3 42

P1.2/

INT5 4 43

P1.3/

INT6 5 44

P1.4/

INT7 6 1

P1.5/

INT8/SCL 7 2

P1.6/

INT9/SDA 8 3

P1.7/

RST 9 4 Reset: a HIGH level on this pin for two machine cycles while the oscillator

P3.0 10 5 • Port 3: 8-bit bidirectional I/O port (P3.0 to P3.7).

P3.1 11 7

P3.2/INT0 12 8

INT1 13 9

P3.3/

P3.4/T0 14 10

P3.5/T1 15 11

WR 16 12

P3.6/

RD 17 13

P3.7/

XTAL2 18 14 Crystal oscillator output: output of the inverting amplifier of the oscillator.

XTAL1 19 15 Crystal oscillator input: input to the inverting amplifier of the oscillator,

V

SS

P2.0 to P2.7

A8 to A15

PSEN 29 26 Program Store Enable. Output read strobe to external Program Memory.

DIP40

VSO40

20 16 Ground: circuit ground potential.

21 to 28 18 to 25 • Port 2: 8-bit bidirectional I/O port (P2.0 to P2.7) with internal pull-ups.

QFP44

logic 1s written to them are pulled HIGH by internal pull-ups, and in this

state can be used as inputs. As inputs, Port 1 pins that are externally

pulled LOW will source current (IIL, see Chapter 20) due to the internal

pull-ups. Port 1 output buffers can sink/source 4 LS TTL loads.

• Alternative functions:

– INT2 to INT9 are external interrupt inputs

– SCL and SDA are the I2C-bus clock and data lines.

is running resets the device.

Same characteristics as Port 1.

• Alternative functions:

INT0 and INT1 are external interrupts 0 and 1

–

– T0 and T1 are external inputs for timers 0 and 1

– WR is the external Data Memory write strobe

– RD is the external Data Memory read strobe.

Left open when external clock is used.

also the input for an externally generated clock source.

Same characteristics as Port 1.

• High-order addressing: Port 2 emits the high-order address byte

(A8 to A15) during accesses to external memory that use 16-bit

addresses (MOVX @DPTR). In this application it uses the strong internal

pull-ups when emitting logic 1s. During accesses to external memory that

use 8-bit addresses (MOVX @Ri), Port 2 emits the contents of the P2

Special Function Register.

When executing code out of external Program Memory ,PSEN is activated

twice each machine cycle. However, during each access to external Data

Memory two PSEN activations are skipped.

DESCRIPTION

P80CL410; P83CL410

1997 Apr 10 8

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

PIN

SYMBOL

ALE 30 27 Address Latch Enable. Output pulse for latching the low byte of the

EA 31 29 External Access. When EA is held HIGH the CPU executes out of internal

P0.0 to P0.7

AD0 to AD7

V

DD

n.c. − 6, 17, 28

DIP40

VSO40

39 to 32 30 to 37 • Port 0: 8-bit open-drain bidirectional I/O port. As an open-drain output

40 38 Power supply.

QFP44

and 39

address during access to external memory. ALE is emitted at a constant

rate of1⁄6× f

(assuming MOVX instructions are not used).

program memory (unless the program counter exceeds 0FFFH). Holding

EA LOW forces the CPU to execute out of external memory regardless of

the value of the program counter.

port it can sink 8 LS TTL loads. Port 0 pins that have logic 1s written to

them float, and in that state will function as high impedance inputs.

• Low-order addressing: Port 0 is also the multiplexed low-order address

and data bus during access to external memory. The strong internal

pull-ups are used while emitting logic 1s within the low order address.

Not connected.

, and may be used for external timing or clocking purposes

osc

DESCRIPTION

P80CL410; P83CL410

1997 Apr 10 9

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

8 FUNCTIONAL DESCRIPTION OVERVIEW

This chapter gives a brief overview of the device.

The detailed functional description is in the following

chapters:

Chapter 9 “Memory organization”

Chapter 10 “I/O facilities”

Chapter 11 “Timers/event counters”

Chapter 12 “Reduced power modes”

Chapter 13 “I2C-bus serial I/O”

Chapter 14 “Interrupt system”

Chapter 15 “Oscillator circuitry”

Chapter 16 “Reset”.

8.1 General

The P8xCL410 is a stand-alone high-performance CMOS

microcontroller designed for use in real-time applications

such as instrumentation, industrial control, intelligent

computer peripherals and consumer products.

The device provides hardware features, architectural

enhancements and new instructions to function as a

controller for applications requiring up to 64 kbytes of

Program Memory and/or up to 64 kbytes of Data Memory.

The P8xCL410 contains a 4 kbytes Program Memory

(ROM; P83CL410); a static 128 bytes Data Memory

(RAM); 32 I/O lines; two16-bit timer/event counters;

a thirteen-source, two priority-level, nested interrupt

structure and on-chip oscillator and timing circuit.

2

C-bus serial interface is also provided.

An I

The device has two software-selectable modes of reduced

activity for power reduction:

• Idle mode; freezes the CPU while allowing the timers,

serial I/O and interrupt system to continue functioning.

• Power-down mode; saves the RAM contents but

freezes the oscillator causing all other chip functions to

be inoperative.

P80CL410; P83CL410

9 MEMORY ORGANIZATION

The P8xCL410 has 4 kbytes of Program Memory (ROM;

P83CL410 only) plus 128 bytes of Data Memory (RAM) on

board. The device has separate address spaces for

Program and Data Memory (see Fig.5). Using Port latches

P0 and P2, the P8xCL410 can address a maximum of

64 kbytes of program memory and a maximum of

64 kbytes of data memory. The CPU generates. The CPU

generates both read (

external Data Memory accesses, and the read strobe

PSEN) for external Program Memory.

(

9.1 Program Memory

After reset the CPU begins program execution at location

0000H. The lower 4 kbytes of Program Memory can be

implemented in the on-chip ROM (P83CL410 only) or in

external Program Memory.

EA pin is tied to VDD, then Program Memory fetches

If the

from addresses 0000H to 0FFFH are directed to the

internal ROM. Fetches from addresses 1000H to FFFFH

are directed to external ROM. Program Counter values

greater than 0FFFH are automatically addressed to

external memory regardless of the state of the EA pin.

9.2 Data Memory

The P8xCL410 contains128 bytes of internal RAM and 27

Special Function Registers (SFR). The memory map

(Fig.5) shows the internal Data Memory space divided into

the lower 128, the upper 128, and the SFR space.

The lower 128 bytes of the internal RAM are organized as

mapped in Fig.6. The lowest 32 bytes are grouped into 4

banks of 8 registers. Program instructions refer to these

registers within a register bank as R0 through R7. Two bits

in the Program Status Word select which register bank is

in use. The next 16 bytes above the register banks form a

block of bit-addressable memory space. The 128 bits in

this area can be directly addressed by the single-bit

manipulation instructions. The remaining registers

(30H to 7FH) are directly and indirectly byte addressable.

RD) and write (WR) signals for

8.2 CPU timing

A machine cycle consists of a sequence of 6 states. Each

state lasts for two oscillator periods, thus a machine cycle

takes 12 oscillator periods or 1 µs if the oscillator

frequency (f

1997 Apr 10 10

) is 12 MHz.

osc

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

handbook, full pagewidth

4095

64K

4096

INTERNAL

(EA = 1)

EXTERNAL

4095

EXTERNAL

(EA = 0)

255

127

0

OVERLAPPED SPACE

INTERNAL

DATA RAM

P80CL410; P83CL410

64K

SPECIAL

FUNCTION

REGISTERS

0

PROGRAM MEMORY

INTERNAL DATA MEMORY

Fig.5 Memory map.

MLA559

EXTERNAL

DATA MEMORY

1997 Apr 10 11

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

handbook, halfpage

R7

R0

R7

R0

R7

7FH

30H

2FH

20H

1FH

18H

17H

10H

0FH

P80CL410; P83CL410

bit-addressable space

(bit addresses 0 to 7F)

4 banks of 8 registers

(R0 to R7)

R0

R7

R0

Fig.6 The lower 128 bytes of internal RAM.

9.3 Special Function Registers (SFRs)

The upper 128 bytes are the address locations of the

SFRs. Figure 7 shows the SFR space. The SFRs include

the port latches, timers, peripheral control, serial I/O

registers, etc. These registers can only be accessed by

direct addressing. There are 128 directly addressable

locations in the SFR address space (SFRs with addresses

divisible by eight).

9.4 Addressing

The P8xCL410 has five methods for addressing source

operands:

• Register

• Direct

• Register-indirect

• Immediate

• Base-register plus index-register-indirect.

08H

07H

0

MLA560 - 1

The first three methods can be used for addressing

destination operands. Most instructions have a

‘destination/source’ field that specifies the data type,

addressing methods and operands involved.

For operations other than MOVs, the destination operand

is also a source operand.

Access to memory addressing is as follows:

• Registers in one of the four register banks through

register, direct or register-indirect

• Internal RAM (128 bytes) through direct or

register-indirect

• Special Function Registers through direct

• External data memory through register-indirect

• Program Memory look-up tables through base-register

plus index-register-indirect.

1997 Apr 10 12

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

REGISTER

MNEMONIC

IP1

B

IX1

IEN1

ACC

S1ADR

S1DAT

S1STA

S1CON

BIT ADDRESS

FEFF FD FC FB FA F9 F8

F6F7 F5 F4 F3 F2 F1 F0

EEEF ED EC EB EA E9 E8

E6E7 E5 E4 E3 E2 E1 E0

DEDF DD DC DB DA D9 D8

DIRECT

BYTE

ADDRESS (HEX)

FFH

F8H

F0H

E9H

E8H

E0H

DBH

DAH

D9H

D8H

P80CL410; P83CL410

PSW

IRQ1

IP0

IEN0

P1

TH1

TH0

TL1

TL0

TMOD

TCON

PCON

DPH

DPL

SP

P0

P3

P2

D6D7 D5 D4 D3 D2 D1 D0

C6C7 C5 C4 C3 C2 C1 C0

BE BD BC BB BA B9 B8

B6B7 B5 B4 B3 B2 B1 B0

AEAF AD AC AB AA A9 A8

A6A7 A5 A4 A3 A2 A1 A0

9697 95 94 93 92 91 90

8E8F 8D 8C 8B 8A 89 88

8687 85 84 83 82 81 80

D0H

C0H

B8H

B0H

A8H

A0H

90H

8DH

8CH

8BH

8AH

89H

88H

87H

83H

82H

81H

80H

SFRs containing

directly addressable

bits

MBK020

Fig.7 Special Function Register memory map.

1997 Apr 10 13

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

10 I/O FACILITIES

10.1 Ports

The P8xCL410 has 32 I/O lines treated as 32 individually

addressable bits or as four parallel 8-bit addressable ports.

Ports 0, 1, 2 and 3 perform the alternative functions

detailed below. To enable a port pin alternate function, the

port bit latch in its SFR must contain a logic 1.

Port 0 Provides the multiplexed low-order address and

data bus for expanding the device with standard

memories and peripherals.

Port 1 Used for the external interrupts

the I2C-bus interface lines SCL and SDA.

Port 2 Provides the high-order address when expanding

the device with external Program or Data Memory.

Port 3 Pins can be configured individually to provide:

• External interrupt request inputs: INT1 and INT0

• Timer/counter inputs: T1 and T0

• Control signals to read and write to external

memories: RD and WR.

Each port consists of a latch (SFRs P0 to P3), an output

driver and input buffer. Ports 1, 2, and 3 have internal

pull-ups Figure 8(a) shows that the strong transistor ‘p1’ is

turned on for only 2 oscillator periods after a LOW-to-HIGH

transition in the port latch. When on, it turns on ‘p3’ (a weak

pull-up) through the inverter. This inverter and ‘p3’ form a

latch which holds the logic 1. In Port 0 the pull-up ‘p1’ is

only on when emitting logic 1s for external memory

access. Writing a logic 1 to a Port 0 bit latch leaves both

output transistors switched off so that the pin can be used

as a high-impedance input.

INT2 to INT9, and

P80CL410; P83CL410

Option 3 Push-pull; output with drive capability in both

polarities. Under this option, pins can only be

used as outputs; see Fig.8(c).

10.3 Port 0 options

The definition of port options for Port 0 is slightly different.

Two cases are considered. First, access to external

memory (

boundary) and second, I/O accesses.

10.3.1 E

Option 1 True logic 0 and logic 1 are written as address to

Option 2 An external pull-up resistor is required for

Option 3 Not allowed for external memory accesses as

10.3.2 I/O A

Option 1 When writing a logic 1 to the port latch, the

Option 2 Open-drain; quasi-directional I/O with n-channel

Option 3 Push-Pull; output with drive capability in both

EA = 0 or access above the built-in memory

XTERNAL MEMORY ACCESSES

the external memory (strong pull-up to be used).

external accesses.

the port can only be used as output.

CCESSES

strong pull-up ‘p1’ will be on for 2 oscillator

periods. No weak pull-up exists. Without an

external pull-up, this option can be used as a

high-impedance input.

open-drain output. Use as an output requires the

connection of an external pull-up resistor.

See Fig.8(b).

polarities. Under this option pins can only be

used as outputs. See Fig.8(c).

10.2 Port options

The pins of port 1 (except P1.6 and P1.7; with option 2S

only), port 2 and port 3 may be individually configured with

one of the following options. These options are also shown

in Fig.8.

Option 1 Standard Port; quasi-bidirectional I/O with

pull-up. The strong booster pull-up ‘p1’ is turned

on for two oscillator periods after a

LOW-to-HIGH transition in the port latch;

Fig.8(a).

Option 2 Open-drain; quasi-bidirectional I/O with

n-channel open-drain output. Use as an output

requires the connection of an external pull-up

resistor; see Fig.8(b).

1997 Apr 10 14

10.4 SET/RESET options

Individual mask selection of the post-reset state is

available with any of the above pins. The required

selection is made by appending ‘S’ or ‘R’ to Options 1, 2,

or 3 above.

Option R RESET, at reset this pin will be initialized LOW.

Option S SET, at reset this pin will be initialized HIGH.

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

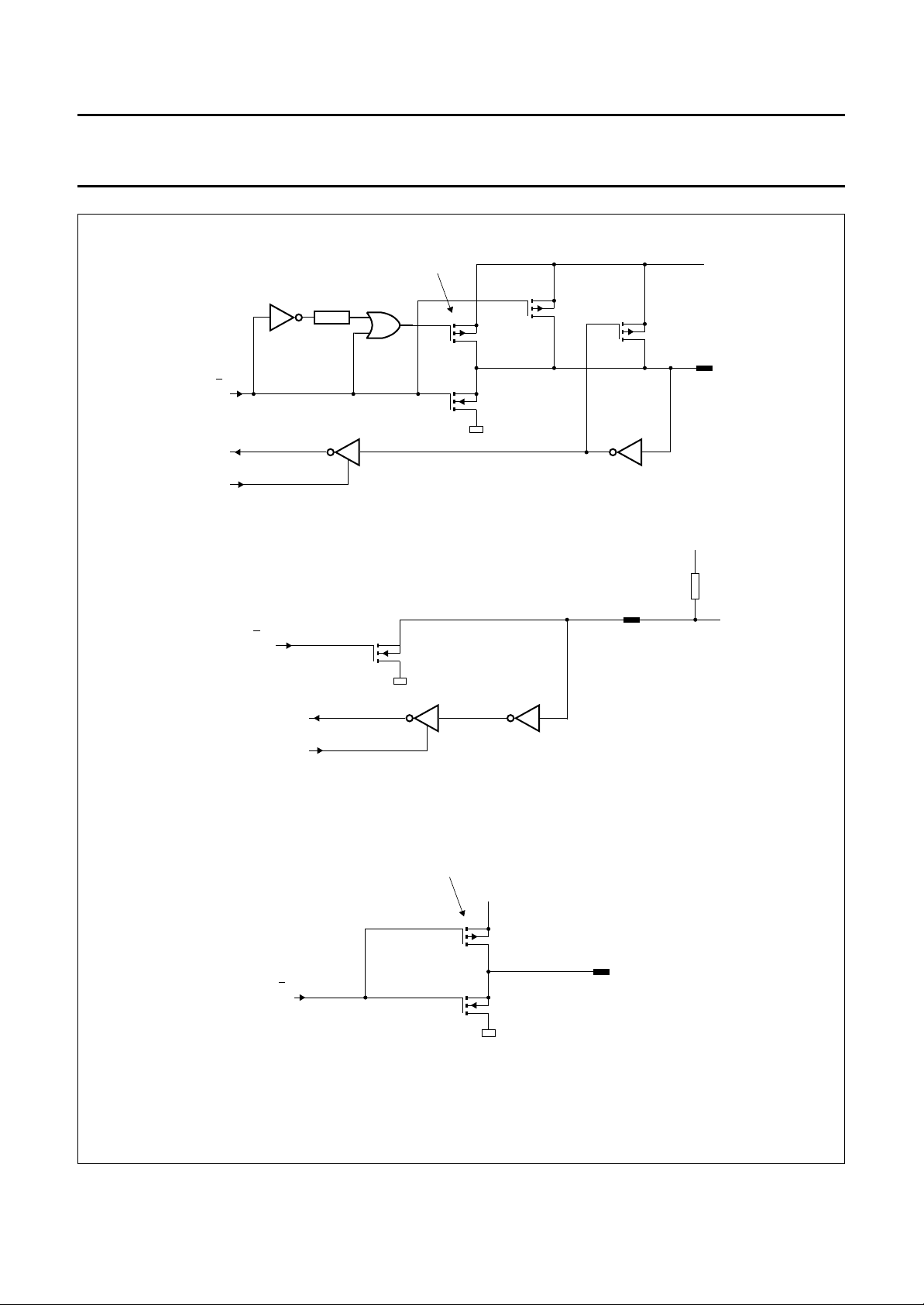

handbook, full pagewidth

from port latch

read port pin

input data

2 oscillator

periods

Q

strong pull-up

INPUT

BUFFER

(a) Standard

P80CL410; P83CL410

+5 V

p2

p1

n

p3

I/O pin

+5 V

from port latch

read port pin

from port latch

Q

input data

Q

n

INPUT

BUFFER

(b) Open-drain

strong pull-up

+5 V

external

pull-up

I/O pin

p1

I/O pin

n

(c) Push-pull

Fig.8 Port configuration options.

1997 Apr 10 15

MGD677

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

11 TIMERS/EVENT COUNTERS

The P8xCL410 contains two16-bit timer/event counter

registers; Timer 0 and Timer 1, which can perform the

following functions:

• Measure time intervals and pulse durations

• Count events

• Generate interrupt requests.

In the ‘Timer’ operating mode the register is incremented

every machine cycle. Since a machine cycle consists of 12

oscillator periods, the count rate is1⁄12× f

In the ‘Counter’ operating mode, the register is

incremented in response to a HIGH-to-LOW transition.

Since it takes 2 machine cycles (24 oscillator periods) to

recognize a HIGH-to-LOW transition, the maximum count

1

rate is

should be held for at least one complete machine cycle.

Timer 0 and Timer 1 can be programmed independently to

operate in four modes:

Mode 0 8-bit timer or 8-bit counter each with divide-by-32

Mode 1 16-bit time-interval or event counter.

Mode 2 8-bit time-interval or event counter with automatic

Mode 3 Timer 0 establishes TL0 and TH0 as two

⁄24× f

. To ensure a given level is sampled, it

osc

prescaler.

reload upon overflow.

separate counters.

osc

.

P80CL410; P83CL410

The following functions remain active during the Idle

mode:

• Timer 0 and Timer 1

2

C-bus

• I

• External interrupt.

These functions may generate an interrupt or reset; thus

ending the Idle mode.

There are two ways to terminate the Idle mode:

1. Activation of any enabled interrupt will cause IDL

(PCON.0) to be cleared by hardware thus terminating

the Idle mode. The interrupt is serviced, and following

the RETI instruction, the next instruction to be

executed will be the one following the instruction that

put the device in the Idle mode. The flag bits GF0

(PCON.2) and GF1 (PCON.3) may be used to

determine whether the interrupt was received during

normal execution or during the Idle mode.

For example, the instruction that writes to PCON.0 can

also set or clear one or both flag bits. When the Idle

mode is terminated by an interrupt, the service routine

can examine the status of the flag bits.

2. The second way of terminating the Idle mode is with an

external hardware reset. Since the oscillator is still

running, the hardware reset is required to be active for

two machine cycles (24 oscillator periods) to complete

the reset operation. Reset redefines all SFRs but does

not affect the on-chip RAM.

12 REDUCED POWER MODES

There are two software selectable modes of reduced

activity for further power reduction: Idle and Power-down.

12.1 Idle mode

Idle mode operation permits the external interrupts,

2

C-bus, and timer blocks to continue to function while the

I

clock to the CPU is halted.

Idle mode is entered by setting the IDL bit in the Power

Control Register (PCON.0, see Table 3). The instruction

that sets IDL is the last instruction executed in the normal

operating mode before the Idle mode is activated

Once in Idle mode, the CPU status is preserved along with

the Stack Pointer, Program Counter, Program Status

Word and Accumulator. The RAM and all other registers

maintain their data during Idle mode. The status of the

external pins during Idle mode is shown in Table 4.

1997 Apr 10 16

12.2 Power-down mode

Operation in Power-down mode freezes the oscillator.

The internal connections which link both Idle and

Power-down signals to the clock generation circuit are

shown in Fig.9.

Power-down mode is entered by setting the PD bit in the

Power Control Register (PCON.1, see Table 2).

The instruction that sets PD is the last executed prior to

going into the Power-down mode.

Once in the Power-down mode, the oscillator is stopped.

The contents of the on-chip RAM and the SFRs are

preserved. The port pins output the value held by their

respective SFRs. ALE and

In the Power-down mode, VDD may be reduced to

minimize circuit power consumption. The supply voltage

must not be reduced until the Power-down mode is

entered, and must be restored before the hardware reset

is applied which will free the oscillator. Reset should not be

released until the oscillator has restarted and stabilized.

PSEN are held LOW.

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

12.3 Wake-up from Power-down mode

When in Power-down mode the controller can be

woken-up with either the external interrupts INT2 to INT9,

or a reset operation. The wake-up operation has two basic

approaches as explained in Section 12.3.1; 12.3.2 and

illustrated in Fig.10.

12.3.1 W

If any of the interrupts INT2 to INT9 are enabled, the

device can be woken-up from the Power-down mode with

the external interrupts. To ensure that the oscillator is

stable before the controller restarts, the internal clock will

remain inactive for 1536 oscillator periods. This is

controlled by an on-chip delay counter.

12.3.2 W

To wake-up the P8xCL410, the RST pin must be kept

HIGH for a minimum of 24 periods. The on-chip delay

counter is inactive. The user must ensure that the oscillator

is stable before any operation is attempted.

AKE-UP USING INT2 TO INT9

AKE-UP USING RST

P80CL410; P83CL410

12.4 Power Control Register (PCON)

See Tables 2 and 3. Idle and Power-down modes are

activated by software using this SFR. PCON is not

bit-addressable.

12.5 Status of external pins

The status of the external pins during Idle and Power-down

mode is shown in Table 3. If the Power-down mode is

activated whilst accessing external Program Memory, the

port data that is held in the Special Function Register P2 is

restored to Port 2.

If the data is a logic 1, the port pin is held HIGH during the

Power-down mode by the strong pull-up transistor ‘p1’;

see Fig.8(a).

Table 2 Power Control Register (address 87H)

76543210

−−−−GF1 GF0 PD IDL

Table 3 Description of PCON bits

BIT SYMBOL DESCRIPTION

7, 6, 5, 4 − reserved

3 and 2 GF1 and GF0 General purpose flag bits

1PDPower-down bit; setting this bit activates the Power-down mode

0 IDL Idle mode bit; setting this bit activates the Idle mode

Table 4 Status of external pins during Idle and Power-down modes

MODE MEMORY ALE

Idle internal 1 1 port data port data port data port data port data

external 1 1 floating port data address port data port data

Power-down internal 0 0 port data port data port data port data port data

external 0 0 floating port data port data port data port data

PSEN PORT 0 PORT 1 PORT 2 PORT 3 PORT 4

1997 Apr 10 17

Philips Semiconductors Product specification

Low voltage 8-bit microcontrollers with

2

I

C-bus

book, full pagewidth

OSCILLATOR

PD

P80CL410; P83CL410

XTAL1XTAL2

interrupts

serial ports

CLOCK

GENERATOR

timer blocks

CPU

IDL

MLA563

handbook, full pagewidth

power-down

RST pin

external

interrupt

oscillator

Fig.9 Internal clock control in Idle and Power-down mode.

delay counter

1536 periods

24 periods

MGD679

Fig.10 Wake-up operation.

1997 Apr 10 18

Loading...

Loading...