DISCRETE SEMICONDUCTORS

DATA SH EET

LLE18100X

NPN silicon planar epitaxial

microwave power transistor

Product specification

November 1994

Philips Semiconductors Product specification

NPN silicon planar epitaxial microwave

power transistor

FEATURES

• Diffused emitter ballasting resistors

providing excellent current sharing

and withstanding a high VSWR

• Interdigitated structure provides

high emitter efficiency

• Gold metallization realizes very

good stability of the characteristics

and excellent lifetime

• Multicell geometry gives good

balance of dissipated power and

low thermal resistance

• Internal input prematching ensures

good stability and allows an easier

design of wideband circuits.

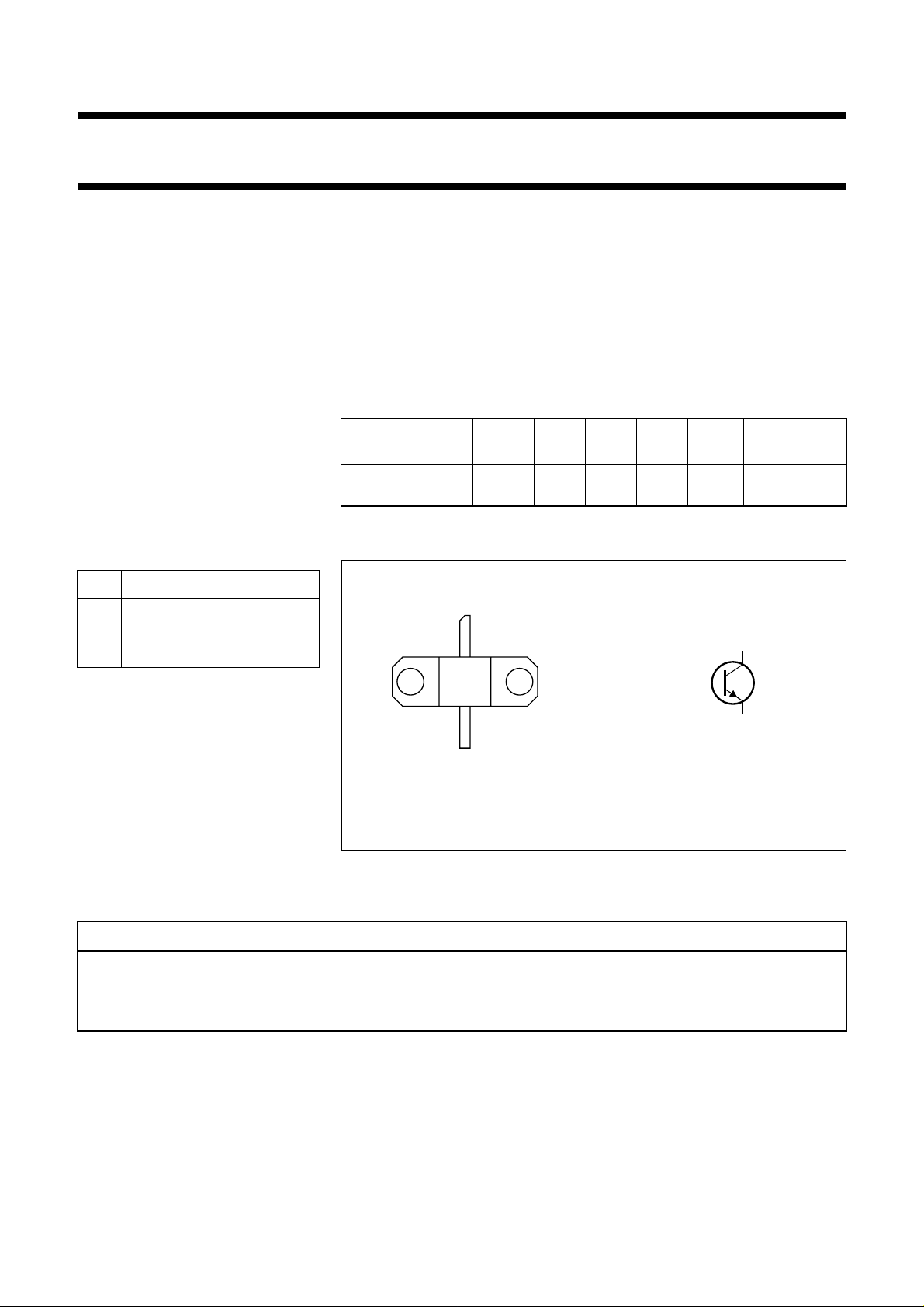

PINNING - SOT437A

PIN DESCRIPTION

1 collector

2 base

3 emitter connected to flange

DESCRIPTION

NPN silicon planar epitaxial

microwave power transistor in a

SOT437A glued cap metal ceramic

flange package, with emitter

connected to flange.

QUICK REFERENCE DATA

Microwave performance up to T

amplifier.

MODE OF

OPERATION

class AB (CW) 1.85 24 0.1 ≥ 9 ≥ 8 see Figs 8

PIN CONFIGURATION

page

Top view

(GHz)

1

2

f

3

MBC045

LLE18100X

APPLICATIONS

Intended for use in common emitter,

class AB power amplifiers in CW

conditions for professional

applications at 1.85 GHz.

= 25 °C in a common emitter class AB

mb

V

(V)

handbook, halfpage

CE

I

CQ

(A)

P

L1

(W)

MBB012

b

G

po

(dB)

c

e

ZI/Z

(Ω)

and 9

L

Fig.1 Simplified outline and symbol.

WARNING

Product and environmental safety - toxic materials

This product contains beryllium oxide. The product is entirely safe provided that the BeO disc is not damaged. All

persons who handle, use or dispose of this product should be aware of its nature and of the necessary safety

precautions. After use, dispose of as chemical or special waste according to the regulations applying at the location of

the user. It must never be thrown out with the general or domestic waste.

November 1994 2

Philips Semiconductors Product specification

NPN silicon planar epitaxial microwave

LLE18100X

power transistor

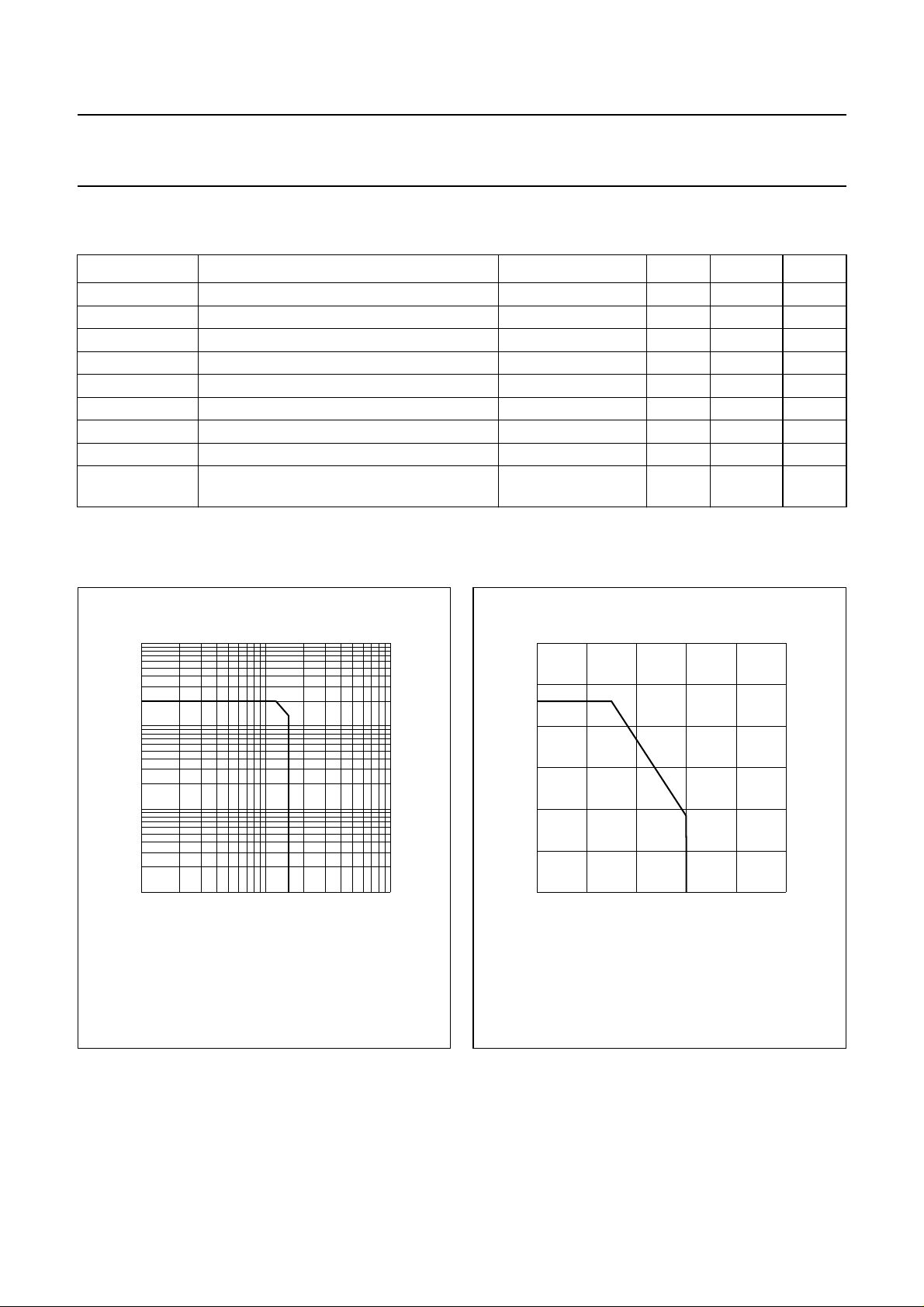

LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

CBO

V

CER

V

CEO

V

EBO

I

C

P

tot

T

stg

T

j

T

sld

Note

1. Up to 0.2 mm from ceramic.

collector-base voltage open emitter − 45 V

collector-emitter voltage RBE= 220 Ω−30 V

collector-emitter voltage open base − 15 V

emitter-base voltage open collector − 3V

collector current − 2A

total power dissipation Tmb=75°C − 23 W

storage temperature range −65 150 °C

junction temperature − 200 °C

soldering temperature t ≤ 10 s

− 235 °C

note 1

10

handbook, halfpage

I

C

(A)

1

−1

10

−2

10

110

Tmb≤ 75°C

(1) Region of permissible DC operation

Fig.2 DC SOAR.

(1)

VCE (V)

MRA545

30

handbook, halfpage

P

tot

(W)

25

20

15

10

5

2

10

0

0 50 100 150 200

P

max = 23 W.

tot

MRA544

Tmb (

250

o

C)

Fig.3 Maximum power dissipation derating as a

function of mounting base temperature.

November 1994 3

Loading...

Loading...