Page 1

Colour Television Chassis

LC4.41E

AB

Supplement to manual LC4.41E AA 3122 785 16240

ME6

G_16240_000.eps

170206

Contents Page

1. Technical Specifications, Connections, and Chassis

Overview 2

2. Safety Instructions, Warnings, and Notes 3

3. Directions for Use 3

4. Mechanical Instructions 4

5. Service Modes, Error Codes, and Fault Finding 5

6. Block Diagrams, Test Point Overviews, and

Waveforms

Wiring Diagram 42” (FHP) 7

Wiring Diagram 42” & 50” Plasma 8

Block Diagram Supply 42” FHP 9

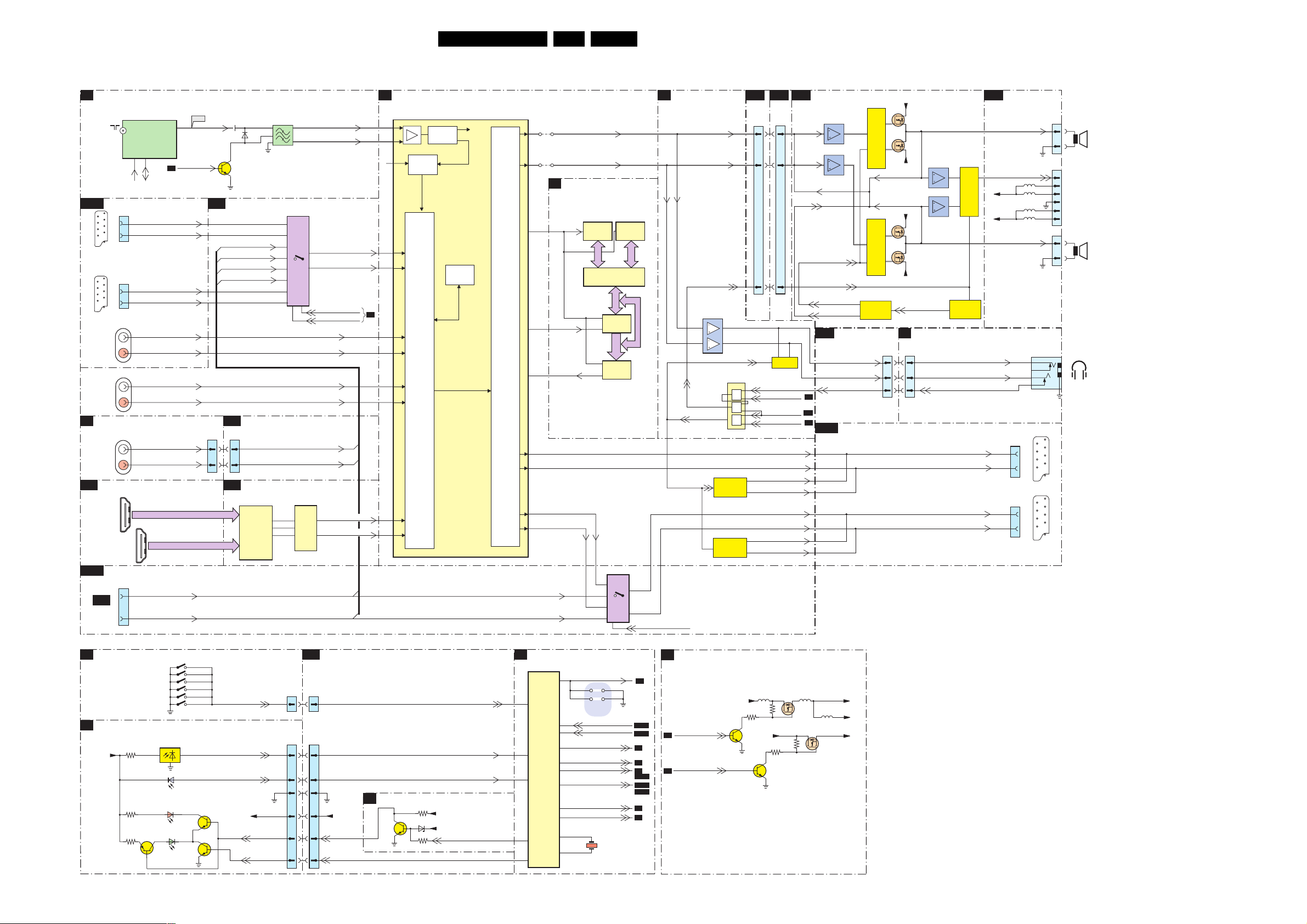

Block Diagram Video 10

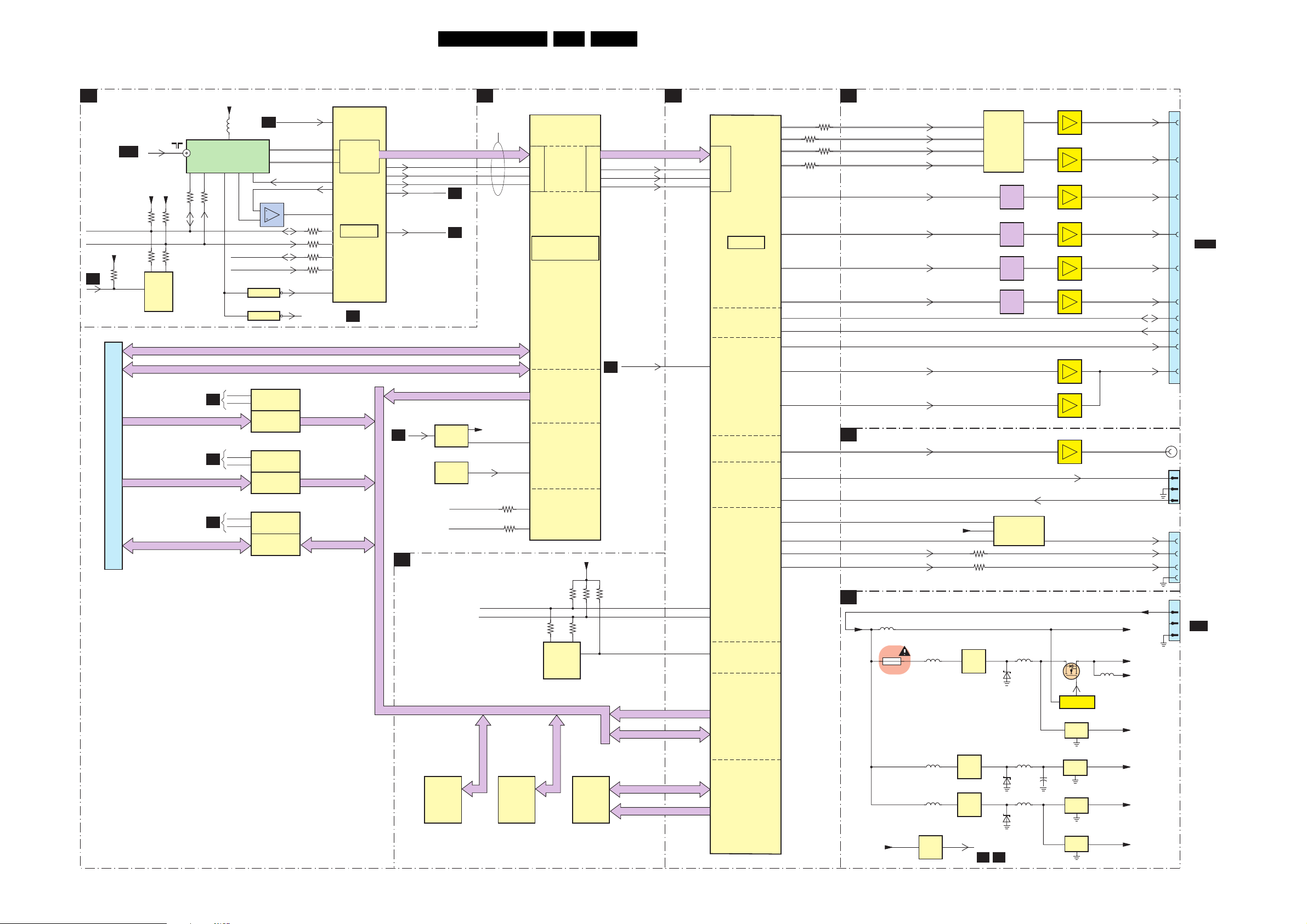

Block Diagram Audio & Control 11

Block Diagram IBO Zapper 12

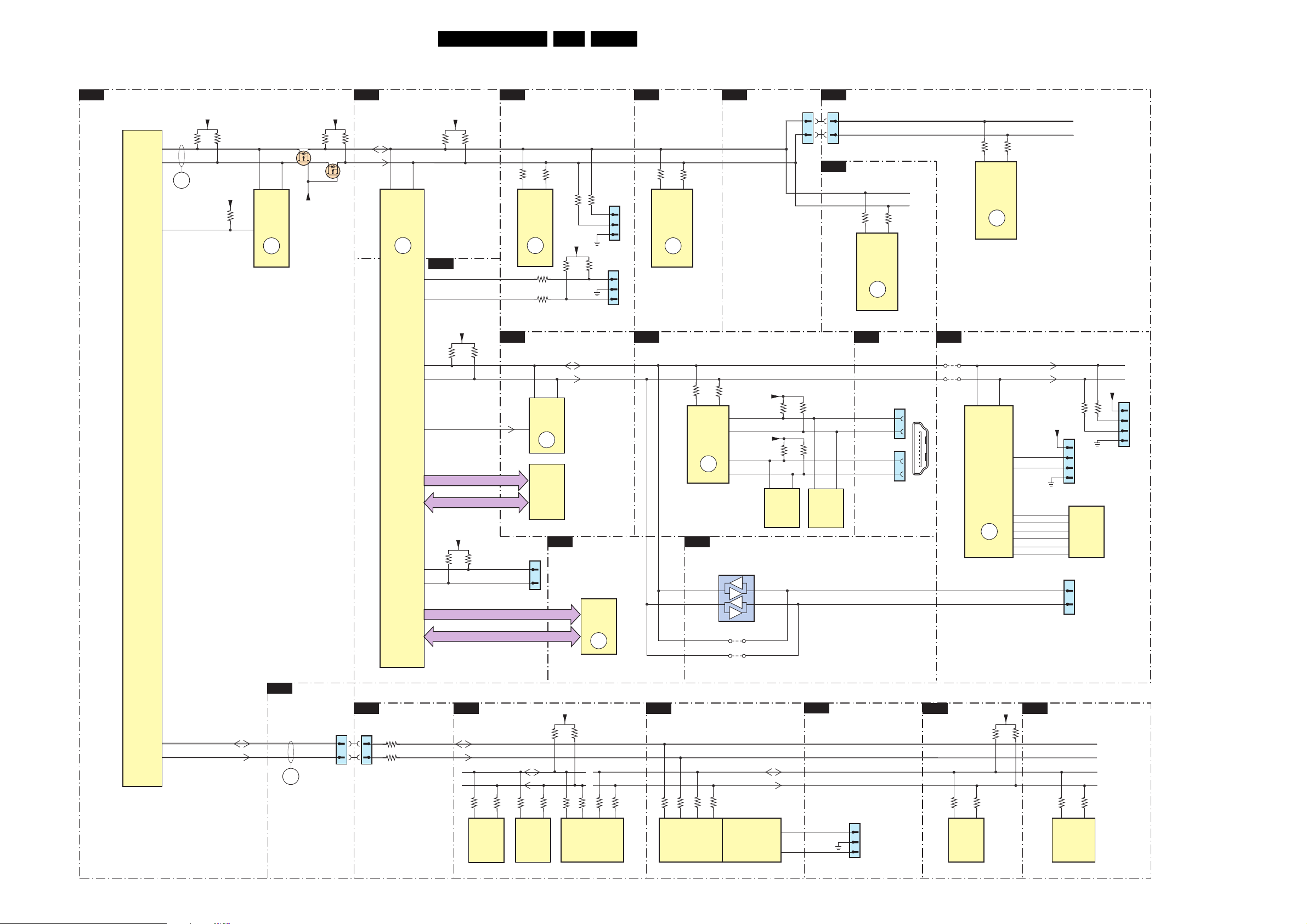

I2C Overview 13

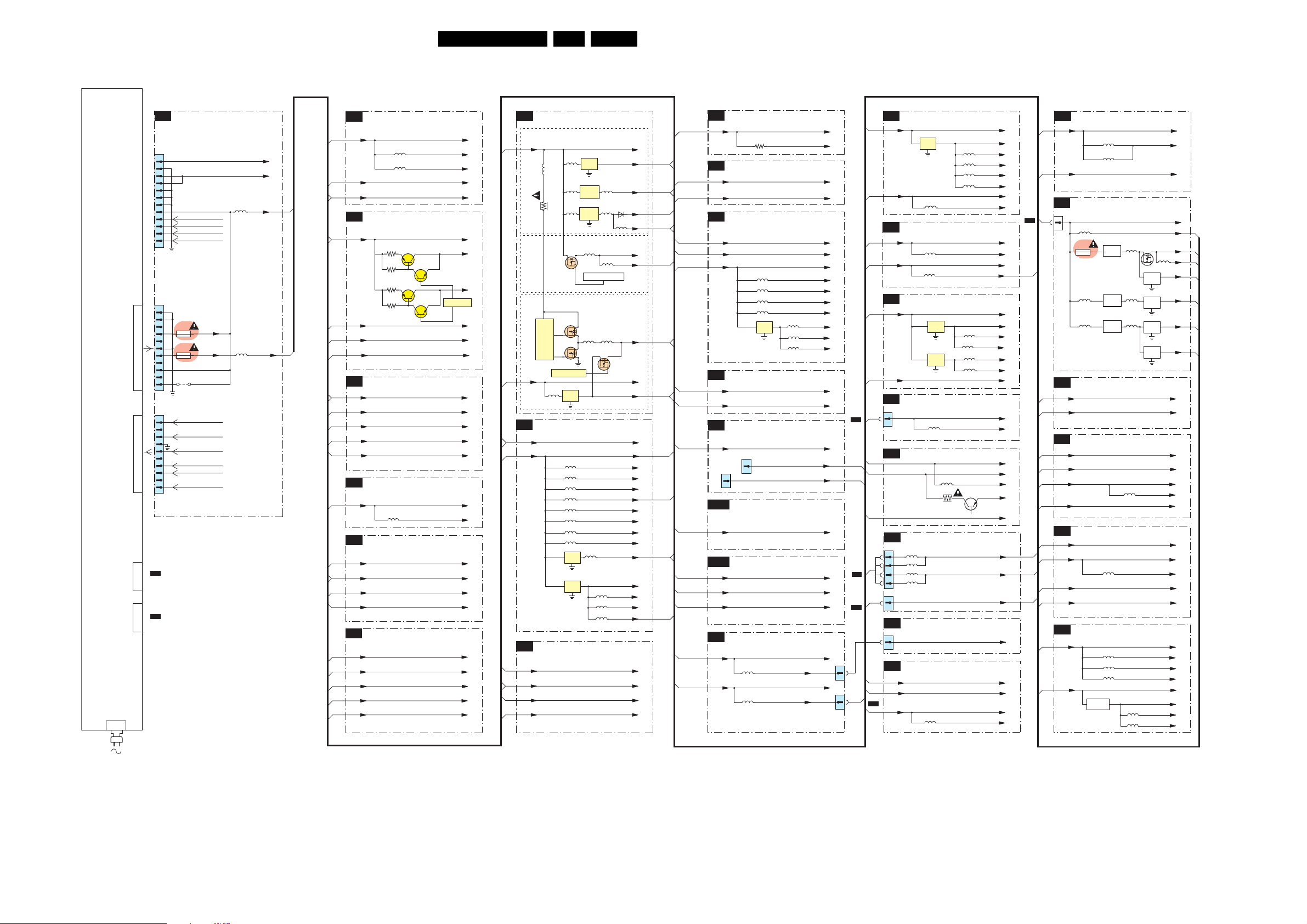

Supply Voltage Overview 14

7. Circuit Diagrams and PWB Layouts Diagram PWB

IBO Zapper Panel: MOJO (K1) 15 22-31

IBO Zapper Panel: Flash Memory (K2) 16 22-31

IBO Zapper Panel: Power Supply (K3) 17 22-31

IBO Zapper Panel: Interface (K4) 18 22-31

IBO Zapper Panel: Analog Back End (K5) 19 22-31

IBO Zapper Panel: Front End (K6) 20 22-31

IBO Zapper Panel: Common Interface (K7) 21 22-31

8. Alignments 33

9. Circuit Descriptions, Abbreviation List, and IC Data

Sheets 36

Abbreviation List 38

IC Data Sheets 40

10. Spare Parts List 42

11. Revision List 44

©

Copyright 2006 Philips Consumer Electronics B.V. Eindhoven, The Netherlands.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic,

mechanical, photocopying, or otherwise without the prior permission of Philips.

Published by WS 0663 TV Service Printed in the Netherlands Subject to modification EN 3122 785 16230

Page 2

EN 2 LC4.41E AB1.

Technical Specifications, Connections, and Chassis Overview

1. Technical Specifications, Connections, and Chassis Overview

Index of this chapter:

1.1 Technical Specifications

1.2 Connection Overview

1.3 Chassis Overview

Notes:

• Only information that is related to the IBO Zapper module

is published in this manual. For the other information, see

the relevant chassis manual (order code on front page).

• Some models in this chassis range have a different

mechanical construction. The information given here is

therefore model specific.

• Figures below can deviate slightly from the actual situation,

due to the different set executions.

• Specifications are indicative (subject to change).

1.1 Technical Specifications

1.1.1 Vision

Display type : Plasma

Screen size :

- 42PF5521D/10/12 : 42” (107 cm), 16:9

- 42PF7521D/10/12 : 42” (107 cm), 16:9

- 50PF7521D/10 : 50” (127 cm), 16:9

Resolution (HxV pixels) :

- 42PF5521D/10/12 : 1024 x 1080

- 42PF7521D/10/12 : 1024 x 768

- 50PF7521D/10 : 1366 x 768

Contrast ratio : 10000 : 1

Light output (cd/m

2

) : 1400

DVB : DVB - terrestrial

1.1.2 Sound

Sound systems : NICAM B/G, D/K, I, L

: AV Stereo

Maximum power (W

) : 2 x 15

RMS

1.1.3 Miscellaneous

Power supply:

Mains voltage (V

) : 220 - 240

AC

Mains frequency (Hz) : 50 / 60

Ambient conditions:

- Temperature range (°C) : +5 to +40

- Maximum humidity : 90% R.H.

Power consumption:

Normal operation (W) :

- 42” : 230

- 50” : 360

Stand-by (W) : < 2

Dimensions (WxHxD cm):

- 42PF5521D/10/12 : 123.6 x 67.9 x 12.6

- 42PF7521D/10/12 : 124.9 x 68.8 x 12.8

- 50PF7521D/10 : 142.5 x 78.6 x 11.8

Weight (kg):

- 42PF5521D/10/12 : 39.2

- 42PF7521D/10/12 : 43.0

- 50PF7521D/10 : 57.3

Response time (ms) : 3

Viewing angle (HxV degrees) : 160 x 160

Tuning system : PLL

TV Colour systems : PAL B/G, D/K, I

: SECAM B/G, D/K, L/L’

Video playback : NTSC M/N 3.58, 4.43

: PAL B/G

: SECAM L/L’

Supported computer formats : VGA (640x480)

: MAC (640x480)

: SVGA (800x600)

: XVGA (1024x768)

: VGA (720x400)

Supported video formats : 640x480i - 1fH

: 640x480p - 2fH

: 720x576i - 1fH

: 720x576p - 2fH

: 1280x720p - 3fH

: 1920x1080i - 2fH

Presets/channels : 100 presets

Tuner bands : VHF

: UHF

: S-band

: Hyper-band

1.2 Connection Overview

Note: The following connector colour abbreviations are used

(acc. to DIN/IEC 757): Bk= Black, Bu= Blue, Gn= Green, Gy=

Grey, Rd= Red, Wh= White, and Ye= Yellow.

1.2.1 Rear Connections

Figure 1-1 Rear I/O

CI Common Interface: PCMCIA

68p- See diagram K7 jk

S/PDIF Cinch: Out

Bk - Coaxial 0.2 - 0.6 V

Service connector (UART)

1 -UART_TX Transmit k

2 -Ground Gnd H

3 -UART_RX Receive j

/ 75 ohm kq

PP

G_16220_021.eps

090206

Page 3

1.3 Chassis Overview

LCD PANEL

POWER SUPPLY

A

PA NE L

SMALL SIGNAL

B

BOARD

OTC TXT PANEL

T

CONTROL BOARD

E

Safety Instructions, Warnings, and Notes

AUDIO PANEL

IBO ZAPPER 2 PANEL

EN 3LC4.41E AB 2.

C

K

Figure 1-2 Chassis overview

2. Safety Instructions, Warnings, and Notes

See the relevant chassis manual (order code on front page).

3. Directions for Use

You can download this information from the following websites:

http://www.philips.com/support

http://www.p4c.philips.com

SIDE I/O PANEL

LED & IR PANEL

G_15451_003.eps

D

J

030306

Page 4

EN 4 LC4.41E AB4.

Mechanical Instructions

4. Mechanical Instructions

Index of this chapter:

4.1 Assy/Panel Removal

4.2 Set Re-assembly

Notes:

• Figures below can deviate slightly from the actual situation,

due to the different set executions.

• Follow the disassembling instructions in described order.

• Only information that is related to the IBO Zapper module

is published in this manual. For the other information, see

the relevant chassis manual (order code on front page).

4.1 Assy/Panel Removal

4.1.1 Cover Shield for IBO-zapper & SSB

1

3

2

4

5

12. Carefully unlock the locking mechanism of the FFC

connector [9] and remove the flatfoil cable (see Figure

“How to unlock an FFC connector”).

13. Finally, loosen four screws [10], and remove the IBO

zapper from the top shielding.

9

8

10

3

3

G_16220_024.eps

090206

Figure 4-3 IBO-zapper & SSB

G_16220_022.eps

090206

Figure 4-1 Cover shield

7

7

66

G_16220_023.eps

090206

Figure 4-2 Connector screws

1. Remove the rear cover from the set.

2. Very cautiously disconnect the LVDS cable [1] from the

SSB panel (see Figure “Cover shield”). Notice that this

connector is very fragile.

3. Unplug the black cable [2] going from the IBO zapper/SSB

to the Audio/STBY board.

4. Remove all other cables [3] from the IBO zapper/SSB.

5. Remove the fixation screws [4] that connect the top

shielding with the bottom shielding.

6. Remove the fixation screws [5] that connect the connector

plate to the frame.

7. Remove the fixation screws [6] that connect the shield to

the rear connector plate, see Figure “Connector screws”.

8. Remove the fixation screws [7] from the connectors.

9. Remove the connector plate from the shielding.

10. Remove the upper part of the shield (with the IBO zapper

attached to it) from the lower part of the shield (on which

the SSB is located), by unhooking it from its brackets.

11. Disconnect the antenna connector [8] from the tuner, see

Figure “IBO zapper & SSB”.

Figure 4-4 How to unlock an FFC connector

4.2 Set Re-assembly

To re-assemble the whole set, execute all processes in reverse

order.

Notes:

• While re-assembling, make sure that all cables are placed

and connected in their original positions.

Be careful with the fragile LVDS cable.

F_16040_038.eps

021105

Page 5

Service Modes, Error Codes, and Fault Finding

5. Service Modes, Error Codes, and Fault Finding

Index of this chapter:

5.1 Service Modes

5.2 Error Codes

Notes:

• Only information that is related to the IBO Zapper module

is published in this manual. For the other information, see

the relevant chassis manual (order code on front page).

5.1 Service Modes

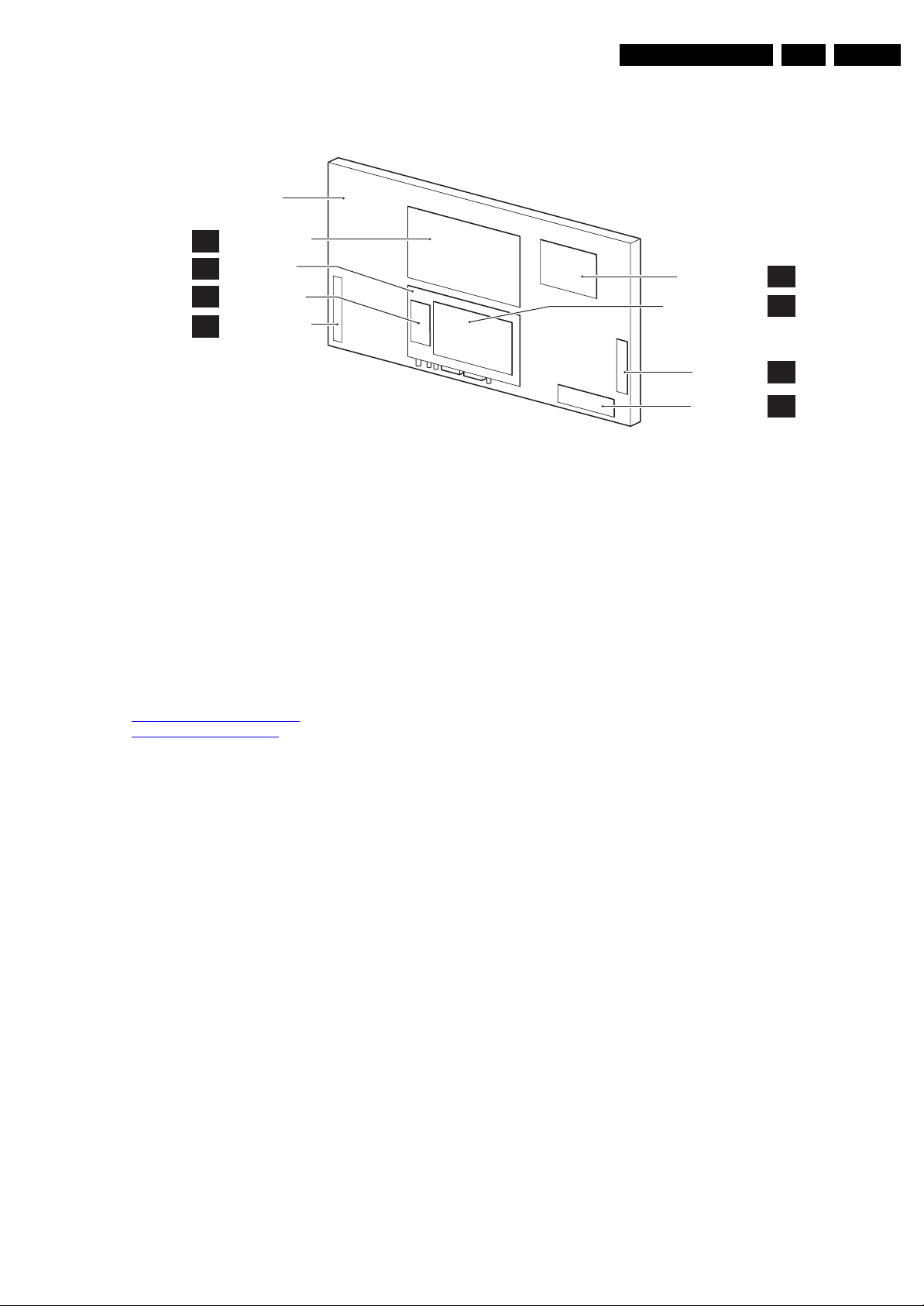

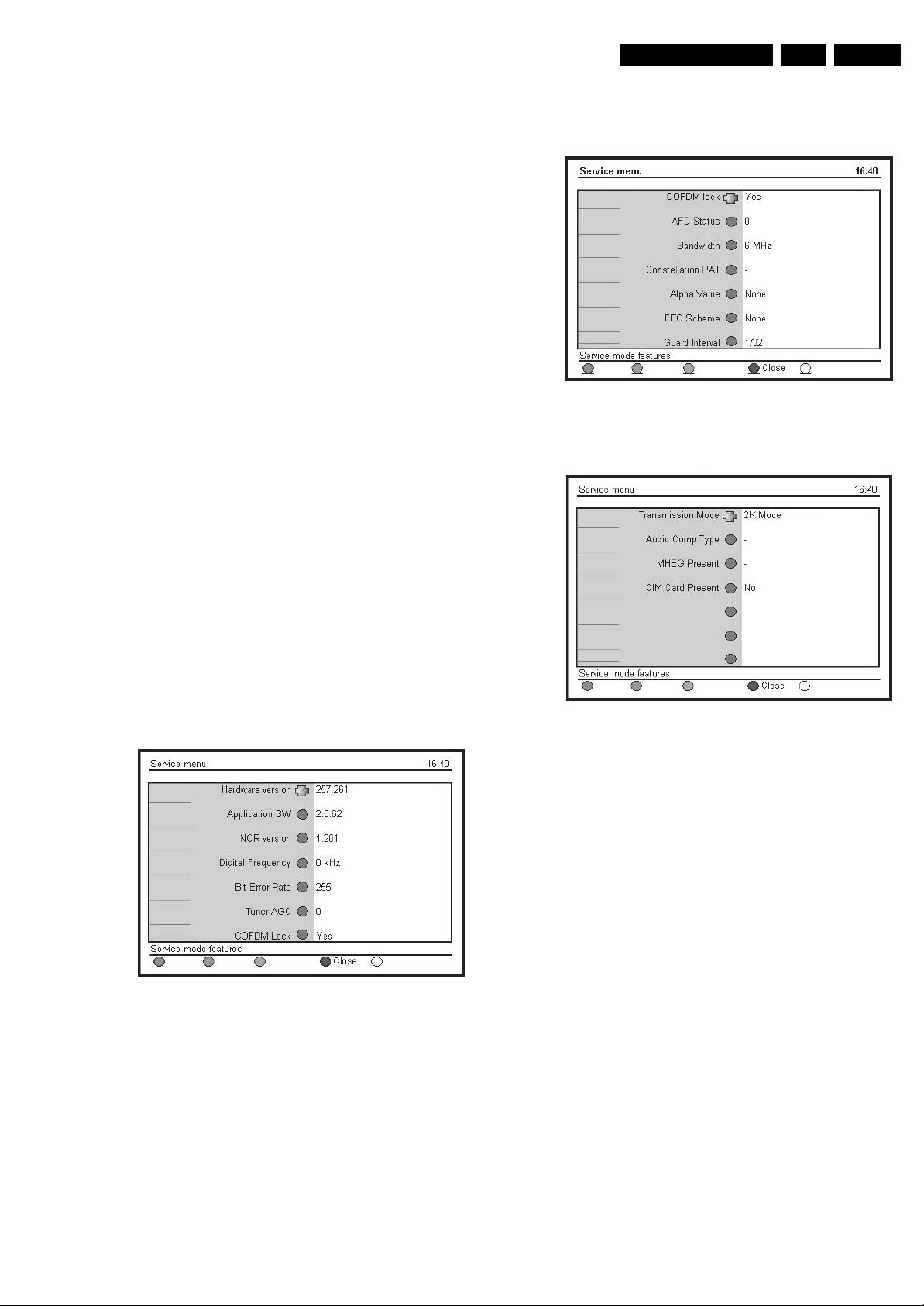

5.1.1 Digital Customer Service Mode (DCSM)

Purpose

The Digital Customer Service Mode shows error codes and

information on the IBO Zapper module operation settings. The

call centre can instruct the customer to activate DCSM by

telephone and read off the information displayed. This helps

the call centre to diagnose problems and failures in the IBO

Zapper module before making a service call.

The DCSM is a read-only mode; therefore, modifications are

not possible in this mode.

Figure 5-2 DCSM menu - 2

EN 5LC4.41E AB 5.

E_14970_041.eps

100904

How to Activate

To activate the DCSM, put the television in its digital mode (via

the A/D button on the remote control).

1. Press the “Digital” Menu button on the remote control to

activate the digital user menu (“Setup”).

2. Activate the “Information” sub menu (via the “down” and

“right” cursor buttons).

3. In the “Information” sub menu, press the following buttons

on the remote control to activate the DCSM:

“GREEN RED YELLOW 9 7 5 9”. Then, the “Service menu”

will appear (see figures below).

Menu explanation

E_14970_040.eps

090904

Figure 5-1 DCSM menu - 1

E_14970_042.eps

090904

Figure 5-3 DCSM menu - 3

1. Hardware version: This indicates the version of the IBO

Zapper module hardware.

2. Application SW: The application software version.

3. NOR Version: The NOR Flash image software version

4. Digital Frequency: The digital frequency that the set is

tuned to.

5. Bit Error Rate: The error rate measured before the error

correction algorithm circuitry. (this value gives an

impression of the received signal)

6. Tuner AGC: Tuner AGC value.

7. COFDM Lock: Indication if COFDM decoder is locked.

8. AFD Status: Status of the Active Picture Format

Descriptor.

9. Terrestrial Delivery System Parameters:

– Bandwidth: Bandwidth of the received signal.

– Constellation Pattern: Displays the signal

constellation.

– Alpha Value: Displays the Alpha Value.

– FEC Scheme: Displays the Forward Error Correcting

Scheme

– Guard Interval: Displays the value for the Guard

Interval.

– Transmission Mode: Displays the Transmission

Mode.

10. Audio Comp Type: Type of detected audio stream.

11. MHEG Present: Indicates if MHEG is present or not.

12. CIM Card Present: Indicates if CIM card is present or not.

How to exit

Press the BLUE button on the Remote Control to exit DCSM.

Page 6

EN 6 LC4.41E AB5.

Service Modes, Error Codes, and Fault Finding

5.2 Error Codes

The error code buffer contains all errors detected since the last

time the buffer was erased. The buffer is written from left to

right. When an error occurs that is not yet in the error code

buffer, it is displayed at the left side and all other errors shift one

position to the right.

5.2.1 How to Read the Error Buffer

You can read the error buffer in 3 ways:

• On screen via the SAM (if you have a picture).

Examples:

– ERROR: 0 0 0 0 0 : No errors detected

– ERROR: 6 0 0 0 0 : Error code 6 is the last and only

detected error

– ERROR: 9 6 0 0 0 : Error code 6 was detected first and

error code 9 is the last detected (newest) error

• Via the blinking LED procedure (when you have no

picture). See “The Blinking LED Procedure”.

•Via ComPair.

5.2.2 How to Clear the Error Buffer

The error code buffer is cleared in the following cases:

• By using the CLEAR command in the SAM menu:

– To enter SAM, press the following key sequence on the

remote control transmitter: “062596” directly followed

by the OSD/i+ button (do not allow the display to time

out between entries while keying the sequence).

– Make sure the menu item CLEAR is selected. Use the

MENU UP/DOWN buttons, if necessary.

– Press the MENU RIGHT button to clear the error

buffer. The text on the right side of the “CLEAR” line will

change from “CLEAR?” to “CLEARED”

• If the contents of the error buffer have not changed for 50

hours, the error buffer resets automatically.

Note: If you exit SAM by disconnecting the mains from the

television set, the error buffer is not reset.

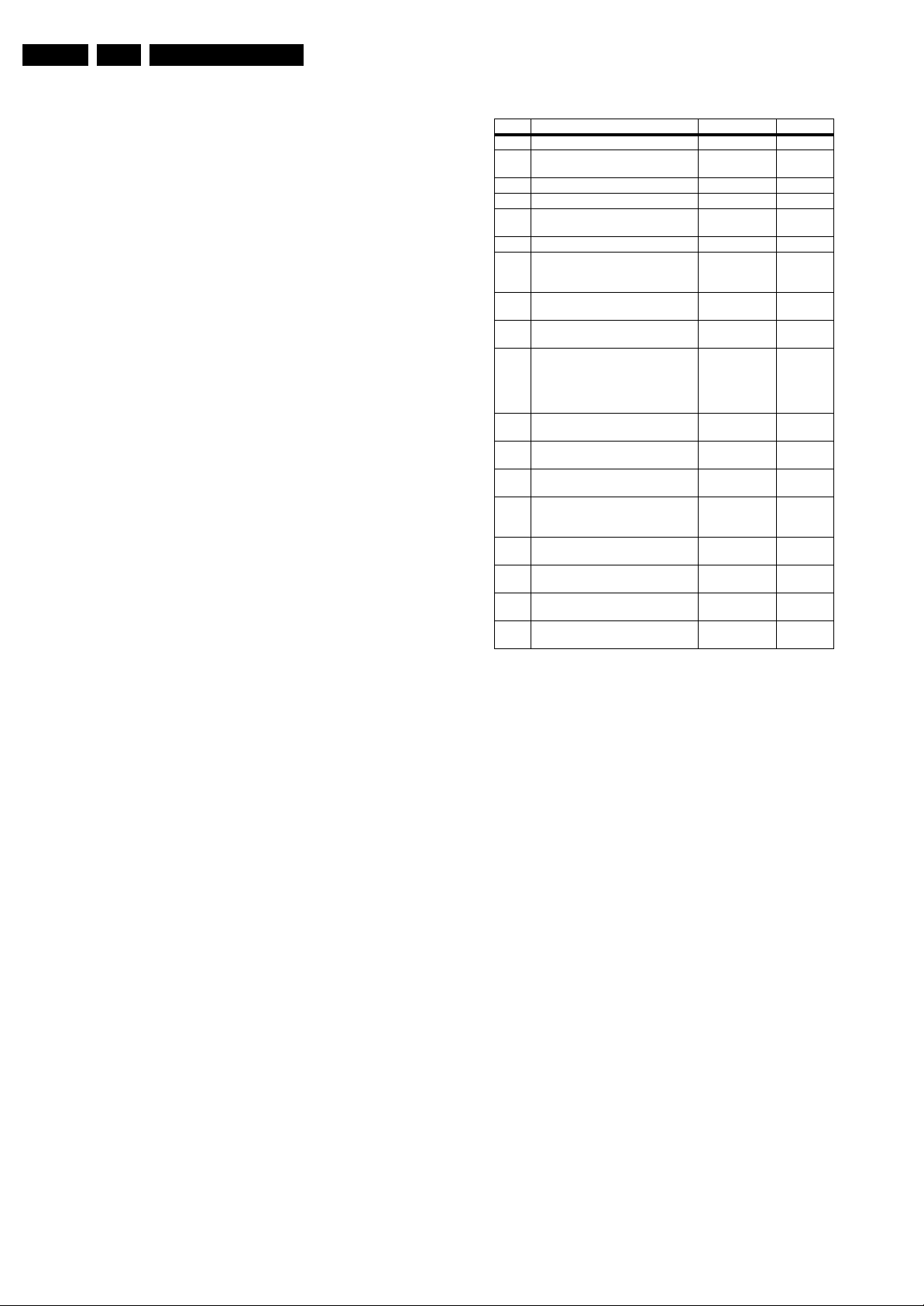

Table 5-1 Error code overview

Error Error Description Check Item Diagram

0No Error

1 Mis-match of TV (Hercules) SW and

Scaler SW

2 +12V from PSU error PSU A

3 Plasma I2C error (only for plasma sets) N.A. N.A.

4I2C error while communicating with the

Genesis Scaler

5 +5V protection 7752 B6

6 General I2C error; communication

between ADC, analogue tuner, and/or

Columbus I

7I

ADC

8I2C error while communicating with the

Scaler EEPROM

9I2C error while communicating with the

Hercules EEPROM (NVM for TV).

Remark: when the Hercules EEPROM

is defective, the Hercules should

operate with its default values.

10 I2C error while communicating with the

PLL tuner

11 I2C error while communicating with the

3D combfilter IC-7M00 (Columbus)

12 I2C error while communicating with

iBoard uP (only iTV sets)

13 I

HDMI decoder IC-7D03 (only for

NAFTA and AP)

14 Read-write error with the Scaler

SDRAM

15 I2C error while communicating with the

OTC

16 I2C error while communicating with

EPLD or Pacific III

17 I2C error while communicating with the

Digital Module (only for digital sets)

2

2

2

C failed

C error while communicating with

C error while communicating with the

Software

versions

7801 B7 + B8

1102, 7L01,

7M00

7L01 B18

7C01 B11

7207 B2

1102 B1

7M00 B19

N.A. N.A.

N.A. N.A.

7B01 B10

7001 T

7N00 B20 + B21

7100 K1

N.A.

B1 + B18 +

B19

5.2.3 Error Codes

In case of non-intermittent faults, write down the errors present

in the error buffer and clear the error buffer before you begin

the repair. This ensures that old error codes are no longer

present.

If possible, check the entire contents of the error buffer. In

some situations, an error code is only the result of another error

and not the actual cause of the problem (for example, a fault in

the protection detection circuitry can also lead to a protection).

Page 7

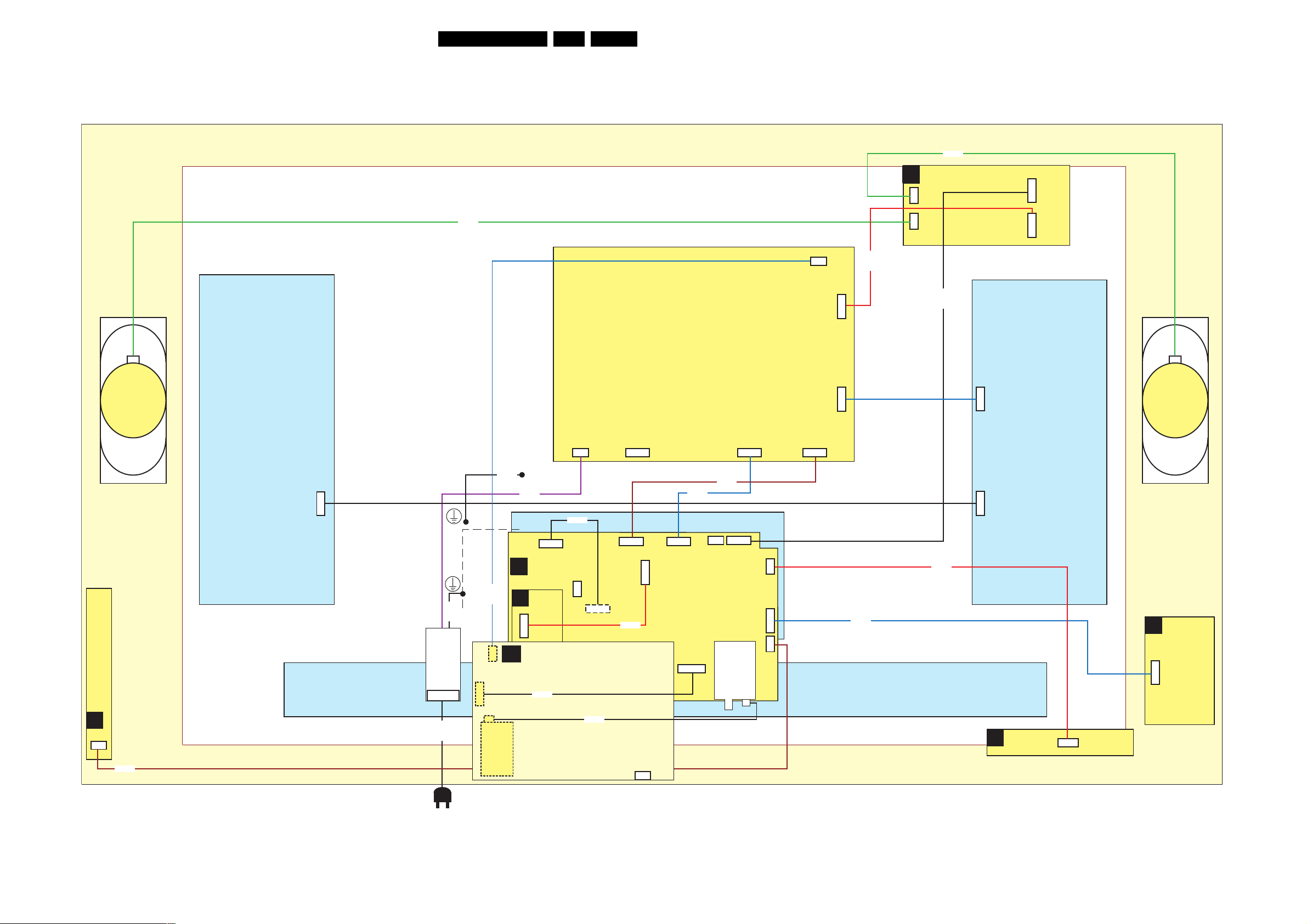

Block Diagrams, Test Point Overviews, and Waveforms

6. Block Diagrams, Test Point Overviews, and Waveforms

Wiring Diagram 42” (FHP)

WIRING 42” (FHP)

7LC4.41E AB 6.

8903

AUDIO

PLASMA PANEL

C

9P

2P3

1M03

1M01

RIGHT

SPEAKER

PDP Y-MAIN

DRIVING BOARD

9P12

CN5003

8902

8900

8192

CN308

2P3

8P06

POWER SUPPLY

0311

9P

PDP

8322

8337

1M03

10P

1M10

3P4

1M46

11P

1002

0323

7P

10P

8302

2P3

1M04

8152

7P

PDP X-MAIN

DRIVING BOARD

10P

CN23

8P11

CN22

1M02

LEFT

SPEAKER

CONTROL BOARD

E

1M01

3P

8101

FILTER

AC/Supply

8187

Shielding

8321

8188 UK

1500

1301

32P

TUNER

8301

3P

B

T

1000

K

31P

1N17

SSB

3P

OTC-

1N20

FLASH

14P

IBO ZAPPER2

8500

8600

31P

LVD S

11P

1J01

8000

1442

1402

3P

14P

10P

1J00

1G03

32P

3P

1J03

9P

1J04

TUNER

1K00

1K04

1K02

6P

11P

3P

8136

8870

LED PANEL

J

6P

1M01

SIDE I/O

D

11P

1M36

G_16230_001.eps

080306

Page 8

Block Diagrams, Test Point Overviews, and Waveforms

Wiring Diagram 42” & 50” Plasma

WIRING 42” & 50” PLASMA

8LC4.41E AB 6.

8903

AUDIO

PLASMA PANEL

C

9P

2P3

1M03

1M01

SPEAKER

CONTROL BOARD

E

1M01

3P

RIGHT

PDP Y-MAIN

DRIVING BOARD

9P12

CN5003

5P

FILTER

AC/Supply

8187

8902

Shielding

8321

8188 UK

1500

8302

1301

32P

TUNER

8900

B

8301

T

1000

IBO ZAPPER2

K

3P

SSB

OTCFLASH

14P

8500

9P10

5P

4P

7P

10P

31P

1N17

8P9

CN8003

CN8005

CN1M10

CN1M02

11P

CN1M03

8P06

1N20

CN1M46

8322

3P

31P

LVDS

8600

8337

11P

1J01

8000

PDP

POWER SUPPLY

CN8006

10P

10P

CN2026

10P

1J00

14P

1442

1G03

32P

3P

1J03

9P

1J04

TUNER

1K00

1K04

1K02

6P

11P

3P

CN8001

2P3

8136

2P3

1M04

8870

8152

7P

PDP X-MAIN

DRIVING BOARD

8P11

CN4004

LED PANEL

J

1M02

6P

1M01

LEFT

SPEAKER

SIDE I/O

D

11P

1M36

8101

1402

3P

G_16230_002.eps

010306

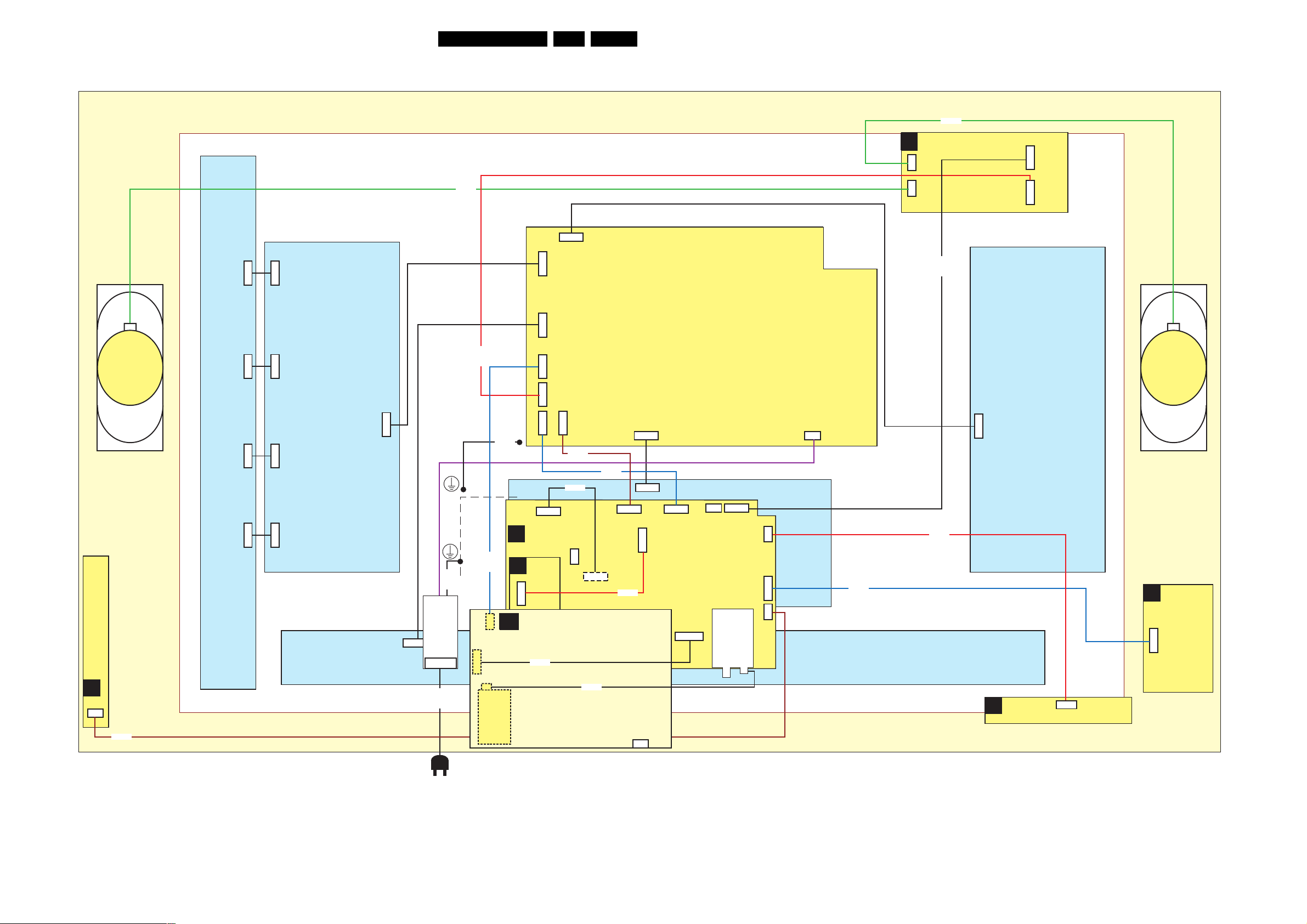

Page 9

Block Diagrams, Test Point Overviews, and Waveforms

Block Diagram Supply 42” FHP

SUPPLY42” FHP

FILTERS STANDBY

A2

0308

2

1

MAINS

INPUT

95-264Vac

400V_HOT

A5

I508

400V_HOT

PROTECTIONS

A3

+5V_INT_SW

- 2.5 Vref -

+5V_INT_SW

3304

7304

1

K

A

3

1400

T6.3A

4

R

2

7500

TNY256P

EN|UV

SOURCE

3324

DRAIN

2V5

5401

5005

5402

MAINS

FILTER

6513

6512

6511

6510

3506

3507

3035

3026

5

2

6501

6502

6506

1M05

1

2

IBO SUPPLY

(RES)

HOT GROUND

- VS PROTECTION -

3308

70-90V

3300

3301

7308 3+4

7

6

5

3306

4

3102

3307

+T

F500

I510

5500

2

4

1

1

2

RELAY CONTROL

ACTIVATING

6

7

8

9

3501

7501

TCET1102

2143

COLD GROUND

6312

3312

6313

2V5

A2

A2

PRECONDITIONER

0311

1

2

3

4

5

6

7

8

9

A5

6600

GBU8J

400V_HOT

TO CN11

PDP DISPLAY

F608

6605

6606

SUPPLY_ON

6503

6504

6505

1

K

7502

A

3

12

34

1450

ACTIVATING

DELAY

A6

F503

3505

2

R

3503

3450

+T

A7

+T

12

34

3509

3508

2505

5503

I514

1460

3451

6507

6507

-T

-T

7540

3452

3036

I504

F502

IN OUT

7461

COM

100-230VAC1

100-230VAC2

25V_HOT

+9V_STBY

+5V_STBY_SW

+5V_INT_SW

+3V3_STBY_SWVCC

I517

VCC

+3V3_STBY_SW

A2

A6

A3

A3

VRA

VRS

VCEGO

VSAGO

- VA PROTECTION - - VCC PROTECTION - - 12V PROTECTION -

2V5

3393

+12V

3302

3334

3335

7363

7366-1

7391

7366-4

7333 1+2

11

10

9

8

+5V_INT_SW

IAK

BUFFER

+5V_STBY_SW

STANDBY

VA

3311

3313

3317

VSAGO

VCEGO

+8V6

7308 1+2

11

10

9

8

6325

13

14

7375

7376

CONTROL

7352

7351

I905

VCEGO

+5V_INT_SW

7341

7004

7348

LATCH

+5V_INT_SW

7326

7327

UNDERVOLTAGE

PROTECTION

6321

3321

6322

+9V_STBY

3373

VSA

+5V_INT_SW

3349

3328

8V6

VCC

3320

3103

2V5

3322

3323

VSA_CONTROL

VCC_GO

LATCH

POK

7333 3+4

7

6

5

4

6333

3333

1

6334

2

A7

A7

3392

A6

F601

3608 3606

3666

3609

3603

3604

3605

3679

3682

I618

3651

6340

13

6341

14

SUPPLY_ON

5600

16

1246

3671

3104

3660

3661

3659

7608

3663

I620

14

3610

2663

7650

MC33368P

7

6

3

5

- DC_PROT -

3361

7362

3340

3364

6362

A6

7610

VCC

ZCDET

CS

FB

GATE

MULT

3358

6364

POWER_OK

5612

6661

12

11

STANDBY

I613

6611

3359

6365

9LC4.41E AB 6.

3675

F610

7661

MC34063D

6

VCC

1

SWC

7

IS

8

DCOL

3641

7640

3388

F600

5660

2

SWE

3677

5

I625

POK

DC_PROT

+5V_INT_SW

3389

7389

RES

1M03

1

2

3

4

5

6

7

8

9

10

400V_HOT

SW25V_HOT

6665

F609

7641

7642

6642

A7

A6

+12V_OVP

TO 1M03(1J00)

B16

PDP DISPLAY

2664

BIAS

2662

LLC SUPPLY

A6

25V_HOT

AUX SUPPLY

A7

7090

7091

7092

PROTECTION

SOFTSTART

CONTROL

CURRENT

PROTECTION

+30V

70-90V

3090

3092

&

7013

3089

3081

- CONTROL -

7001

MC34067P

15

VCC

14

OA

3

OSCCC

6

10

EAO

FI

8

lp

12

OB

7

ln

1260

T2A

1110

T5A

I105

1200

T2A

VCC_GO

A6

I220

+5V_INT_SW

7093

LM317T

IN OUT

COM

6002

3675

5260

I101

7110

3107÷3109

I213

I208

7202

6202

3095

3096

3097

F003

F004

7112

TEA1507P

CONTROL

1

VCC

3

CTRL

7200

3202

POK

F001

6111

3082

5001

4

2

DRAIN

ISENCE

DRIVER

3206

3203

3050

GND

DEM

3209

3084

SW25V_HOT

7007

7020

HIGH

6

SIDE

DRIVE

7

7008

7021

LOW

10

SIDE

DRIVE

9

12

7117

8

5

6

2

3113

4

6111

I214

3214

VA

7050

I200

SEQUENCE

DISCHARGE

400V_HOT

I038

I057

I083

7260

L4973V3.3

REGULATOR

7

VCC

8

VFB

3116 3117

I106

6113

2114

7212

TEA1507P

CONTROL

3

CTRL

4

DEMAG

1

VCC

GND

6211

6142

VS

6050

2053

7005

7006

HOT GROUND

OUT

3118

3115

DRAIN

DRIVE

6213

I202

2

3

5121

8

6

7052

7003

TCET1102

2143

5002

16

14

F005

3

12

11

6

10

9

5004

16

14

3

12

9

6

10

11

7002

TCET1102

2143

COLD GROUND

- +12V-SUPPLY -

5268

3269

- VA-SUPPLY -

+5V_INT_SW

7120

TCET1102

2143

- VCC-SUPPLY -

I236

7217

3149

3218

3213

3220

3053

+T

I201

3268

6133

3111

5220

1

4

5

7

3

+5V_INT_SW

LATCH

1084

T1.0A

6044

1082

T2.5A

1083

T2.5A

6029

7121

7130

14

13

12

11

8

14

7220

TCET1102

2

F293

F294

+12V

+8V6

VCC

+12V

VA

VCC

VS

VA

VCC

VCC

VA

VCC

F_16040_022.eps

240206

1002

1M10

1M46

0323

0342

0352

7

6

5

4

3

PDP AUDIO

2

1

1

2

AMBI LIGHT

3

4

IBO ZAPPER

1

2

3

TO (1J01)

5

6

7

8

9

10

1

3

4

5

TO CN23

6

PDP DISPLAY

8

9

10

1

3

4

TO CN42

PDP DISPLAY

5

7

1

4

TO CN52

5

PDP DISPLAY

7

TO 1M02

C

TO 1M10

AL

OR 1301

K3

1M46

B16

SSB

(RES)

(RES)

A3

6291

6642

3039

VRA

VSA_CONTROL

6226

5229

3228

7502

7042

7010

7011

A3

22942294

F016

3037

6042

VRS

FEEDBACK

6230

F116

1

K

2

R

A

3

5290

VS

2045

6045

2029

6021

3022

3080

6012

2269

2121

+30V

3111

VA

Adj.

3229

2021

3072

3057

3224

5293

5291

5292

VSND_POS

VSND_NEG

A2

A3

5225

7230

IN OUT

COM

DC_PROT

GND_SND

70-90V

VTUN

+30V

VRS

+12V

VCC

+8V6

VB

A2

VA

+5V_STBY_SW

VS

VTUN

+9V_STBY

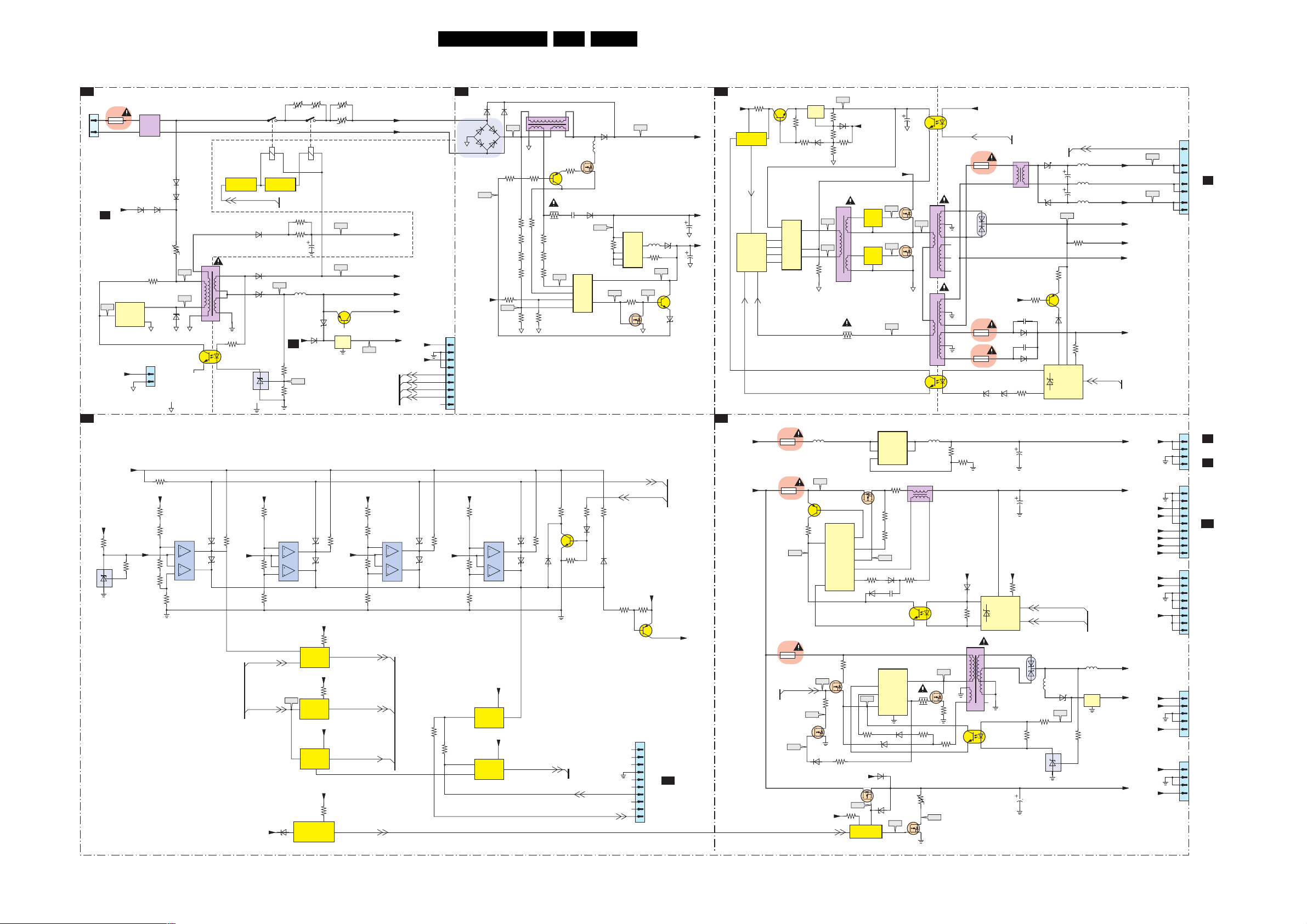

Page 10

Block Diagrams, Test Point Overviews, and Waveforms

Block Diagram Video

VIDEO

TUNER & VIF

B1

RF

IN

FR

OM

IBO-TUNER

K6

See also

Block Diagram

IBO-ZAPPER

SCART ANALOG IO

B15A

1

21

EXT 2

SCART 2

1

21

EXT 1

SCART 1

FROM 1500

K5

See also

Block giagram

IBO-ZAPPER

Fo

Sets Only

SIDE AV

D

VIDEO

IN

5

S-VHS

1G02

20

16

15

11

19

1G01

19

20

16

15

11

1G03

14

12

10

15

r DVB

1302

(1002)

1301

(1001)

1

2

SVHS

1152

UV1318S

7

8

7

8

8

+VTUN

+5SW_a

67

MAIN

TUNER

4

5

1

SCL

SDA

FBL_HSYNC_OUT

RGB-R|YC-C_IN

RGB-G_IN

RGB-B_IN

STATUS_2_IN|OUT

SC1_CVBS

_IN

SC1_FB

L_IN

CVI_Pr_IN

CVI_Y_

CVI_Pb_IN

STATUS_1

DMMI_CVBS_IN|Y_IN

DMMI_R_Pr_IN

DMMI_G_Y_IN

DMMI_B_Pb_IN

FBL_HSYNC_PIN16_IN

FRONT_YCVBS_IN

FRONT_C_IN

3

4

( ) 37” - 42” only

2156

11

IN

B2

IF-TER

3154

SC2_CVBS_MON_OUT

B2

B2

7G02

7G03

B15B

FBL_HSYNC_PIN16_IN

B2

B2

7G10

7G05

7G04

1304

(1M36)

2

4

1154

1

1156

1

SC2_Y_IN_1

SC2_Y_IN

FRONT_Y_CVBS_IN

SC2_C_IN

FRONT_C_IN

D

MMI_CVBS_

IN|Y_IN

AV2_DMMI_SW

EF

SC2_AV3_Y_IN

SC2_CVBS_MON_OUT

EF

SC1_CVBS_RF_OUT

DMMI

SC1_FBL_

CVI_Pr_IN

DMMI_R_Pr_IN

CVI_Y_IN

DMMI_G_Y_IN

CVI_Pb_IN

DMMI_B_Pb_IN

DMMI_RGB_SW

SC2_AV3_Y_IN

DMMI_CVBS_IN

DMMI_RGB_SW

SC2_Y_IN_1

EF

EF

EF

FBL_HSYNC_OUT

RGB-B_IN

RGB-G_IN

RGB-R|YC-C_IN

SIDE

B17

CONNECTIONS

1K01

(1K04)

FRONT_YCVBS_IN

2

FRONT_C_IN

4

4

VIF1

5

VIF2

RF_AGC

SIF1

4

SIF2

5

IN

2

1

12

13

3

5

4

2

7

9

14

12

17

19

5

3

12

9

2

19

B2

7G11

7G09

7G07

7G06

7217

TDA15021H

24

25

31

29

30

1,10,11,20

10,11

HERCULES

AC

DC

14

15

4

9

B7

SC2_OUT_SW

3

8

13

18

7G08

4

10,11

13

8

3

18

Sound

Traps

AGC

Detect

QSS Mixer

AM Demod.

SC2_Y_IN_1

SC2_AV3_C

_

IN

7206

EF

CVBS_COMB

7219

13

14

12

9

SC1_FBL_IN

SC1_CV1_DMMI_R_Pr_

SC1_CV1_DMMI_G_Y_IN

SC1_CV1_DMMI_B_Pb_IN

EF

OTC-FLASH (FOR 1000pg TXT)

T

7007

MSM51V18165F

FLASH

ROM

512Kx8

7006

M29W160ET70N6E

FLASH

ROM

512Kx8

CVBS1

QSS/FM

AM

_1

IN

58

59

64

51

52

48

55

43

DD(0-15)

AA(1-20)

Video

Switch

Control

B2

B2,B13

B2,B13

B2,B13

+

c

cvbs/y

7001

SAA5801H/015

CONTROL

HERCULES

Dig. 2H/4H

Combfilter

Y Delay Adj.

PAL/NTSC/

SECAM

Decoder &

Baseband

Delay

INSSW3

R/Pr-3

77 78 79 80

SC1_FBL_IN_1

SC1_CV1_DMMI_R_Pr_IN

CVBS_COMB

B3

B15b

(OTC)

83

TV

84

5

96

77

78

79

74

78

79

SCAVEM

on text

Yint

Chroma

Uint

Vint

RGB/Pr Pb Insert

YUV Interface

G/Y3

B/Pb-3

SC1_CV1_DMMI_G_Y_IN

SC1_CV1_DMMI_B_Pb_IN

B15b

B15b

B15b

CVBS_COMB

INT_OTC

R_OTC

G_OTC

B_OTC

RESET_FLASH

(Only For 37” - 50” Sets)

RGB Matrix

Blue & Black

Strech

Gamma Corr.

Skin Tone

SAT

U/V Tint

Saturation

YUV

Peaking

SCAVEM

U/V Delay

YUV in/out

H/V

YOUT

VOUT

UOUT

VIN

UIN

74 75 76 70 71 72

N.C.

INTF_V_OUT

INTF_U_OUT

INTF_Y_OUT

B3

1000

1442

11

H

22

V

44

55

77

99

11 11

12 12

13 13

SCL

14 14

SDA

RO

GO

BO

B_OSD

R_OSD

G_OSD

Fast Blanking

VDRB

Vertical &

East-West

Geometry

Sync Sep

H-OSC

HOUT

H-Shift

H-Drive

CVBS/Y

YIN

SYNC INTERFACE

(TO OTC-FLASH)

Hsync_SDTV

Vsync_SDTV

CVBS_COMB

INT_OTC

R_OTC_SDTV

G_OTC_SDTV

B_OTC_SDTV

RESET_FLASH

SCL

SDA

RO

85

GO

86

BO

87

22

VSYNC

HOUT

67

B13

B13

B2

B7

B13

B13

B13

B2

10LC4.41E AB 6.

7208

EF

7210

EF

For sets without

OTC-Flash (26”, 32”)

SYNC INTERFACE

B3

7436-2

7436-1

ADC

B18

7L61/7L62

EF

7L51/7L52

7L71

EF

SCART ANALOG IO

B15A

DIGITAL IO

B14

1

18 2

19

HDMI-1

1

18 2

19

HDMI-2

MUX-SYNC INTERFACE

B13

BINA|Pb

RINA|Pr

HDMI

27

3

7

25

1

5

5

1

13

12

7E01

7604

1

3

5

2

B10

B19

7E00

A2

A1

D1

R-PR-ADC

17

G-Y-ADC

14

B-PB-ADC

11

9

I_PC_HD_SEL

8

4

SDRAM

7B01

K4D263238F

SDRAM

1Mx32x4

COLUMBUS

(Dig. PAL/NTC Comb)

7M00

T6TU5XBG

COLUMBUS

DIGITAL COMB

7M01

MSM56V16

512Kx16x2

SC1_R_CVI_Pr_IN

14

SC1_G_CVI_Y_IN

15

SC1_B_CVI_Pb_IN

4

RGB|CVI_HDA_SEL

9

+2V5_DDR

FILTER

COL_A

DRAM

H_HDMI

V_HDMI

HDMI_VCLK

HDMI_Y(0-7)

HDMI_CbCr(1-7)

R_PR+

G_Y+

B_PB+

AVSY NC

AHSYNC

95

COL_DQ

FE00

7209

EF

B13

B13

B13

Vsync_SDTV

43

B3

B3

Hsync_SDTV

21

7L01

P3563M-LF

2

3

11

A/D

EF

7L72

VIN VOUT

COM

SCL

SDA

1G01

CONV.

6

9

37

38

B15b

B15b

B15b

B12

1F02

1

RX2+A

3

RX2-A

RX1+A

4

6

RX1-A

7

RX0+A

RX0-A

9

RXC+A

10

12

RXC-A

1F03

1

RX2+B

3

RX2-B

RX1+B

4

6

RX1-B

7

RX0+B

RX0-B

9

RXC+B

10

12

RXC-B

R_OTC_SDTV

FE01

G_OTC_SDTV

FE02

B_OTC_SDTV

SC1_R_CVI_Pr_IN

SC1_G_CVI_Y_IN

SC1_B_CVI_Pb_IN

Vsync_SDTV

Hsync_SDTV

COL_Di(1-9)

COL_YA(1-9)

SC1_CV1_DMMI_R_Pr_IN

SC1_CV1_DMMI_G_Y_IN

SC1_CV1_DMMI_B_Pb_IN

GINA|YINA

HDMI

7D03

SII9993CTG100

A9

A10

A12

A13

PANELLINK

A15

RECEIVER

A16

F16

G16

C10

C9

C13

C12

C16

C15

G14

F14

B7

SOG

FS D ATA

FSADDR

COL_Do(1-8)

COL_YB(1-8)

B13

B13

B13

B7

SCALER

7801

GM1501

C3

D2

C2

B2

L3

L4

C14

B14

D16

ANALOG

INPUT

PORT

FRAME

STORE

CONTROL

DVI/HDMI

INPUT

PORT

SCALER

GRAPHIC

ZOOM

OUT BLENDER

OSD CONTROLLER

BRIGHTNESS/CONTRAST/HUE/SAT

VIDEO

ZOOM

UART

INTERFACE

MICRO

CONTROLLER

INTERNAL

RAM

B9

SCALER

DISPLAY

TIMING

GEN.

EXTERNAL

ROM

INTERFACE

AE16

AF16

AE15

AF15

AE14

AF14

AF12

AF11

AF13

AE12

OCMDATA

OCMADDR

PAC IF IC 3

B20

TXB0TXB0+

TXB1TXB1+

TXB2TXB2+

TXB3TXB3+

TXBCTXBC+

OR

TXB0+

TXB0TXB1+

TXB1TXB2+

TXB2TXB3+

TXB3TXBC+

TXBC-

FLASH/CONTROL

B11

7C03

M29W400DT55N6E

FLASH

ROM

512Kx8

4N02

4N01

4N04

4N03

4N06

4N05

4N10

4N09

4N08

4N07

29

28

32

31

35

34

41

40

37

38

1N12

TXO0TXO0+

1N13

TXO1TXO1+

1N14

TXO2TXO2+

1N15

TXO3TXO3+

1N11

TXOCTXOC+

7N00

T6TF4AFG

LVDS

PACIFIC3

(RES For PIXEL+)

1N16

LVDS_VCC

LVDSALVD S A+

LVD S BLVD S B+

LVDSCLVD S C+

LVDSDLVD S D+

LVDSCLKLVDSCLK+

OR

LVDS_VCC

LVDSALVD S A+

LVD S BLVD S B+

LVDSCLVD S C+

LVDSDLVD S D+

LVDSCLKLVDSCLK+

TXO0-

103

TXO0+

102

TXO1-

101

TXO1+

100

TXO2-

99

TXO2+

98

TXO3-

93

TXO3+

92

TXOC-

96

TXOC+

95

1

11

12

13

14

15

16

17

18

19

20

24

25

26

21

22

1N17

1

11

10

12

14

13

15

19

18

20

27

26

28

22

21

23

G_16220_005.eps

070206

TO DISPLAY (26” & 32”)TO DISPLAY (LCD 37” & 42”, PDP 42” & 50”)

Page 11

Block Diagrams, Test Point Overviews, and Waveforms

Block Diagram Audio & Control

AUDIO

TUNER & IF

B1

1152

UV1318S

RF IN

SCART ANALOG-IO

B15A

B14

B15B

EXT 1

SCART 1

EXT 2

SCART 2

AUDI O

L/R IN

AUDI O

L/R IN

SIDE AV

D

AUDI O

L/R IN

HDMI 1

HDMI 2

FROM 1500

K5

See also

Block giagram

IBO-ZAPPER

1G01-1

1

6

2

21

1

1G02-1

6

2

21

1G02-2

1F01

1002

DIGITAL IO

1F02

1

19

DMMI

1G03

6

4

18 2

CONTROL

CONTROL BOARD

E

IR/LED/LIGHT-SENSOR

J

+5v2-STBY

3040

3051

3061

TUNER

4

5

SCL

SDA

AV1_Audio_INL

AV1_Audio_INR

DVI_D_AudioINL

DVI_D_AudioINR

1F03

1

18 2

19

DMMI_AudioINL

DMMI_AudioINR

Channel+

Channel-

Volume+

Volume-

7062

AV2_Audio_INL

AV2_Audio_INR

HD_AudioINL

HD_AudioINR

Menu

Power

1040

LED GREEN

IFOUT

B2

HDMI_A

HDMI_B

6070

LIGHT

SENSOR

6051

LED RED

6060

F158

11

SEL_IF_SDM

L

R

1703

1704

1705

1701

1702

1706

IR

SENSOR

IF-TER

B14

1M36

66

88

7051

7052

2156

6154

7151

DIGITAL IO

SIDE_AudioINL

SIDE_AudioINR

DMMI_AudioINL

DMMI_AudioINR

B17

1K04

B12

7D03

TDA9975

CONVERTER

KEYBOARD

LIGHT-SENSOR

+5V2-STBY

1156

4

1

2

5

3

7F03

74HC4052D

1

MULTI

PLEXER

12

4

11

5

14

2

15

10

DVI_D_AudioINL

DVI_D_AudioINR

SIDE CONNECTORS

SIDE_AudioINL

SIDE_AudioINR

HDMI

7D04

UDA1334ATS

HDMI

A5

1

A7

B7

3

2

1M01

22

0345

33

11

22

55

44

66

10-BIT

VIDEO

RC

LED1

LED2

Analog_AudioINL

3

Analog_AudioINR

13

9

Analog_AudioSEL1

Analog_AudioSEL2

HD_AudioINL

HD_AudioINR

DAC

HDMI_AudioINL

14

HDMI_AudioINR

16

SIDE CONNECTORS

B17

1K02

1K00

SIF1

SIF2

+3V3STBY

LED_SEL

PC-TV-LED

HERCULES

B2

7217

TDA15021H

29

30

33

34

35

B7

49

50

56

57

53

54

SYNC INTERFACE

B3

7430

AM

QSS Mixer

AM Demod.

QSS/FM

AD Conv.

Std Stereo

Decoder

I2S

Processor

AUDIO

SELECT

ADC/DAC

KEYBOARD

LSIPDP_DVB_SEMISTANDBY

3431

+3v3STBY

6430

+5VSW

3432

P50_LIN2_ITV_IR_SW_RST

RES

RC_OUT

AUDI O

CONTROL

Vol/Treb/

Bass

Features

DACs

4211

61

4212

60

103

105

106

36

37

62

HER_SC2_AudioOutL

HER_SC2_AudioOutR

63

DMMI_AudioINL

DMMI_AudioINR

HERCULES

B2

7217

TDA15021H

120

HERCULES

97

115

123

107

AUDOUTLSR

AUDOUTLSL

AUDIO DELAY LINE

B4

(LIPSYNC)

7503

M74HC590

I2SCLK

COUNTER COUNTER

7502

CY62256LL

7505

74HC573

I2SDO1

7506

74HC573

I2SDI1

SEL_IF_SDM

114

SERVICE

STATUS_1

116

STATUS_2

119

102

SOUND-ENABLE

111

SC_STANDBY

122

AV2_DMMI_SW

127

98

TV_SC_COM

99

10

11

11LC4.41E AB 6.

RAM

32kx8

LATCH

LATCH

7G07

2

1

12

13

4204

4205

SDM

EXT_MUTE

TV_IRQ

1202

24M576

7501

M74HC590

10

15

14

AUDIO PROCESSING

B5

OUT_MUTE

DMMI_SC2_REC_SEL

B6

B1

B15A

B15A

B5

B5

B6

B15B

B15A

B15B

B7

B7

PAN

B8

B2

AUDIO-R

AUDIO-L

SOUND-ENABLE

7601

TS482ID

2

1

7

6

OUT_MUTE

7602

74HC08PW

3

6

OUT_MUTE

8

7201

MUTE

7202

MUTE

DC-DC CONVERTER

+12VSW

EL-PWR-CTL

SC_STANDBY

7755

&

&

&

B16

2

1

5

9

10

3758

+3V3STBY

1J04

SC2_L_MON_OUT

SC2_R_MON_OUT

7756

C2

C1

1M01

11

33

88

HP_DET_R_DC_1

SOUND_ENABLE

POWER_DOWN

EXT_MUTE

SC1_L_RF_OUT

SC1_R_RF_OUT

5756 5757

7606

3755

3759

ADAC1

ADAC2

MUTE

SC1_L

SC1_R

SC2_L

SC2_R

7754

3750

AUDIO: AMPLIFIER

7D10-02

7D10-3

FEEDBACK

MUTE

SOUND-ENABLE

MUTE

INV-MUTE

SIDE

B17

CONNECTORS

HP_ROUT

HP_DET_R_DC_1

B2

B16

B2

7758

SCART ANALOG-IO

B15A

PAN_VCC

LVDS_VCC

5700

+3V3SW

7D19÷7D21

7D26

HP_LOUT

7D14÷7D16

CONTROL

CONTROL

CONTROL

+12_20V

7D18

7D18

-12_20V

FEEDBACK-LR

FEEDBACK-RL

+12_20V

7D23

7D23

-12_20V

D

1K01

1K04

10 10

12 12

11 11

7D10-01

7D10-04

U-VOLT-DETECT

SIDE AV

SOUND_L-HEADPHONE-OUT

SOUND_R-HEADPHONE-OUT

DETECT

SC1_L_RF_OUT

SC1_R_RF_OUT

SC2_L_MON_OUT

SC2_R_MON_OUT

7D11

7D25

CONTROL

C2

PROT-AUDIOSUPPLY

+12_20V

CONTROL

-12_20V

AUDIO:

CONNECTORS

LEFT-SPEAKER

5M09

5M12

5M09

5M11

RIGHT-SPEAKER

1G01-1

3

1

1G02-1

3

1

1010

7

1

2

21

EXT 1

SCART 1

21

EXT 2

SCART 2

1M03

1M02

1M04

1

1

1

3

LEFT

SPEAKER

7

TO

6

PDP

SUPPLY

5

3

2

1

1

3

RIGHT

SPEAKER

HEADPHONE

G_16230_003.eps

010306

Page 12

Block Diagrams, Test Point Overviews, and Waveforms

Block Diagram IBO Zapper

IBO - ZAPPER 2 PANEL (DVB)

FRONT END

K6

FROM

MAIN TUNER

B1

SSB

I2C_TDA_SDA

I2C_TDA_SCL

+5V

K1

3634

dsp_EEPROM_WP

1700

1

35

68P PCMCIA CONN

34

68

3626

3612

7

M24C256

EEPROM

RF-IN

56

7602

1600

TD1316L

+5V+5V

3607

3627

3633

PCMCIA-D (0-7)

8

9

3606

K7

K7

K7

+5VClean

5602

11

TUNER

10 5 13

AGC

XTAL

7601-1

LM393D

2

3

I2C_LOCAL_SDA

I2C_LOCAL_SCL

7605

74AHC1GU04GW

2

INVERTER

7606

74AHC1GU04GW

2

INVERTER

A_MD (0-7) + A_MDO (0-7)

CONTROL LINES

7701

74LVC573ADB

7702

74LVC573ADB

7703

74LVC245A

RESET_FE-N

K1

14

15

CONTROL

LATCH

CONTROL

LATCH

CONTROL

BUS

TRANS

CEIVER

IF-AGC

AGC-TUN

1

COMB-OUT

4

4

IF1

IF2

3630

3631

3625

3629

X-IN

4MHz_MOJO

MIU_ADDR (0-7)PCMCIA-A (0-7)

MIU_ADDR (8-14)PCMCIA-A (8-14)

MIU_DATA (0-7)

7600

TDA10046HT

9

62

61

DECODER

2

1

21

4

COFMD

3

8

6

54

COFDM

CHANNEL

K1

38

TDA_DAT (0-7)

TDA_CLK

37

TDA_VALID

36

TDA_SYNC

35

UNCOR

33

FE_LOCK

25

MIU_ADDR (15-24)

K7

VCCEN

FLASH MEMORY

K2

K7

K7

K1

7705

ST890C

3

7704

FXO-31FT

8

CURRENT

6

SWITCH

OSC

27MHz

I2C_LOCAL_SCL 31

I2C_LOCAL_SDA 30

COMMON INTERFACE

7700

STV0700

MPEG

TS

50

IN

48

49

CONTROLLER

PCMCIA_5V

FAULT

12

INTERRUPT

MANAGEMENT

35

3700

3701

INTERFACE

TS

INTER

FAC E

PCMCIA

UCSG

ICC

+5V

TS

OUT

12LC4.41E AB 6.

TS_DATA (0-7)

TS_CLK

63

TS_SYNC

62

TS_VALID

61

FE_LOCK

K6

K1

MOJO

7100

PNX8316HS

TS

29

IN

30

28

34

AV

MOJO

I2C

GPIO

AV

GPIO

I2C

202

203

204

205

172

165

163

167

180

181

182

9

206

198

199

201

200

ANALOG BACK END

K5

3135

3134

3133

3164

8

15

14

MOJO_I2S_OUT_SD

MOJO_I2S_OUT_SCK

MOJO_I2S_OUT_WS

MOJO_SYSCLK 6

INTERFACE

K4

C_CVBS

G/Y

B/Pb

R/Pr

AR1

AR2

SPDIF

USB_OVRCUR

USB_PWR

USB_DM

USB_DP

+5V_USB

7502

UDA1334ATS

3

1

2

2

7

1

3420

3421

16

AUDI O

DAC

14

5511

5511

FILTER

FILTER

5512

FILTER

5513

FILTER

5514

FILTER

7403

LM3525

Power Switch and

Over-current

Protection

7521÷7523

7524÷7526

7527÷7529

7518÷7819

TXDO

RXDO

6,8

7500

7501

7503

7504

7512 7511

7507

7520

7402

EF

CVBS_VCR

GREEN/Y

BLUE/U

RED/V

I2C_TV_SDA

I2C_TV_SCL

TV_IRQ

TV_IRQ

VBUS

USB_D-

USB_D+

1500

R1

L1

4

6

8

12

10

14

1

2

3

25

1401

1402

1403

1

2

3

4

TO 1G03

B15B

LC4.x (EUR)

SPDIF

OUT

UART

1

CONN.

2

FOR

COMPAIR

3

ONLY

CONNECTOR

(Reserved)

USB

7200

M29W320DT

EPROM

NOR

FLASH

I2C_LOCAL_SDA

I2C_LOCAL_SCL

MIU BUS

7201

M58LWO32A

NOR

FLASH

(optional)

3209

5

7203

M24C64

EEPROM

8KX8

3207

3206

3210

6

7

7202

K4S281632F

SYNC

DRAM

4x2Mx16

3211

user_EEPROM_WP

MIU_ADDR

MIU_DATA

SDRAM_DATA

SDRAM_ADDR

185

7

6

GPIO

MIU

SDRAM

POWER SUPPLY

K3

+12V

+3V3

5309

1304

F500mA

5301

5304

5306

7306

NCP303LSN30

POWER

12

ON

RESET

7300

MC34063AP1

SUPPLY

7303

MC34063AP1

26

SUPPLY

7305

MC34063AP1

SUPPLY

RESET_n

K1 K2

1301

+12V

+12V_A

5300

26

6300

5303

6303

5305

26

6304

2311

7311

7309

7310

CONTROL

7301

LD1117V18

IN OUT

COM

7302

LD1117V18

IN OUT

COM

7307

LD1117V50

IN OUT

COM

7308

LD1117V50

IN OUT

COM

5302

+3V3

+3V3

+1V8FE

+1V2_MOJO

+5V

+5V

G_16220_007.eps

CLEAN

CLEAN

070206

1

2

3

TO X220

OR 1M10

PSU

Page 13

I2C Overview

I²C

HERCULES

B2

7217

TDA15021H

HERCULES

SET

PROCESSOR

Block Diagrams, Test Point Overviews, and Waveforms

SCALER

B8

109

108

ERR

6

NVM_WP_HERC

104

+3V3STBY

3233

3232

+3V3STBY

3249

56

7207

M24C16

EEPROM

7

NVM

ERR

9

7221

+3V3SW

+3V3SW

3298

7220

3297

SDA

SCL

N1 N2

7801

GM1501H

SCALER

ERR

4

ADDRESS

DATA

ADDRESS

DATA

M1

M2

P3

P4

AF5

AF7

AD6

+3V3STBY

3902

B7

3838

3901

SCALER

+3V3SW

3817

3818

NVM_WP_SCALER

OCMADDR

OCMDATA

+3V3_IO

3837

JTAG_TDI_SDA

JTAG_CLK_SCL

FSADDR

FSDATA

TUNER & IF

B1

3102

54

1102

UV1318S

TUNER

ERR

10

3172

UART_TX

3173

UART_RX

FLASH / CONTROL

B11

5

7C01

M24C32

7

EEPROM

7C03

M29W400D

ERROM

1802

2

1

JTAG

I2C

3101

SDA_IO

SCL_IO

ERR

8

B10

3152

+3V3STBY

3170

6

3151

3171

SDRAM

7B01

K4D263238F

SDRAM

ERR

13LC4.41E AB 6.

1151

1

SDA

2

SCL

3

SERVICE

CONNECTOR

COMPAIR

1177

1

2

3

SERVICE

CONNECTOR

UART

14

B19

B12

COLUMBUS

3M14

3M15

B15

A15

7M00

T6TU5XBG

COLUMBUS

CTRL

ERR

11

HDMI

B3

3D05

3D06

74

75

K16

7D03

SII9993CT

PANELLINK

RECEIVER

B9

K15

HDMI

J16

ERR

13

J15

SCALER INTERFACE

7A00

PCA9515ADP

3

2

4A01

4A00

SYNC INTERFACE

+5VHDMI_A

3D09

+5VHDMI_B

3D10

5

7D01

M24C02

EEPROM

256x8

6

7

RES

1442

3D01

3D03

6

1000

14 14

13 13

B18

5

7D00

M24C02

EEPROM

256x8

T

6

OTC-FLASH

ADC

3L19

38 37

7L01

P3563M

ADC

ERR

7

DIGITAL I/O

B14

DOC_SDAA

DOC_SCLA

DOC_SDAB

DOC_SCLB

3L18

1F02

16

15

1F03

16

15

2x HDMI

CONNECTOR

3016

3015

86 85

7001

SAA5801H/

TV

CONTROL

ERR

15

(Only For 27” - 42” Sets)

PACIFIC3

B20

4N30

4N31

198 200

7N00

1

18 2

19

T6TF4AFG

PACIFIC3

MISC

ERR

SDA_DMA_BUS1_DISP

SDA_DMA_BUS1_DISP

SDA_PF3

SCL_PF3

+3V3SW

1N04

3N20

SDA

SCL

FOR

DEVELOPMENT

USE ONLY (N.S.)

1

2

3

4

3N21

+3V3SW

1N03

1

SSDA

202

SSCL

204

SPI_SO

192

SPI_SCK

191

SPI_CS

194

16

188

187

193

SPI_WP

SPI_RST

2

3

4

FOR PACIFIC3

PROGRAMMING (N.S.)

5

6

7N02

M25P05

1

3

Flash

7

2

1N17

(1G50)

31

30

TO

DISPLAY

512k

SPI_SI

112

113

SWHW_I2C_SDA

SWHW_I2C_SCL

B15B

ERR

17

DMMI

1G03

11

22

For DMM I

IBO ZAPPER2

ANALOGBACKEND

K5

1500

3513

3512

(Only For DVB Sets)

I2C_TV_SDA

I2C_TV_SCL

K6

3607

TD1316L

DIGITAL

FRONT END

I2C_TDA_SDA

I2C_TDA_SCL

3606

8

9

1600

TUNER

3632

5

7602

M24C256

EEPROM

3633

RES

+5V

3626

6

3627

3625

3630

3631

86

43

7600

TDA10046

COFDM

CHANNEL DECODER

3629

K1

3147

98

MOJO

3144

3146

76

7100-6

PNX8316HS

MOJO

(I2C-USB-SCO)

I2C_local_SDA

I2C_local_SCL

3143

FOR PDP ONLY

(Depending on screen manufacturer)

7100-7

PNX8316HS

MOJO

(GPIO)

15

14

K4

TXD0

RXD0

INTERFACE

1402

1

2

FOR COMPAIR

3

UART

CONNECTOR

K2

FLASH

MEMORY

3209

3210

56

7203

M24C64

EEPROM

8kx8

3207

+5V

3206

K7

COMMON

INTERFACE

3701

3700

30 31

7700

STV0700

PCMCIA

CONTROLLER

(OPTIONAL PIXEL+)

G_16220_008.eps

090206

Page 14

Block Diagrams, Test Point Overviews, and Waveforms

Supply Voltage Overview

SUPPLY LINE OVERVIEW

14LC4.41E AB 6.

PDP

POWER SUPPLY

PANEL (PSU)

CN8001

1M46

1M03

TO 1301

1M10

ZAPPER2

TO 1M02

1M02

AUDIO

TOP CONNECTORS

B16

1J02

1

2

3

4

5

6

7

8

9

10

11

12

1J01

(1M46)

1

2

3

N.C

.

1J07

4

5

N.C

.

6

1J08

7

8

N.C

.

9

10

N.C

.

4J01

11

1J00

(1M03)

1

2

N.C

.

3

4

5

6

N.C

.

7

8

9

N.C

.

10

RES

K3

IBO

C2

POWER_DOWN

STANDBY

BACKLIGHT_CTRL

LAMP_ON_OFF

+12VUFD

+5V_UFD

UFD CONTROL

BACKLIGHT_CTRL

LAMP_ON_OFF

FAN_SPEED

STANDBY

PRO

TECT_AUD

POWER_UP_OK

5J03

5J04

VP

+3V3STBY

+12VSW

+5V

B3,B6

B5,B6,B9

B6,B16

TUNER & IF

B1

B6

B16

B6

B6

B6

B6

B6

B16

B6

B6

B6

B6

B6

B6

B16

B6

B6

B6

B8

B8

B6

B8

B8

+5VSW

5152

5153

+VTUN

+3V3STBY

HERCULES

B2

+3V3STBY

3265

7215

3264

7216-1

3263

7217

3262

7216-2

+5VSW

+8VSW_TV

+3V3SW

SYNC INTERFACE

B3

+3V3STBY

+3V3SW

+5VSW

+5V

+12VSW

AUDIO DELAY LINE (FOR PDP SETS ONLY)

B4

+5VSWI

5501

AUDIO PROCESSING

B5

+3V3SW

+3V3STBY

+5VSW

+5V

SCALER

B7

+1V8_CORE

+2V5_DDR

+3V3SW

+3V3_IO

+3V3_PLL

+5VSW

+5VSW_a

+5VSW_b

+VTUN

+3V3STBY

+3V3STBY

+1V8_A

+1V8_B

HERCULES

+5VSW

+8VSW_TV

+3V3SW

+3V3STBY

+3V3SW

+5VSW

+5V

+12VSW

+5VSWI

+5VD

+3V3SW

+3V3STBY

+5VSW

+5V

+1V8_CORE

+2V5_DDR

+3V3SW

+3V3_IO

+3V3_PLL

B16

B16

B6

B16

B6

B6

B6

B16

B6

B16

DC-DC CONVERTER

B6

+12VSW

5709

3718

STEP

DOWN

CONTR

SC_STANDBY

+5V

5704

SCALER

B8

+3V3STBY

+3V3SW

SCALER INTERFACE

B9

+3V3SW

+3V3STBY

+5VSWI

+5V

(Supply to Tuner & Hercules)

7738

5738

IN OUT

COM

7752

5752

DC/DC

Converter

7730

5730

PWR

REG

5757

7754

PANEL-PWR-CTL

(For 37”-50” Large Screen)

7758

5717

7758

7708

IN OUT

COM

5900

5901

5902

5903

5904

5905

5906

5907

7900

5908

IN OUT

COM

7901

IN OUT

COM

+8VSW_TV

5753

5754

6735

5733

5737

(For 26”-42” Screen)

LVD S_VCC

5700

5713

7754

+3V3STBY

+3V3STBY

3V3_ADC

3V3_LBADC

3V3_LVDSA

3V3_LVDSB

3V3_LVDS

+2V5_DDR

+1V8_ADC

5909

+1V8_DV1

5910

+1V8_CORE

5911

+3V3STBY

+12VSW

+5VSWI

+VTUN

+5VSW

PAN _VCC

+3V3SW

+5V

+3V3SW

3V3_PLL

3V3_DVI

3V3_IO

+1V8

+3V3SW

+5VSWI

+5V

B14

B14

B6,B16

B6,B16

B8

B2

B15b

B8

B4,B9,B19

B13

B6

B1

B1,B2,B3,B5

B15a,B15b,

B17

B20

B6

B2,B3,B5,B7,

B8,B9,B11,B12

B13,B19,B20

B6

B1,B2,B3,B5,

B8,B9,B15b

B6

B6

B7

B7,B11

B6

B7,B10

B18

B6

B6

B7

B6

SDRAM

B10

+2V5_DDR

FLASH / CONTROL

B11

+3V3_IO

+3V3SW

HDMI

B12

+5VHDMI_A

+5VHDMI_B

+3V3SW

MUX-SYNC INTERFACE

B13

+3V3SW

+5VSWI

DIGITAL IO

B14

+5VSWI

1F02

18

DVI

1F03

18

DVI

SCART ANALOG IO

B15A

+5VSW

DMMI

B15B

+3V3STBY

+5VSW

+8VSW_TV

SIDE CONNECTORS

B17

+3V3STBY

5K00

+5VSW

5K01

3B01

5D06

5D00

5D01

5D02

7D02

IN OUT

COM

5D05

5D03

5D04

+3V3STBY_1

+5VSW_1

+2V5_DDR

FSVREF

+3V3_IO

+3V3SW

+5VHDMI_A

+5VHDMI_B

+3V3SW

VDDA_3V3PLL

VDDA_3V3

VDDD_3V3

VDDI_3V3

VDDC_1V8

VDDA_1V8

VDDD_1V8

+3V3SW

+5VSWI

+5VSWI

+5VHDMI_A

+5VHDMI_B

+5VSW

+3V3STBY

+5VSW

+8VSW_TV

+3V3STBY

1K00

+5VSW

1K01

B19

B8

B6

B6

B6

B6

1442

B3

C2

B12

C2

B12

C2

1M02

PSU

1J04

B16

5

K3

K3

1304

7

K3

ADC

B18

+5VSWIA

+2V5_DDR

COLUMBUS

B19

+3V3SW

+5VSWI

PACIFIC3

B20

+3V3SW

LVDS_VCC

OTC-FLASH (FOR 1000pg TXT)

T

1000

6

AUDIO: CONNECTORS

C1

AUDIO: CONNECTORS

C2

1M02

5M10

1

5M11

2

5M12

5

5M09

6

1M01

7

IR / LED / LIGHT-SENSOR

J

1870

5

MOJO

K1

+1V2_MOJO

3V3clean

D

+3V3

(ONLY FOR DVB SET)

7L02

IN OUT

COM

5L21

5M03

5M04

5100

7N04

IN OUT

7N03

IN OUT

5001

FLASH MEMORY

PSU

K3

K3

37”

K3

N.C.

K3

K3

K3

K3

K3

K3

K3

K3

K3

K3

K2

+3V3

(ONLY FOR DVB SET)

K3

1301

1

B18

(ONLY FOR DVB SET)

K4

+3V3

+5V_USB

(ONLY FOR DVB SET)

K5

+3V3

+3V3clean

+5Vclean

+12V_A

(ONLY FOR DVB SET)

K6

+1V8FE

+3V3

C1

C1

+5Vclean

C1

(ONLY FOR DVB SET)

K7

+3V3

(ONLY FOR DVB SET)

5201

5200

+5V

POWER SUPPLY

5309

7300

MC34063AP1

1304

6

SUPPLY

7303

MC34063AP1

5304

6

SUPPLY

7305

MC34063AP1

5306

6

SUPPLY

INTERFACE

ANALOG BACK END

FRONT END

5801

+5V

COMMON INTERFACE

5703

5704

7705

1

CURRENT

SWITCH

5702

7

+5V

+3V3

+3V3_NOR48

+5V

+12V

+12V_A

K5

7311

7301

IN OUT

COM

7302

IN OUT

COM

7307

IN OUT

COM

7308

IN OUT

COM

PCMCIA_AVCC

+3V3

3V3clean

5302

+1V8FE

+1V2_MOJO

+5V

+5Vclean

+3V3

+5V_USB

+3V3

+3V3clean

+5Vclean

+5V_amp

+12V_A

+1V8FE

+3V3

+3V3_FE

+5V

+5Vclean

+3V3

+3V3_STV

+3V3_CORE

+3V3_BUF

+5V

PCMCIA_5V

PCMCIA_VPP

K1,K2,K4,

K5,K6,K7

K1,K5

K6

K1

K2,K5,

K6,K7

K6

5300

2

5303

2

5308

2

5515

5700

5701

+5VSWIA

+3V3SWB

VDDP

5L01

VAD C

5L11

VPLL

5L17

VMPLL

5L19

+2V5_DDR

VDDC

1M10

+3V3SW

+3V3SWA

+5VSWI

+5VSWIA

+3V3SW

5N04

5N05

5N03

7D24

+1V5

1V5CORE

+1V5PLL

+2V5PLL

+2V5VDD

LVDS_VCC

+3V3SW

+3V3_INTOTC

(OPTIONAL)

-12_20V

+12_20V

VN

VP

+3V3-STANDBY

-12_20V

+12_20V

+3V3-STANDBY

+3V3STBY

+1V2_MOJO

3V3clean

+3V3

+3V3_MOJO

COM

5N06

COM

5D16

3D43

G_16230_004.eps

010306

Page 15

Circuit Diagrams and PWB Layouts

7. Circuit Diagrams and PWB Layouts

IBO Zapper Panel: MOJO

1234567891011121314

RES

K1

A

MIU_WEN

K1

K2

NOR_RYBY

B

RESET_n

K3

4MHz_MOJO

K6

C

D

E

F

G

H

I

TS_DATA(0)

K7

TS_DATA(1)

K7

TS_DATA(2)

K7

TS_DATA(3)

K7

TS_DATA(4)

K7

TS_DATA(5)

K7

TS_DATA(6)

K7

TS_DATA(7)

K7

K5

MOJO_I2S_OUT_SD

K5

MOJO_I2S_OUT_SCK

K5

MOJO_I2S_OUT_WS

K4

SPDIF

K5

MOJO_SYSCLK

I2C_LOCAL_SCL

K2, K6, K7

K2, K6, K7

I2C_LOCAL_SDA

K5

I2C_TV_SCL

I2C_TV_SDA

K5

USB_OVRCUR

K4

USB_PWR

K4

USB_DM

K4

USB_DP

K4

3139 123 6147.1

MOJO

7100-2

PNX8316HS

0

1

2

3

TS_DATA

4

5

6

7

SD_OUT

SCK_OUT

WS_OUT

SPDIF

FSCLK

4101

3

10K

F135

1

(TS)

7100-3

PNX8316HS

(AV)

2

7104

BSN20

TS_SYNC

TS_STROBE

3

10K

3145

RES

+3V3_MOJO

TS_VAL

CVBS

CVBS

CVBS

4100

2V2

20

2V2

21

2V2

22

2V2

23

2V2

24

2V2

25

2V2

26

2V2

27

1V

3135

3134

3133

202

22R

0V

203

22R

1V6

204

22R

206

100R3142

3164

205 165

22R

RES

F136

3148

RES

1234567891011121314

+3V3

Y

C

Y

B

G

Y

R

C

7103

BSN20

1

+3V3_MOJO

3114

3138

0V

30

1V6

29

1V3

28

168

0V

172

170

0V

163

0V

0V

167

2

RES

+3V3_MOJO

10K

10K

TS_SYNC

TS_VALID

C_CVBS

3149

TS_CLK

B|Pb

G|Y

R|Pr

F133

F134

10K

3150

+3V3_MOJO

10K

3119

+3V3

10K3115

3117

3100

100R3143

100R3144

100R

100R

10K3116

10K

10K

+1V2_MOJO

RES

4V6

4V6

3V3

3V3

+1V2_MOJO

6

7

8

9

36

198

39

+3V3

+3V3

+3V3

+3V3

4102

4104

K7

K7

K7

K5

K5

K5

K5

I100

3146

I101

3147

10K

15LC4.41E AB 7.

F105

F108

F114

F109

F111

F106

F107

F110

F112

F113

CONFIGURABLE

MOJO_TDI

MOJO_TRST

MOJO_TMS

3V3

0V

2

TMS

TRST

PCST0

0

12012

189

188

312433R

312333R

3122

33R

F125

1

194

0V

0V

0V

MOJO_TDO

3V2

DSU_TPC0

SYS_RESETN

5

I104

0V

0V

0V

1V2_CORE

+3V3_MOJO

4105

4110

4106

4107

4109

RES

33R

3139

3V2

208

207

TDI

TDO

7100-8

PNX8316HS

(JTAG-ETAG-SYS)

3101

10K

+3V3_MOJO

1V2

2112 100n

2113 100n

100n2114

100n2115

2116 100n

100n2103

100n

2104

100n

2105

100n

2106

100n

2107

100n

2108

100n

2109

100n

2110

2111 100n

2132

10u 16V

2131

16V10u

2130

16V10u

5100

+3V3

JTAG_TCK

JTAG_TRST

JTAG_TMS

STV_TDI

10046_TDO

3113

RES

MOJO_TRST

MOJO_TDI

10046_TDO

MOJO_TMS

MOJO_TCK

RESET_n

PCST0_0

PCST0_1

PCST0_2

TPCI

PCST1_0

PCST1_1

PCST1_2

41

78

119

VDDC

134

191

3V3

10

43

60

76

94

VDDP

111

130

161

190

MOJO_TCK

RESET_n

5103

100MHz

1V2clean

2133

10u

PCST0_0

PCST0_1

DSU_CLK DSU_CLK

PCST0_2

FOR DEV. ONLY

(I2C-USB-SCO)

SCL0

SDA0

SCL1

SDA1

SC0_DA

USB_OVRCUR

SC0_OFF

5101

100MHz

5102

100MHz

7100-6

PNX8316HS

1V2

157

160

AVSS_PLL

AVDD_PLL

DSU_CLK

186

312033R

SC0_CMDVCC

USB_PWR

SC0_CCK

SC0_RST

159187

XTAL_OUT

DSU_TPC1

33R 3121

USB_DP

USB_DM

0V

XTAL_IN

158

3V3

2100

2101

2102

RESETN

PCST1

195 4

312633R

33R 3127

10u

10u

10u

37

199

200

201

40

38

3V3

3

TCK

197

196

33R 3125

MOJO_TRST

MOJO_TDI

10046_TDO

MOJO_TMS

MOJO_TCK

RESET_n

PCST0_0

PCST0_1

PCST0_2

DSU_CLK

2122

RES

FTSH-114-01-L-DV

1

3

5

7

9

11

13

15

17

19

21

23

25

27

7100-1

PNX8314HS

(PWR)

ROW_1

1100-1

FTSH-114-01-L-DV

VSSC

VSSP

AVDD

IDUMP

ROW_2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

0

1

2

1

2

1100-2

7105 F13

1100-1 E8

F105 A7

1100-2 E8

F106 A7

A

B

C

D

E

F

G

H

I

1101 B9

1106 E14

2100 F6

2101 G6

2102 G6

2103 G6

2104 G6

2105 G6

2106 G6

2107 H6

2108 H6

2109 H6

2110 H6

2111 H6

2112 F6

2113 F6

2114 G6

2115 G6

2116 G6

2119 H9

2120 H9

2121 I9

2122 C8

2130 I7

2131 I7

2132 H7

2133 C5

3100 A4

3101 E6

3112 E9

3113 C7

3114 A3

3115 A4

3116 A4

3117 A4

3119 A4

3120 E5

3121 E5

3122 E6

3123 E6

3124 E6

3125 E6

3126 E6

3127 E6

3128 E14

3129 F14

3130 E14

3131 E14

3132 F14

3133 G1

3134 G1

3135 F1

3136 E14

3137 F14

3138 A3

3139 C6

3140 I9

3141 D14

3142 G1

3143 H4

3144 H4

3145 H2

3146 H4

3147 H4

3148 I2

3149 I3

3150 I3

3151 G13

3154 G13

3155 G14

3156-1 G11

3156-2 H11

3156-3 G11

3156-4 H11

3157-1 G11

3157-2 H11

3157-3 G11

3157-4 H11

3158-1 G11

3158-2 H11

3158-3 G11

3158-4 H11

3159-1 H11

3159-2 H11

3159-3 H11

3159-4 H11

3160 I11

3161 I11

3162 I11

3163 G11

3164 G1

4100 H3

4101 H2

4102 A4

4104 A4

4105 B7

4106 B7

4107 B7

4108 F14

4109 C7

4110 B7

5100 I7

5101 F5

5102 F5

5103 C5

7100-1 F8

7100-2 E2

7100-3 F2

7100-4 A12

7100-5 G12

7100-6 H5

7100-7 D12

7100-8 D7

7103 H3

7104 I2

F107 A7

F108 A7

F109 A7

F110 A7

F111 A7

F112 A7

F113 B7

F114 A7

F122 E9

F125 B6

F129 E13

F131 E13

F132 F13

F133 H3

F134 H3

F135 H2

F136 H2

F137 F14

F138 A10

I100 H4

I101 H4

I103 F13

I104 E6

I105 I9

0

1

2

3

4

5

6

7

SDRAM_DATA

8

9

10

11

12

13

14

15

IR_IN

IR_OUT

PWM

VS

VPP

C4

C8

SC1_DA

SC1_CMDVCC

SC1_RST

SC1_OFF

SC1_CCK

CTS0

RTS0

RX0

TX0

DCD0

PLL_OUTX0

PIO <0:15>

0

1

2

3

4

5

6

7

MIU_DATA

8

9

10

11

12

13

14

15

MIU_RDY

MIU_CS_N0

MIU_CS_N1

MIU_CS_N2

MIU_CS_N3

MIU_OE_N

MIU_WEN

MIU_MASK0

7100-4

PNX8316HS

(SDRAM)

SDRAM_ADDR

7100-7

PNX8316HS

(GPIO)

7100-5

PNX8316HS

(MIU)

DQM0

DQM1

CAS

RAS

WE

CKE

HSCKB

VCXO_CLOCK

BOOT <0:3>

ITU_OUT

ITU_CLOCK

PIO <16:27>

MIU_ADDR

MIU_MASK1

MIU_LBA

MIU_BAA

MIU_CLK

10

11

12

13

14

DTR0

0V

153

0

0V

154

1

0V

155

2

0V

156

3

0V

149

4

0V

148

5

0V

147

6

0V

146

7

0V

145

8

0V

144

9

0V

152

0V

143

0V

142

0V

150

0V

151

2V1

138

3V1

133

3V

140

2V9

141

3V

139

3V3

137

1V5

136

N.C.

DTR0

17

0V

F129

UART1_RX

0V

18

RX1

3V3

19

TX1

0V

PIO19|ITU_OUT0|BOOT0

176

0

177

3V3

3V3

PIO21|ITU_OUT2|BOOT2

178

179

I103

180

181

182

3V2

F132

183

0V

184

DSW_I2C_enable

75

0V

80

3V3

81

0V

82

3V3

83

3V3

84

3V3

85

3V3

86

0V

87

0V

88

3V3

89

0V

90

0V

3V3

91

0V

92

93

3V3

96

0V

97

0V

98

3V3

99

3V3

100

3V3

101

3V3

102

3V3

103

0V

104

0V

105

0V

107

110

50

51

PIO20|ITU_OUT1|BOOT1

PIO22|ITU_OUT3|BOOT3

RES

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

UART1_TX

RES

+3V3_MOJO

3151

10K

10K

3154

7105

BSN20

F131

2

RES

1

3155

10K

3130 10K

3128

3131

4108

SDRAM_ADDR(10)

SDRAM_ADDR(11)

SDRAM_ADDR(12)

SDRAM_ADDR(13)

SDRAM_ADDR(14)

3141

10K

B2B-PH-K

RES

F137

3

3132

10K

MIU_ADDR(0)

MIU_ADDR(1)

MIU_ADDR(2)

MIU_ADDR(3)

MIU_ADDR(4)

MIU_ADDR(5)

MIU_ADDR(6)

MIU_ADDR(7)