查询HEF4737供应商查询HEF4737供应商

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4737B

HEF4737V

LSI

Quadruple static decade counters

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

DESCRIPTION

The HEF4737B and HEF4737V are static quadruple

decade counters for frequencies from 0 to 10 MHz. The

counters are supplied with an extra overload flip-flop giving

a total count capability of 19 999. The counter has the

following inputs and outputs: a count input (CP), an

asynchronous reset input (MR), an asynchronous preset

input (PL), a transfer input (T), an output enable input (EO)

(which controls the BCD outputs), the digit select inputs

(SA, SB, SC) (which perform selection of the contents of the

latches to the 3-state BCD outputs (O

to O3)), and the

0

carry outputs (CO2to CO5) (which give the carry signals of

the decades except from the first decade).

The complementary MOS structure gives the devices very

low stand-by and operating dissipation. Operating from a

single supply voltage all outputs can drive one standard

TTL input without interface circuitry under all specified

operating conditions.

The BCD digit outputs are LOCMOS 3-state outputs. The

high impedance off-state feature allows common busing of

the outputs. The counters are supplied with asynchronous

reset and preset to 19 999 facilities making them suitable

for counter and time base applications. All carry signals

are available except from the first decade.

Schmitt-trigger action in the inputs makes the circuit highly

tolerant to slower input rise and fall times.

Recommended supply voltage range for HEF4737B is 3 to

15 V and for HEF4737V is 4,5 to 12,5 V.

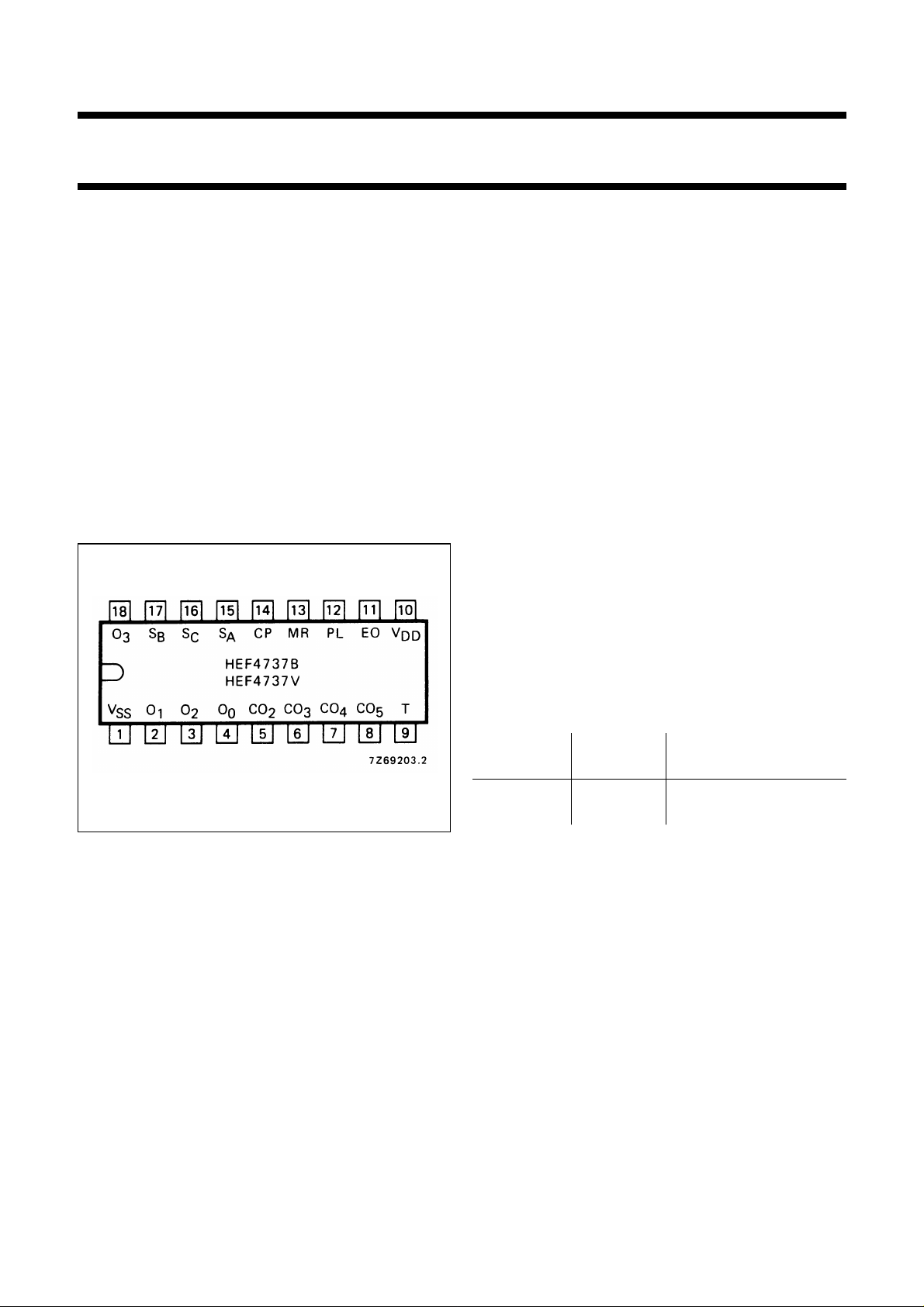

HEF4737BP; HEF4737VP(N); 18-lead DIL

plastic (SOT102-1)

HEF4737BD; HEF4737VD(F); 18-lead DIL

ceramic (SOT133B)

( ): Package Designator North America

Fig.1 Pinning diagram.

PINNING

CP count input

MR asynchronous reset input

PL asynchronous preset input

T transfer input

S

, SB, S

A

C

digit select inputs

EO output enable input

O

CO

0

to O

to CO

2

3

5

BCD outputs

carry outputs

SUPPLY VOLTAGE

RATING RECOMMENDED

OPERATING

HEF4737B −0,5 to 18 3,0 to 15,0 V

HEF4737V −0,5 to 18 4,5 to 12,5 V

FAMILY DATA, I

LIMITS category LSI

DD

See Family Specifications

January 1995 2

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

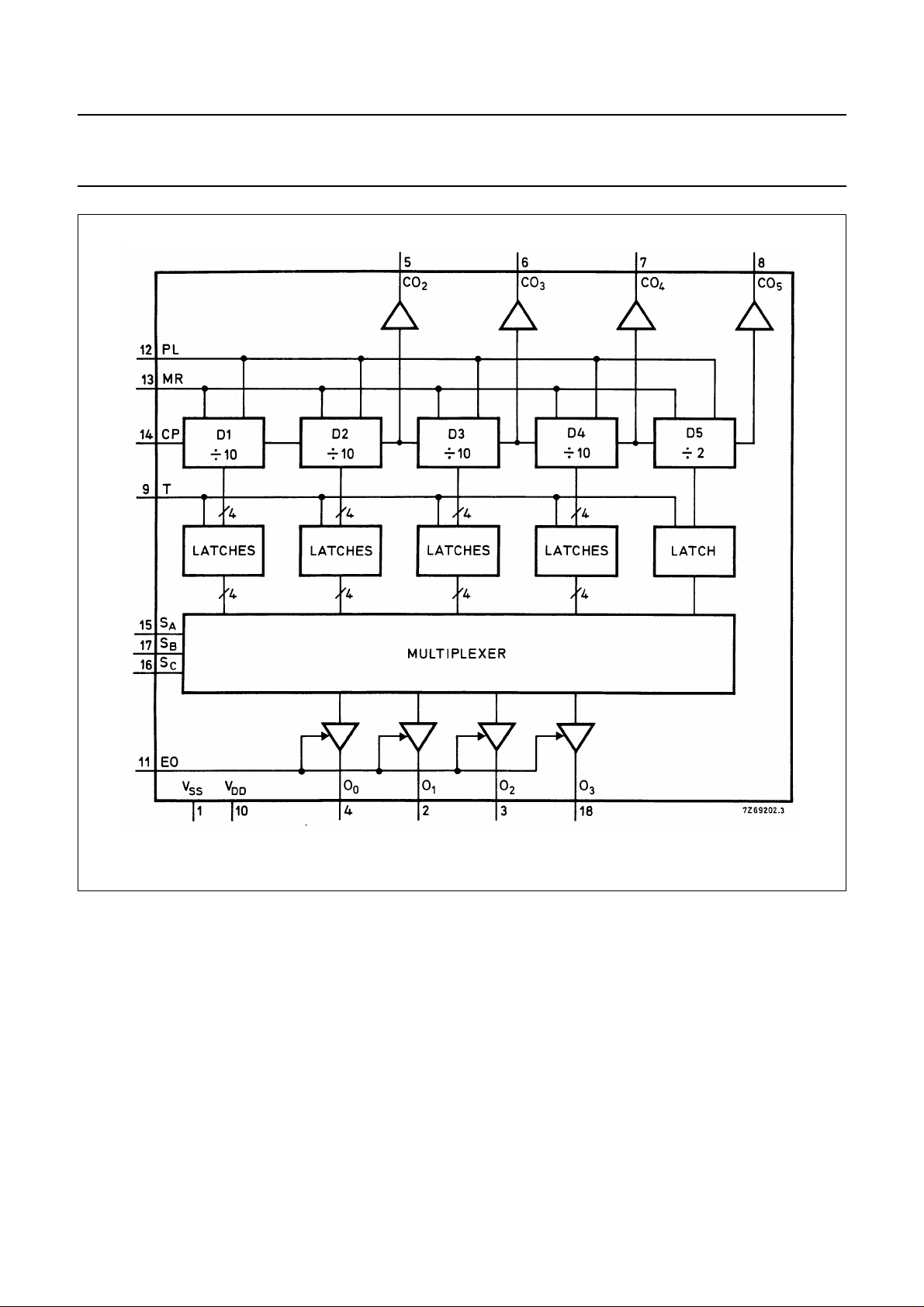

Fig.2 Block diagram.

FUNCTIONAL DESCRIPTION

Input signals

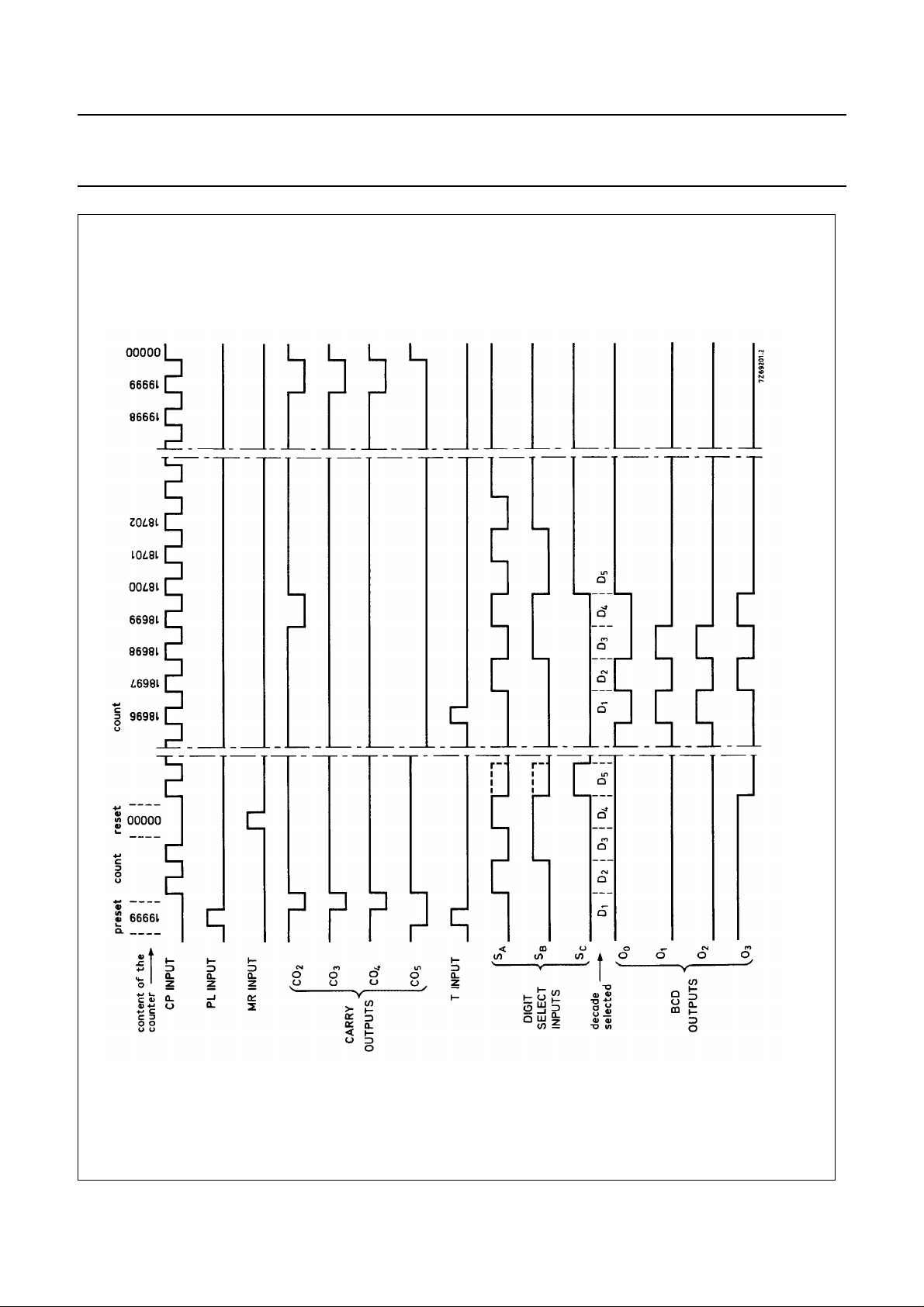

Count input (CP)

The signal to be counted is applied to this input. When PL

and MR are LOW the contents of the counter increments

by one at a LOW to HIGH transition of CP.

Reset input (MR)

This is an asynchronous reset. A HIGH level applied to this

input will reset the counter to zero independent of the level

at the count input and preset input.

January 1995 3

Preset input (PL)

This is an asynchronous preset. When MR is LOW a HIGH

at the PL input will preset the counter to 19 999

independent of the level at the count input.

Transfer input (T)

A HIGH level applied to this input allows the information

held by the counter to pass to the latches.

Output enable input (EO)

A HIGH level at this input enables the BCD outputs and

information can be read out of the latches using the

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

multiplexer. A LOW level at this input disables the BCD

outputs making them floating (high impedance off-state).

Digit select inputs (SA, SB, SC)

S

A

S

B

S

C

L L L selects D1 (LSD)

H L L selects D2

L H L selects D3

H H L selects D4

X X H selects D5 (MSD)

Notes

1. H = HIGH state (the more positive voltage)

2. L = LOW state (the less positive voltage)

3. X = state is immaterial

4. When D5 is selected, the contents of D5 is available at

O0and O1,O2 and O3are LOW.

5. LSD = least significant divider

6. MSD = most significant divider

Output signals

The carry outputs are active LOW outputs.

Carry output CO

2

When the contents of the first two decades of the counter

are both 9 then the CO2output becomes LOW. It remains

LOW until the next LOW to HIGH transition of the count

input, i.e. until the contents of the first two decades are

zero. CO2is LOW when the contents of the counter are: 00

099, 00 199, 00 299 etc.

Carry output CO

3

When the contents of the first three decades of the counter

are all 9 then the CO3output becomes LOW. It remains

LOW until the next LOW to HIGH transition of the count

input, i.e. until the contents of the first three decades are

zero. CO3is LOW when the contents of the counter are

00 999, 01 999, 02 999 etc.

Carry output CO

4

When the contents of the first four decades of the counter

are all 9 then the CO4output becomes LOW. It remains

LOW until the next LOW to HIGH transition of the count

input, i.e. until the contents of the first four decades are

zero. CO4is LOW when the contents of the counter are

09 999 and 19 999.

The carry signals CO2, CO3and CO4are suppressed

while the preset is active. A HIGH to the preset input sets

the counter to 19 999 but the carry signals remain HIGH

until preset input returns to LOW, then the carry outputs

will also become LOW.

Carry output CO

5

When the content of the counter is 10 000 the CO5output

becomes LOW. It returns to HIGH when the content of the

counter is zero.

Digit outputs (O0to O3)

The digit outputs give the contents of the selected latch.

The output is in the form of BCD, positive logic.

January 1995 4

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

January 1995 5

Fig.3 Timing diagram.

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

The values given at VDD= 15 V in the following d.c. and a.c. characteristics, are not applicable to the HEF4737V,

because of its reduced supply voltage range.

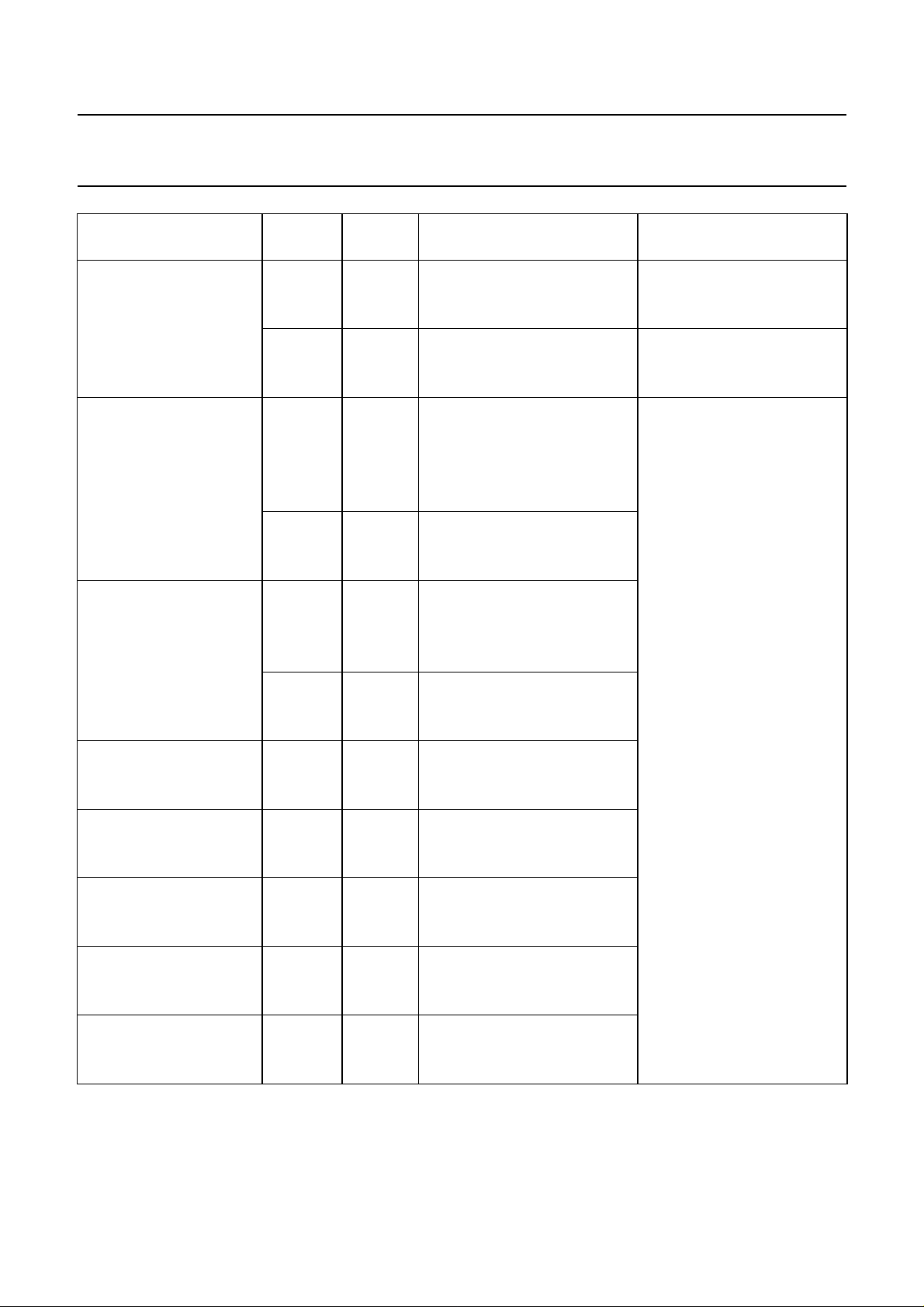

DC CHARACTERISTICS

=0V

V

SS

T

(°C)

amb

V

V

Input leakage

current at 10

V

= 0 or V

I

DD

15 −− −0,3 − 1 µA

Output (sink) 4,75 0,4 1,6 − 1,6 − 1,4 − mA

current LOW 10 0,5 I

15 1,5 7,0 − 6,0 − 4,0 − mA

Output (source) 5 4,6 0,96 − 0,80 − 0,65 − mA

current HIGH 10 9,5 −I

15 13,5 7,0 − 6,0 − 4,5 − mA

Output (source)

current HIGH 5 2,5 −I

3-state output

leakage current 10

V

= 0 or V

O

DD

15 − 1,6 − 1,6 − 12 µA

DD

V

V

OH

V

OL

V

SYMBOL

−40 + 25 + 85

MIN. MAX. MIN. MAX. MIN. MAX.

± I

± I

IN

OL

OH

OH

OZ

−− −0,3 − 1 µA

2,5 − 2,3 − 1,7 − mA

2,4 − 2,0 − 1,6 − mA

3,0 − 2,5 − 2,0 − mA

− 1,6 − 1,6 − 12 µA

HEF4737V

AC CHARACTERISTICS

V

SS

=0V; T

=25°C; CL= 15 pF; input transition times ≤ 20 ns

amb

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLA TION

FORMULA

Propagation delays

CP → O

n

(D1 selected) 10 t

5 320 640 ns 308 ns + (0,24 ns/pF) C

PHL

120 240 ns 125 ns + (0,10 ns/pF) C

HIGH to LOW 15 90 180 ns 86 ns + (0,07 ns/pF) C

5 320 640 ns 296 ns + (0,48 ns/pF) C

LOW to HIGH 10 t

PLH

120 240 ns 110 ns + (0,20 ns/pF) C

15 90 180 ns 82 ns + (0,15 ns/pF) C

CP → O

n

(D5 selected) 10 t

5 620 1240 ns 608 ns + (0,24 ns/pF) C

PHL

330 660 ns 325 ns + (0,10 ns/pF) C

HIGH to LOW 15 250 500 ns 246 ns + (0,07 ns/pF) C

5 620 1240 ns 596 ns + (0,48 ns/pF) C

LOW to HIGH 10 t

PLH

330 660 ns 320 ns + (0,20 ns/pF) C

15 250 500 ns 242 ns + (0,15 ns/pF) C

January 1995 6

L

L

L

L

L

L

L

L

L

L

L

L

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

CP → CO

2

HIGH to LOW 10 t

LOW to HIGH 10 t

Propagation delays

CP → CO

5

HIGH to LOW 10 t

LOW to HIGH 10 t

Sn→ O

n

HIGH to LOW 10 t

LOW to HIGH 10 t

T→ O

n

HIGH to LOW 10 t

LOW to HIGH 10 t

MR → O

n

HIGH to LOW 10 t

PL → O

n

LOW to HIGH 10 t

MR → CO

n

LOW to HIGH 10 t

PL → CO

n

HIGH to LOW 10 t

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLA TION

FORMULA

5 220 440 ns 208 ns + (0,24 ns/pF) C

PHL

110 220 ns 105 ns + (0,10 ns/pF) C

15 85 170 ns 81 ns + (0,07 ns/pF) C

5 220 400 ns 196 ns + (0,48 ns/pF) C

PLH

110 220 ns 100 ns + (0,20 ns/pF) C

15 85 170 ns 77 ns + (0,15 ns/pF) C

5 350 700 ns 338 ns + (0,24 ns/pF) C

PHL

160 320 ns 155 ns + (0,10 ns/pF) C

15 120 240 ns 116 ns + (0,07 ns/pF) C

5 350 700 ns 326 ns + (0,48 ns/pF) C

PLH

160 320 ns 150 ns + (0,20 ns/pF) C

15 120 240 ns 112 ns + (0,15 ns/pF) C

5 200 400 ns 188 ns + (0,24 ns/pF) C

PHL

80 160 ns 75 ns + (0,10 ns/pF) C

15 55 110 ns 51 ns + (0,07 ns/pF) C

5 200 400 ns 176 ns + (0,48 ns/pF) C

PLH

80 160 ns 70 ns + (0,20 ns/pF) C

15 55 110 ns 47 ns + (0,15 ns/pF) C

5 220 440 ns 208 ns + (0,24 ns/pF) C

PHL

90 180 ns 85 ns + (0,10 ns/pF) C

15 60 120 ns 56 ns + (0,07 ns/pF) C

5 220 440 ns 196 ns + (0,48 ns/pF) C

PLH

90 180 ns 80 ns + (0,20 ns/pF) C

15 60 120 ns 52 ns + (0,15 ns/pF) C

5 490 980 ns 478 ns + (0,24 ns/pF) C

PHL

200 400 ns 195 ns + (0,10 ns/pF) C

15 60 120 ns 56 ns + (0,07 ns/pF) C

5 260 520 ns 236 ns + (0,48 ns/pF) C

PLH

110 220 ns 100 ns + (0,20 ns/pF) C

15 85 170 ns 77 ns + (0,15 ns/pF) C

5 350 700 ns 326 ns + (0,48 ns/pF) C

PLH

160 320 ns 150 ns + (0,20 ns/pF) C

15 120 240 ns 112 ns + (0,15 ns/pF) C

5 350 700 ns 338 ns + (0,24 ns/pF) C

PHL

160 320 ns 155 ns + (0,10 ns/pF) C

15 120 240 ns 116 ns + (0,07 ns/pF) C

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

January 1995 7

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

V

DD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLA TION

FORMULA

Output transition 5 35 70 ns 15 ns + (0,40 ns/pF) C

times; any output 10 t

THL

18 36 ns 9 ns + (0,18 ns/pF) C

HIGH to LOW 15 15 30 ns 8 ns + (0,13 ns/pF) C

5 50 100 ns 15 ns + (0,70 ns/pF) C

LOW to HIGH 10 t

TLH

30 60 ns 13 ns + (0,33 ns/pF) C

15 25 50 ns 13 ns + (0,23 ns/pF) C

3-state propagation delays

Output disable times

EO → O

n

HIGH 10 t

5 60 120 ns

PHZ

35 70 ns

15 25 50 ns

5 60 120 ns

LOW 10 t

PLZ

35 70 ns

15 25 50 ns

Output enable times

EO → O

n

HIGH 10 t

5 90 180 ns

PZH

40 80 ns

15 30 60 ns

5 90 180 ns

LOW 10 t

PZL

40 80 ns

15 30 60 ns

Maximum CP pulse 5 160 80 ns

width; LOW 10 t

WCPL

60 30 ns

15 50 25 ns

Minimum MR pulse 5 100 50 ns

width; HIGH 10 t

WMRH

50 25 ns

15 40 20 ns

Minimum PL pulse 5 120 60 ns

width; HIGH 10 t

WPLH

60 30 ns

15 50 25 ns

Minimum T pulse 5 100 50 ns

width; HIGH 10 t

WTH

40 20 ns

15 36 18 ns

Maximum clock 5 3 6 MHz

pulse frequency 10 f

max

8 16 MHz

15 10 20 MHz

L

L

L

L

L

L

January 1995 8

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

V

DD

V

Dynamic power 5 950 f

dissipation per 10 4 200 f

package (P) 15 11 200 f

TYPICAL FORMULA FOR P (µW)

+∑(foCL) × V

i

+∑(foCL) × V

i

+∑(foCL) × V

i

DD

DD

DD

2

where

2

fi= input freq. (MHz)

2

fo= output freq. (MHz)

C

= load cap. (pF)

L

∑ (f

oCL

= supply voltage (V)

V

DD

) = sum of outputs

HEF4737V

January 1995 9

Loading...

Loading...