INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4737B

HEF4737V

LSI

Quadruple static decade counters

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

DESCRIPTION

The HEF4737B and HEF4737V are static quadruple

decade counters for frequencies from 0 to 10 MHz. The

counters are supplied with an extra overload flip-flop giving

a total count capability of 19 999. The counter has the

following inputs and outputs: a count input (CP), an

asynchronous reset input (MR), an asynchronous preset

input (PL), a transfer input (T), an output enable input (EO)

(which controls the BCD outputs), the digit select inputs

(SA, SB, SC) (which perform selection of the contents of the

latches to the 3-state BCD outputs (O

to O3)), and the

0

carry outputs (CO2to CO5) (which give the carry signals of

the decades except from the first decade).

The complementary MOS structure gives the devices very

low stand-by and operating dissipation. Operating from a

single supply voltage all outputs can drive one standard

TTL input without interface circuitry under all specified

operating conditions.

The BCD digit outputs are LOCMOS 3-state outputs. The

high impedance off-state feature allows common busing of

the outputs. The counters are supplied with asynchronous

reset and preset to 19 999 facilities making them suitable

for counter and time base applications. All carry signals

are available except from the first decade.

Schmitt-trigger action in the inputs makes the circuit highly

tolerant to slower input rise and fall times.

Recommended supply voltage range for HEF4737B is 3 to

15 V and for HEF4737V is 4,5 to 12,5 V.

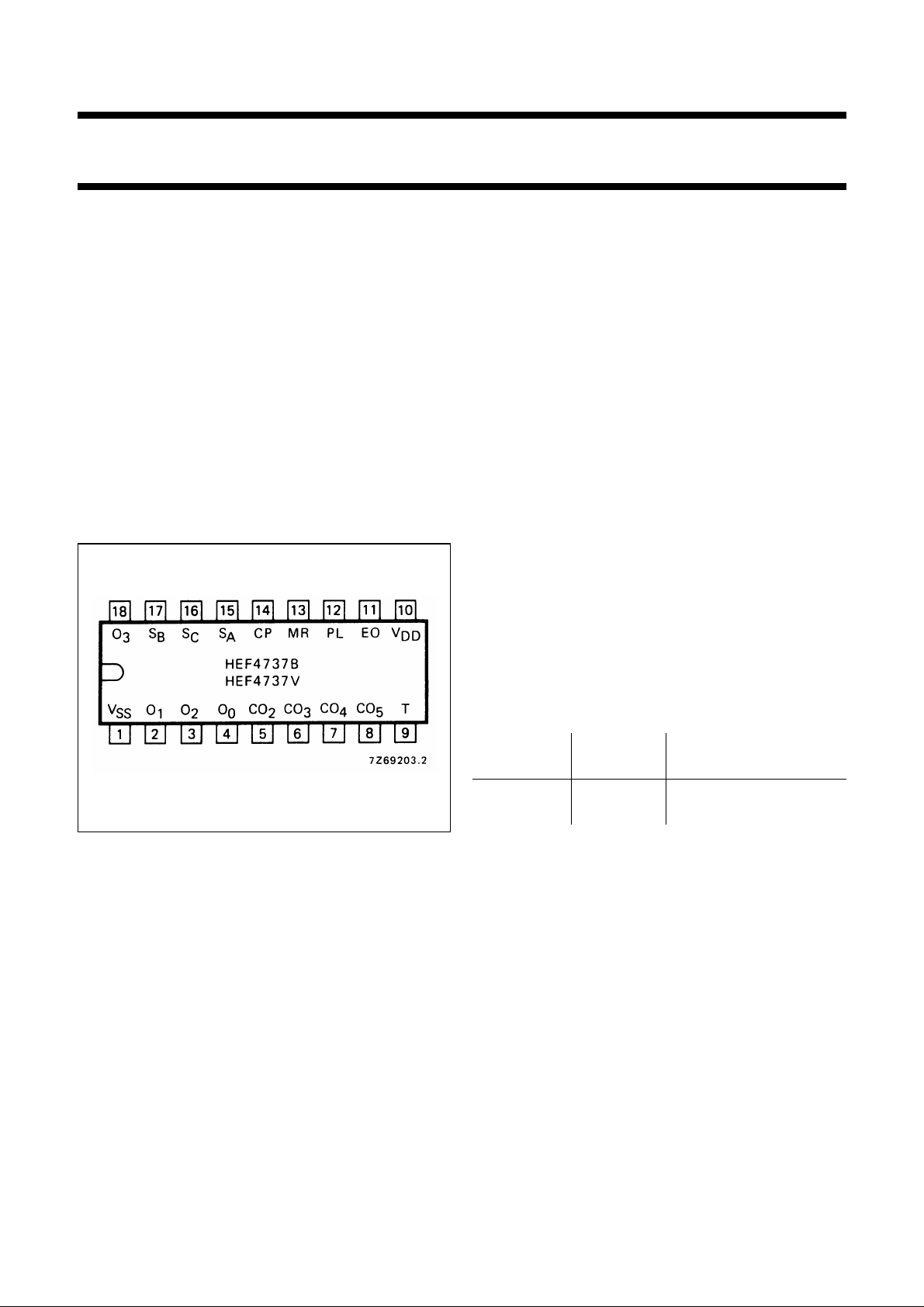

HEF4737BP; HEF4737VP(N); 18-lead DIL

plastic (SOT102-1)

HEF4737BD; HEF4737VD(F); 18-lead DIL

ceramic (SOT133B)

( ): Package Designator North America

Fig.1 Pinning diagram.

PINNING

CP count input

MR asynchronous reset input

PL asynchronous preset input

T transfer input

S

, SB, S

A

C

digit select inputs

EO output enable input

O

CO

0

to O

to CO

2

3

5

BCD outputs

carry outputs

SUPPLY VOLTAGE

RATING RECOMMENDED

OPERATING

HEF4737B −0,5 to 18 3,0 to 15,0 V

HEF4737V −0,5 to 18 4,5 to 12,5 V

FAMILY DATA, I

LIMITS category LSI

DD

See Family Specifications

January 1995 2

Philips Semiconductors Product specification

HEF4737B

Quadruple static decade counters

HEF4737V

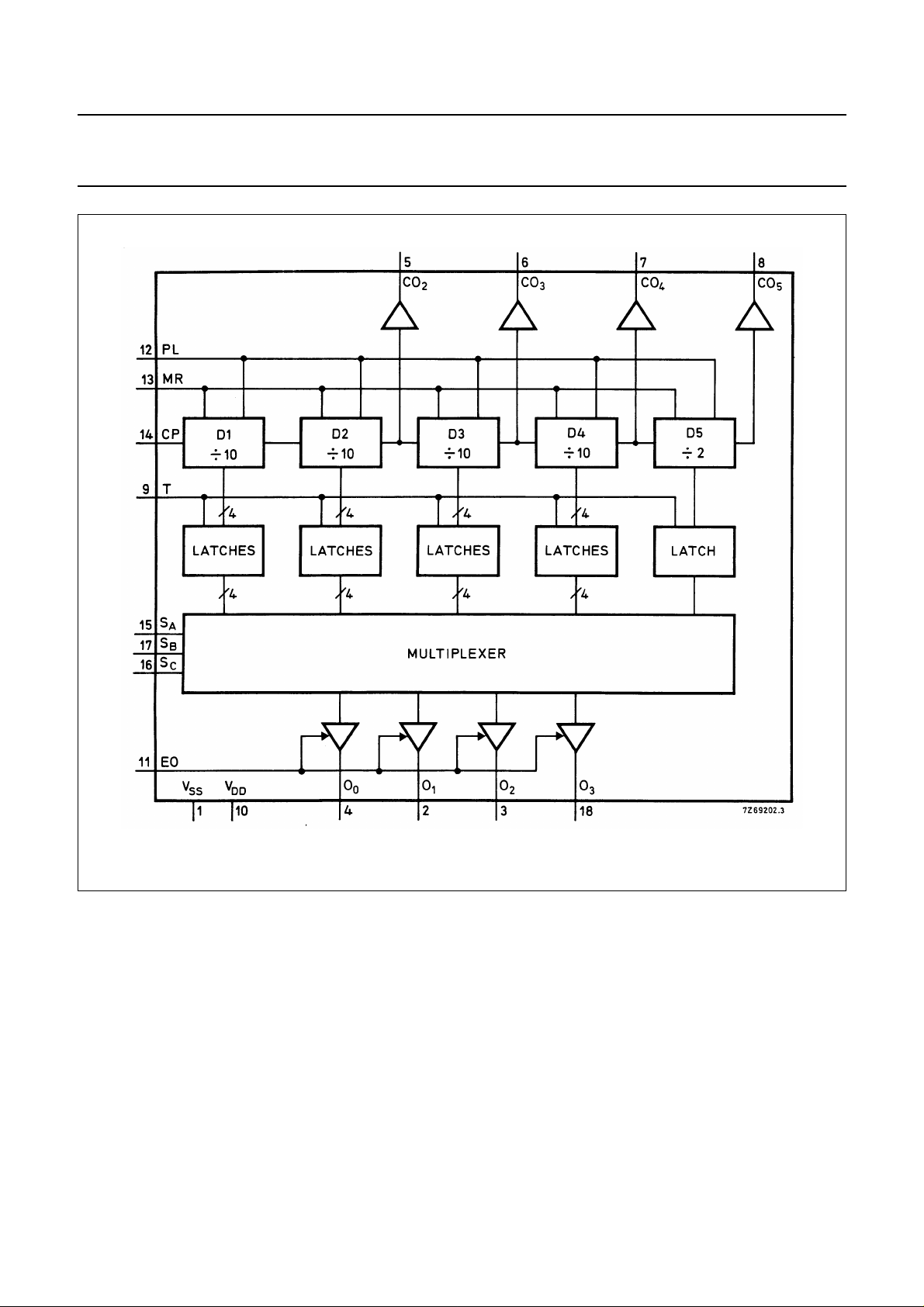

Fig.2 Block diagram.

FUNCTIONAL DESCRIPTION

Input signals

Count input (CP)

The signal to be counted is applied to this input. When PL

and MR are LOW the contents of the counter increments

by one at a LOW to HIGH transition of CP.

Reset input (MR)

This is an asynchronous reset. A HIGH level applied to this

input will reset the counter to zero independent of the level

at the count input and preset input.

January 1995 3

Preset input (PL)

This is an asynchronous preset. When MR is LOW a HIGH

at the PL input will preset the counter to 19 999

independent of the level at the count input.

Transfer input (T)

A HIGH level applied to this input allows the information

held by the counter to pass to the latches.

Output enable input (EO)

A HIGH level at this input enables the BCD outputs and

information can be read out of the latches using the

Loading...

Loading...