Philips hef4521b DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4521B

MSI

24-stage frequency divider and

oscillator

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors Product specification

24-stage frequency divider and oscillator

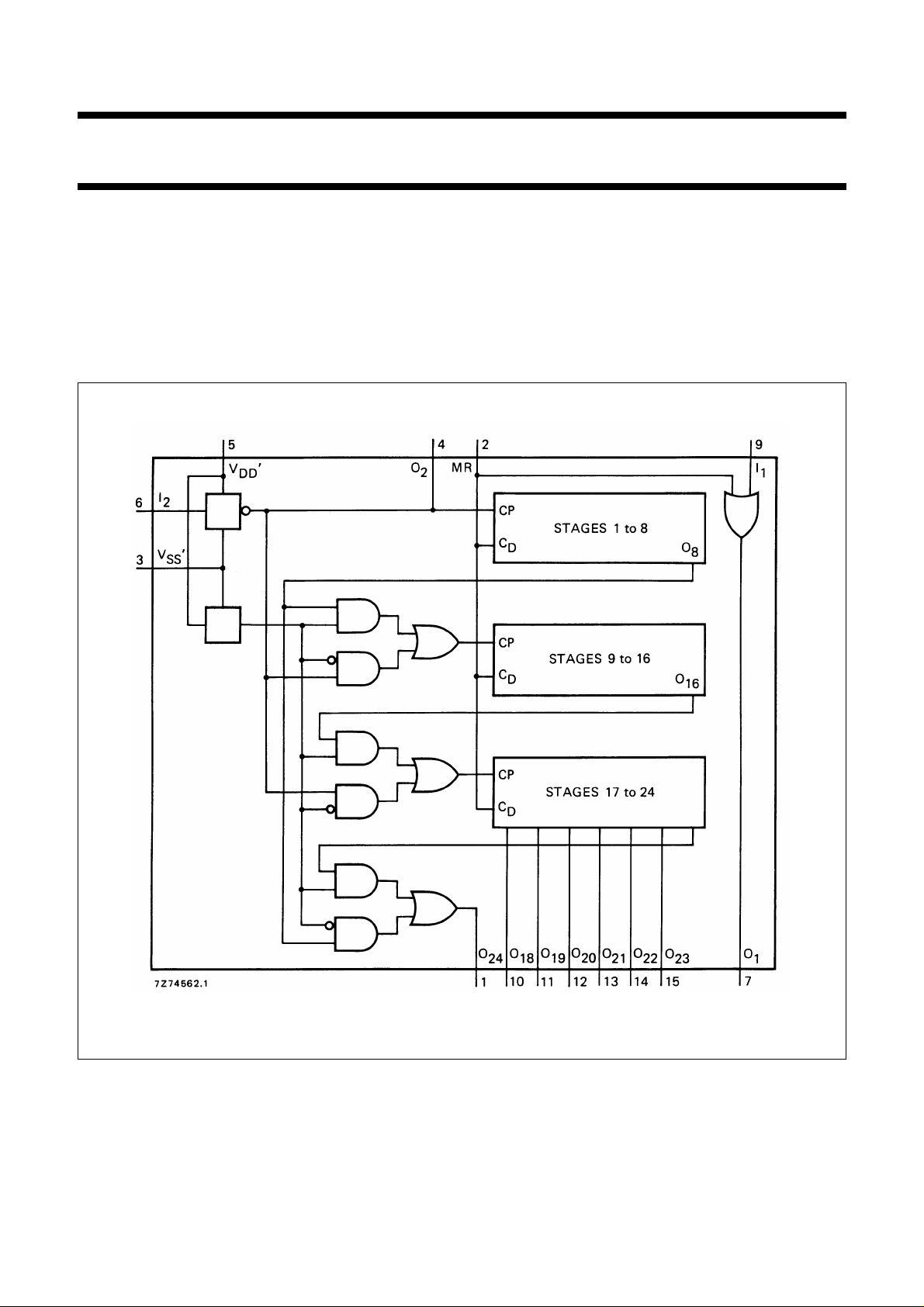

DESCRIPTION

The HEF4521B consists of a chain of 24 toggle flip-flops

with an overriding asynchronous master reset input (MR),

and an input circuit that allows three modes of operation.

The single inverting stage (I2/O2) will function as a crystal

oscillator, or in combination with I1as an RC oscillator, or

as an input buffer for an external oscillator. Low-power

operation as a crystal oscillator is enabled by connecting

external resistors to pins 3 (V

Each flip-flop divides the frequency of the previous flip-flop

by two, consequently the HEF4521B will count up to

224= 16777216. The counting advances on the HIGH to

LOW transition of the clock (I2). The outputs of the last

seven stages are available for additional flexibility.

HEF4521B

’) and 5 (VDD’).

SS

MSI

Fig.1 Functional diagram.

FAMILY DATA, I

See Family Specifications

January 1995 2

LIMITS category MSI

DD

Philips Semiconductors Product specification

24-stage frequency divider and oscillator

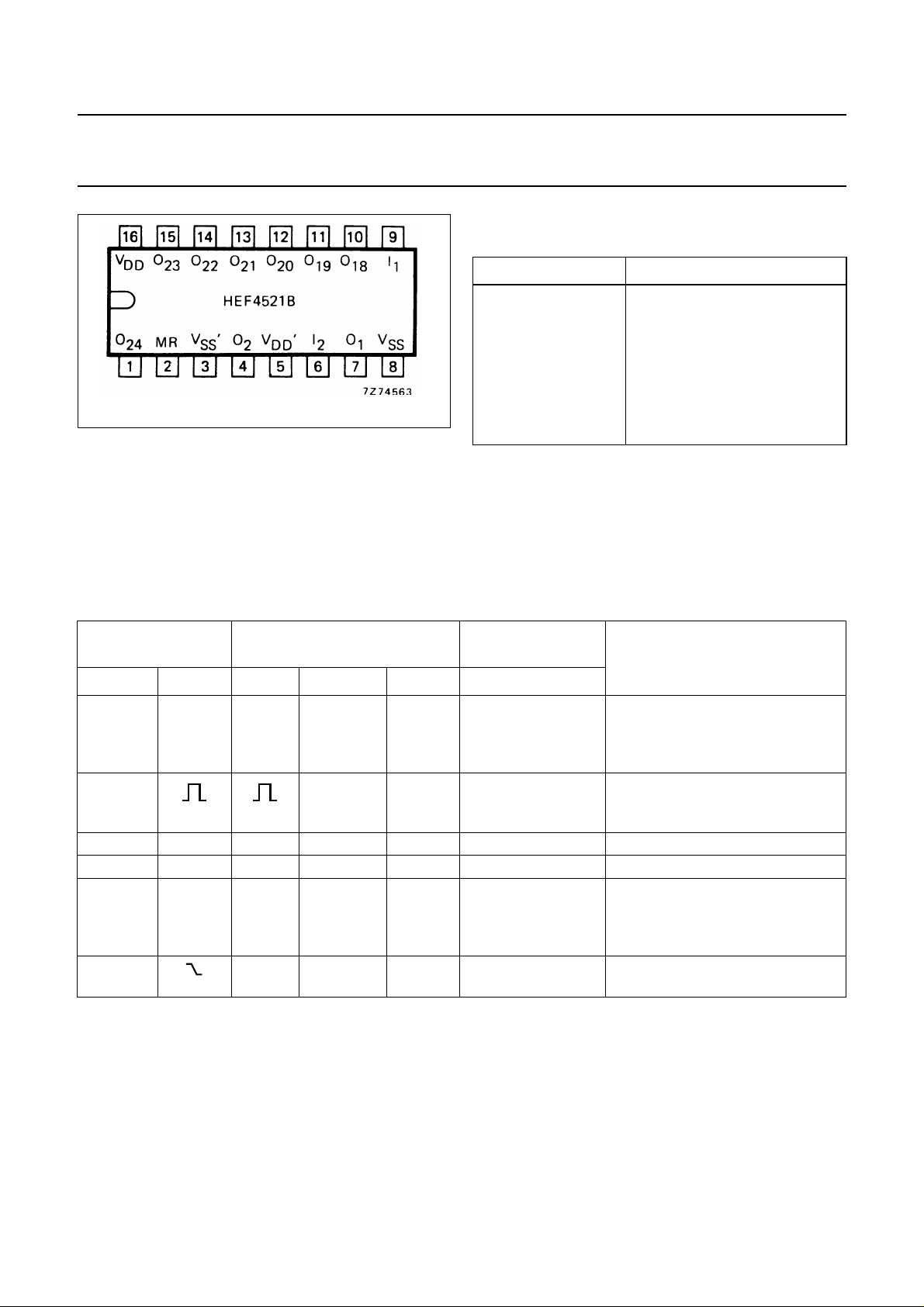

Fig.2 Pinning diagram.

HEF4521BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4521BD(F): 16-lead DIL; ceramic (cerdip) (SOT74)

HEF4521BT(D): 16-lead SO; plastic (SOT109-1)

( ): Package Designator North America

COUNT CAPACITY

OUTPUT COUNT CAPACITY

O

18

O

19

O

20

O

21

O

22

O

23

O

24

218= 262 144

219= 524 288

220= 1 048 576

221= 2 097 152

222= 4 194 304

223= 8 388 608

224= 16 777 216

HEF4521B

MSI

FUNCTIONAL TEST SEQUENCE

INPUTS

MR I

2

O

HLLVDDV

LV

LLLV

LHLVSSV

LHLV

LV

TERMINALS

2

CONTROL

VSS’V

DD

SS

SS

SS

DD

V

V

V

V

’O

SS

SS

SS

SS

DD

DD

A test function has been included for the reduction of the

test time required to exercise all 24 counter stages. This

test function divides the counter into three 8-stage

sections by connecting VSS’toVDDand VDD’toVSS. Via

I2(connected to O2) 255 counts are loaded into each of

the 8-stage sections in parallel. All flip-flops are now at a

HIGH state.

OUTPUTS

REMARKS

to O

18

24

L counter is in three 8-stage sections

in parallel mode; I2and O2are

interconnected (O2is now input);

counter is reset by MR

H 255 pulses are clocked into I2,O

2

(the counter advances on the LOW

to HIGH transition)

HV

’ is connected to V

SS

SS

H the input I2is made HIGH

HV

’ is connected to VDD;O2is

DD

now made floating and becomes an

output; the device is now in the

224mode

L

counter ripples from an all HIGH

state to an all LOW state

The counter is now returned to the normal 24-stage in

series configuration by connecting VSS’ to VSSand VDD’to

VDD. One more pulse is entered into input I2, which will

cause the counter to ripple from an all HIGH state to an all

LOW state.

January 1995 3

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

January 1995 4

Philips Semiconductors Product specification

24-stage frequency divider and oscillator

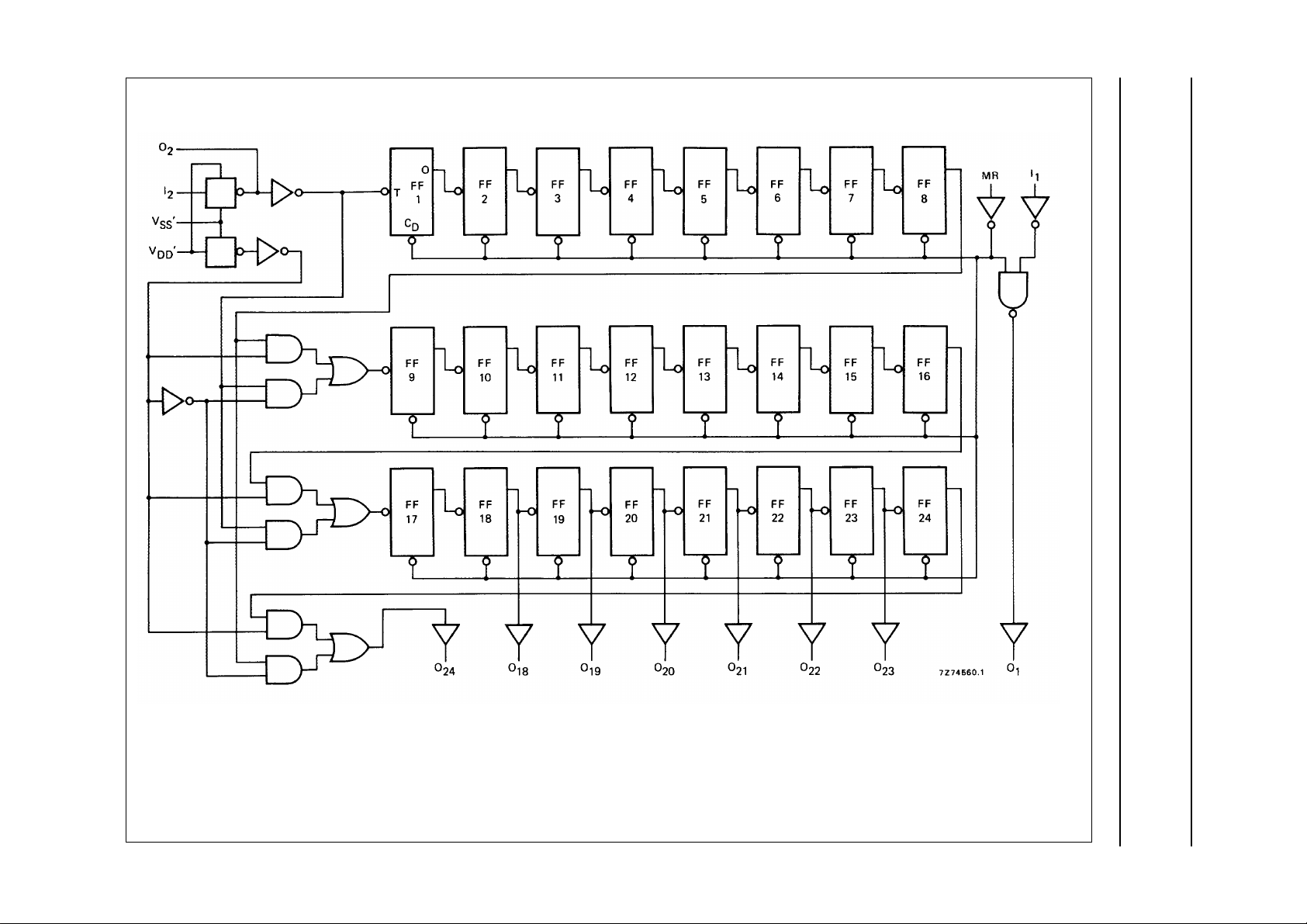

Fig.3 Logic diagram; for schematic diagram of clock circuit see Fig.4.

HEF4521B

MSI

Loading...

Loading...