Philips hef4043b DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4043B

MSI

Quadruple R/S latch with 3-state

outputs

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors Product specification

Quadruple R/S latch with 3-state outputs

DESCRIPTION

The HEF4043B is a quadruple R/S latch with 3-state

outputs with a common output enable input (EO). Each

latch has an active HIGH set input (S0 to S3), an active

HIGH reset input (R0to R3) and an active HIGH 3-state

output (O0to O3).

When EO is HIGH, the state of the latch output (On) can be

determined from the function table below. When EO is

LOW, the latch outputs are in the high impedance

OFF-state. EO does not affect the state of the latch.

The high impedance off-state feature allows common

busing of the outputs.

HEF4043B

MSI

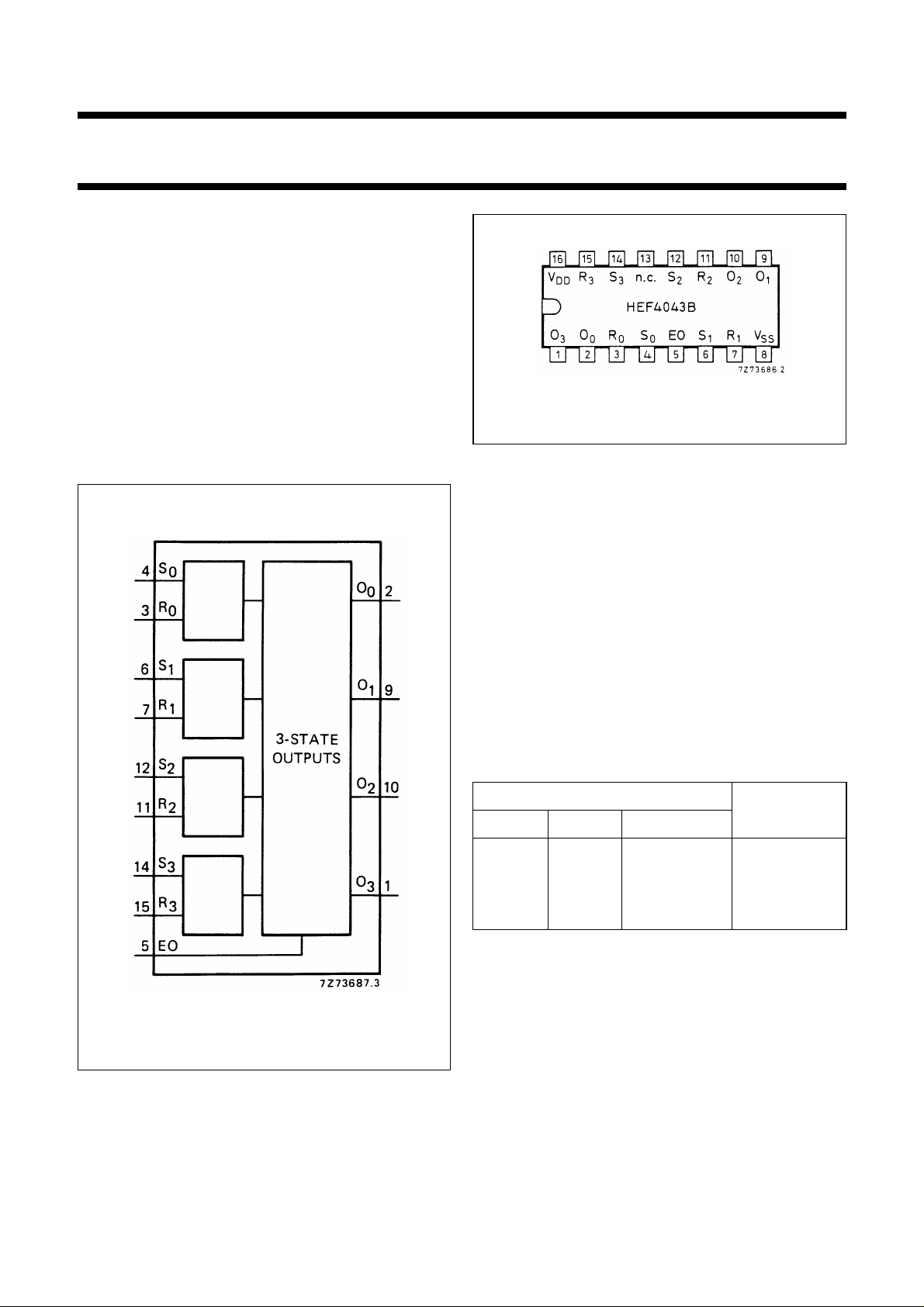

Fig.2 Pinning diagram.

HEF4043BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4043BD(F): 16-lead DIL; ceramic (cerdip) (SOT74)

HEF4043BT(D): 16-lead SO; plastic (SOT109-1)

( ): Package Designator North America

Fig.1 Functional diagram.

PINNING

EO common output enable input

S

R

O

to S

0

to R

0

0

to O

3

3

3

set inputs (active HIGH)

reset inputs (active HIGH)

3-state buffered latch outputs

FUNCTION TABLE

INPUTS OUTPUT

EO S

n

R

n

O

LX X Z

HL H L

HH X H

H L L latched

Notes

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state immaterial

Z = high impedance state

n

January 1995 2

FAMILY DATA, IDDLIMITS category MSI

See Family Specifications

Loading...

Loading...