Philips hef4042b DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4042B

MSI

Quadruple D-latch

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors Product specification

Quadruple D-latch

DESCRIPTION

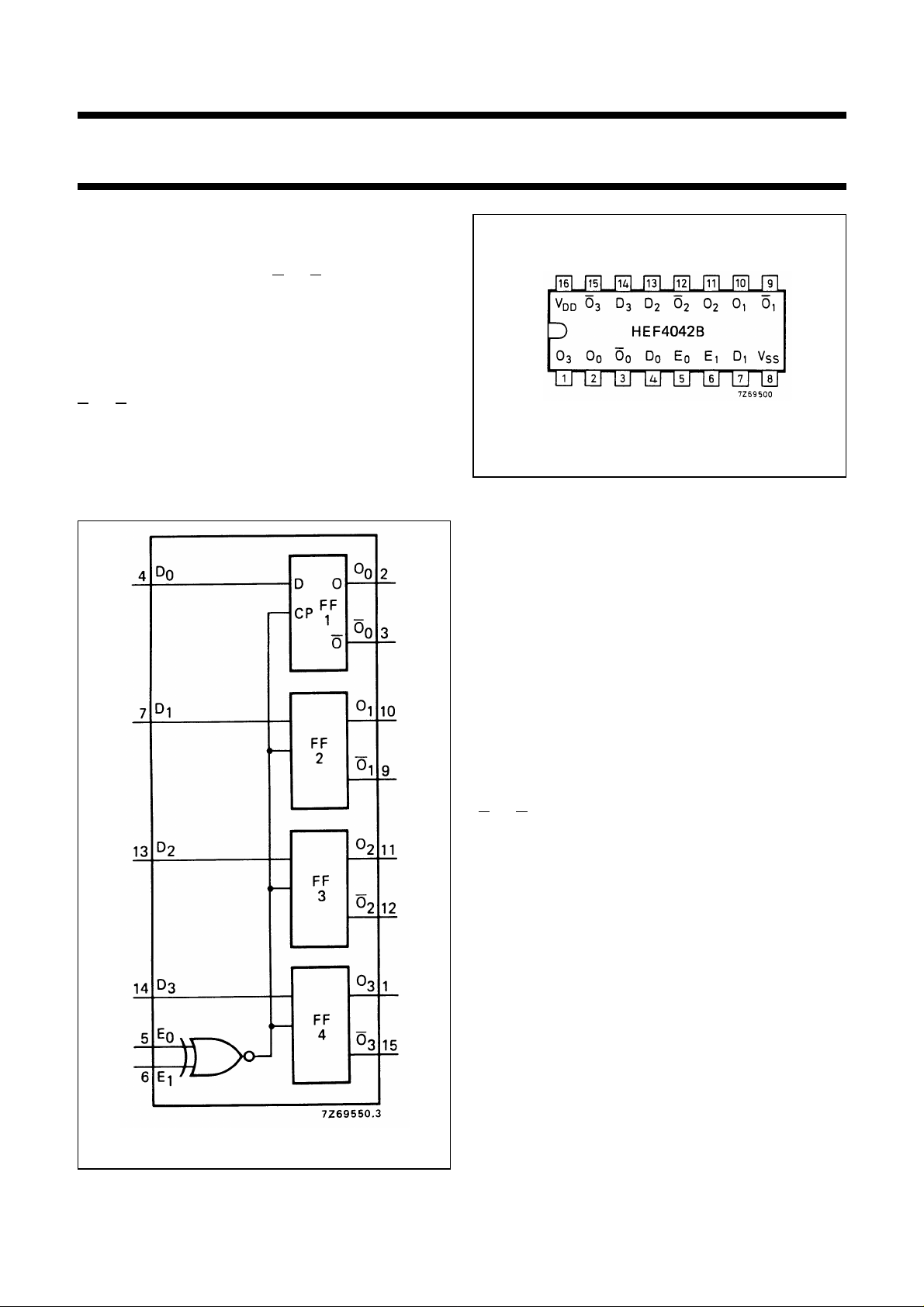

The HEF4042B is a 4-bit latch with four data inputs (D0to

D3), four buffered latch outputs (O0to O3), four buffered

complementary latch outputs (O0to O3) and two common

enable inputs (E0and E1). Information on D0to D3is

transferred to O0to O3while both E0and E1are in the

same state, either HIGH or LOW. O0to O3follow D0to

D3as long as both E0and E1remain in the same state.

When E0and E1are different, D0to D3do not affect O0to

O3 and the information in the latch is stored.

O0to O3are always the complement of O0to O3. The

exclusive-OR input structure allows the choice of either

polarity for E0and E1. With one enable input HIGH, the

other enable input is active HIGH; with one enable input

LOW, the other enable input is active LOW.

HEF4042B

MSI

Fig.2 Pinning diagram.

HEF4042BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4042BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4042BT(D): 16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

Fig.1 Functional diagram.

PINNING

D

to D

0

E

and E

0

to O

O

0

O0to O

3

3

3

data inputs

enable inputs

1

parallel latch outputs

complementary parallel latch outputs

APPLICATION INFORMATION

Some examples of applications for the HEF4042B are:

• Buffer storage

• Holding register

FAMILY DATA, IDDLIMITS category MSI

See Family Specifications

January 1995 2

Loading...

Loading...