Philips hef4027b DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4027B

flip-flops

Dual JK flip-flop

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors Product specification

Dual JK flip-flop

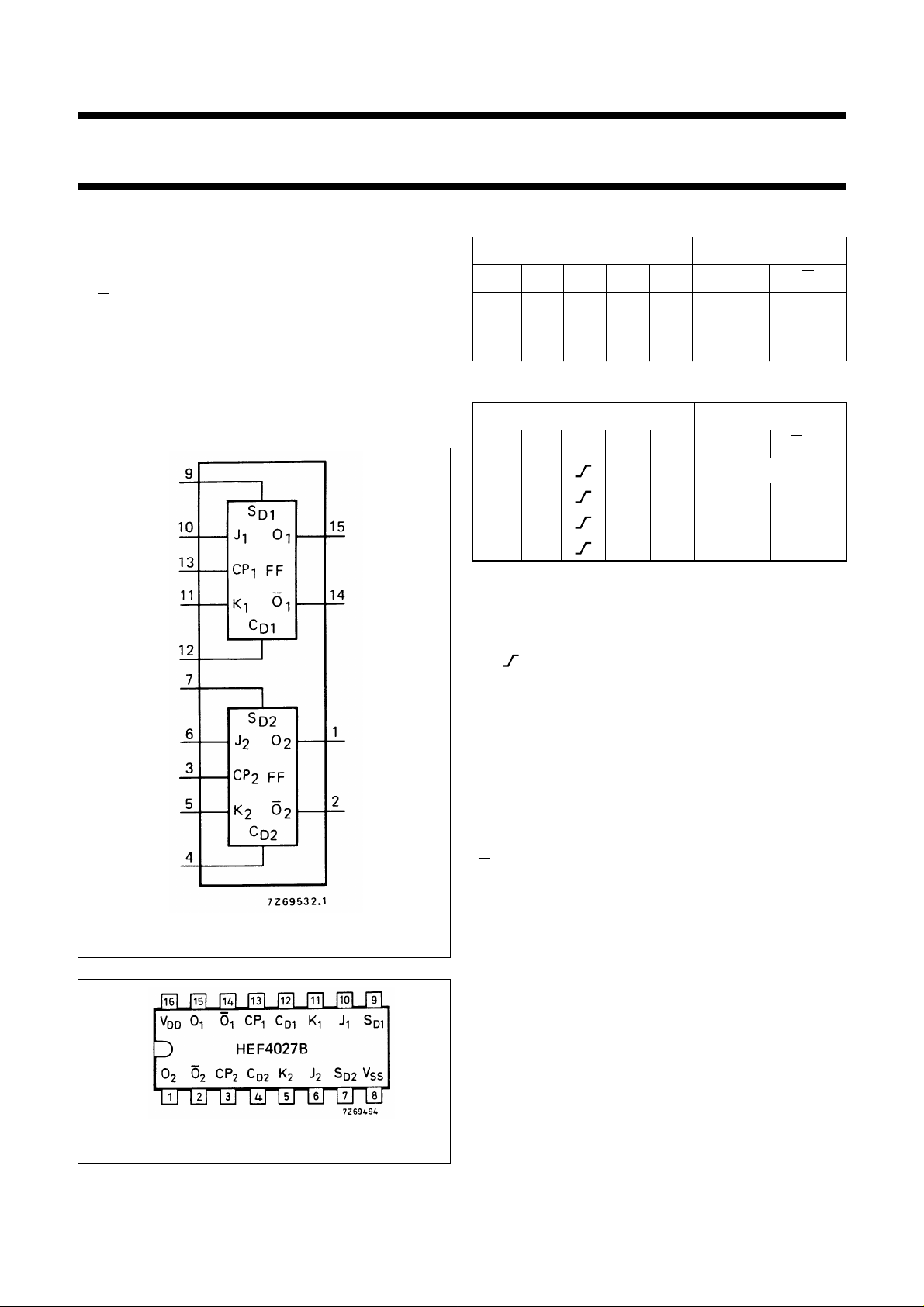

DESCRIPTION

The HEF4027B is a dual JK flip-flop which is

edge-triggered and features independent set direct

(SD), clear direct (CD), clock (CP) inputs and outputs

(O,O). Data is accepted when CP is LOW, and transferred

to the output on the positive-going edge of the clock. The

active HIGH asynchronous clear-direct (CD) and set-direct

(SD) are independent and override the J, K, and CP inputs.

The outputs are buffered for best system performance.

Schmitt-trigger action in the clock input makes the circuit

highly tolerant to slower clock rise and fall times.

HEF4027B

flip-flops

FUNCTION TABLES

INPUTS OUTPUTS

CDCP J K O O

S

D

HLXXX H L

LHXXX L H

HHXXX H H

INPUTS OUTPUTS

CDCP J K O

S

D

n + 1

L L L L no change

LL HL H L

LL LH L H

LL HH

O

n

Notes

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

= positive-going transition

O

= state after clock positive transition

n + 1

O

n + 1

O

n

Fig.1 Functional diagram.

Fig.2 Pinning diagram.

PINNING

J,K synchronous inputs

CP clock input (L to H edge-triggered)

S

asynchronous set-direct input (active HIGH)

D

C

asynchronous clear-direct input (active HIGH)

D

O true output

O complement output

HEF4027BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4027BD(F): 16-lead DIL; ceramic (cerdip) (SOT74)

HEF4027BT(D): 16-lead SO; plastic (SOT109-1)

( ): Package Designator North America

FAMILY DATA, I

LIMITS category FLIP-FLOPS

DD

See Family Specifications

January 1995 2

Loading...

Loading...