Philips HEF4021BP, HEF4021BDB, HEF4021BD, HEF4021BU, HEF4021BT Datasheet

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4021B

MSI

8-bit static shift register

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995 2

Philips Semiconductors Product specification

8-bit static shift register

HEF4021B

MSI

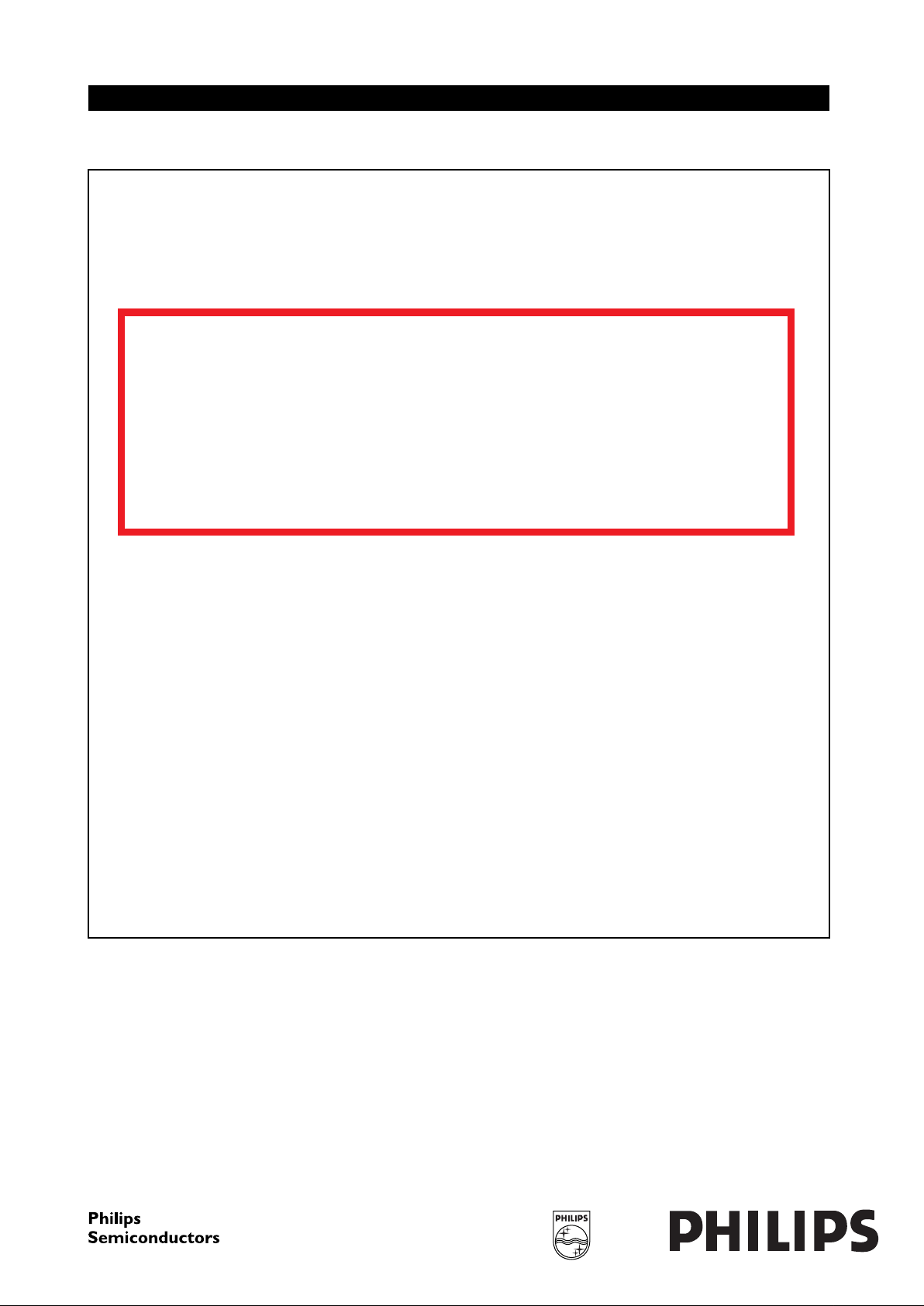

DESCRIPTION

The HEF4021B is an 8-bit static shift register

(parallel-to-serial converter) with a synchronous serial

data input (DS), a clock input (CP), an asynchronous active

HIGH parallel load input (PL), eight asynchronous parallel

data inputs (P0to P7) and buffered parallel outputs from

the last three stages (05to O7).

Each register stage is a D-type master-slave flip-flop with

a set direct/clear direct input. Information on P

0

to P7is

asynchronously loaded into the register while PL is HIGH,

independent of CP and DS. When PL is LOW, data on

DSis shifted into the first register position and all the data

in the register is shifted one position to the right on the

LOW to HIGH transition of CP. Schmitt-trigger action in the

clock input makes the circuit highly tolerant to slower clock

rise and fall times.

Fig.1 Functional diagram.

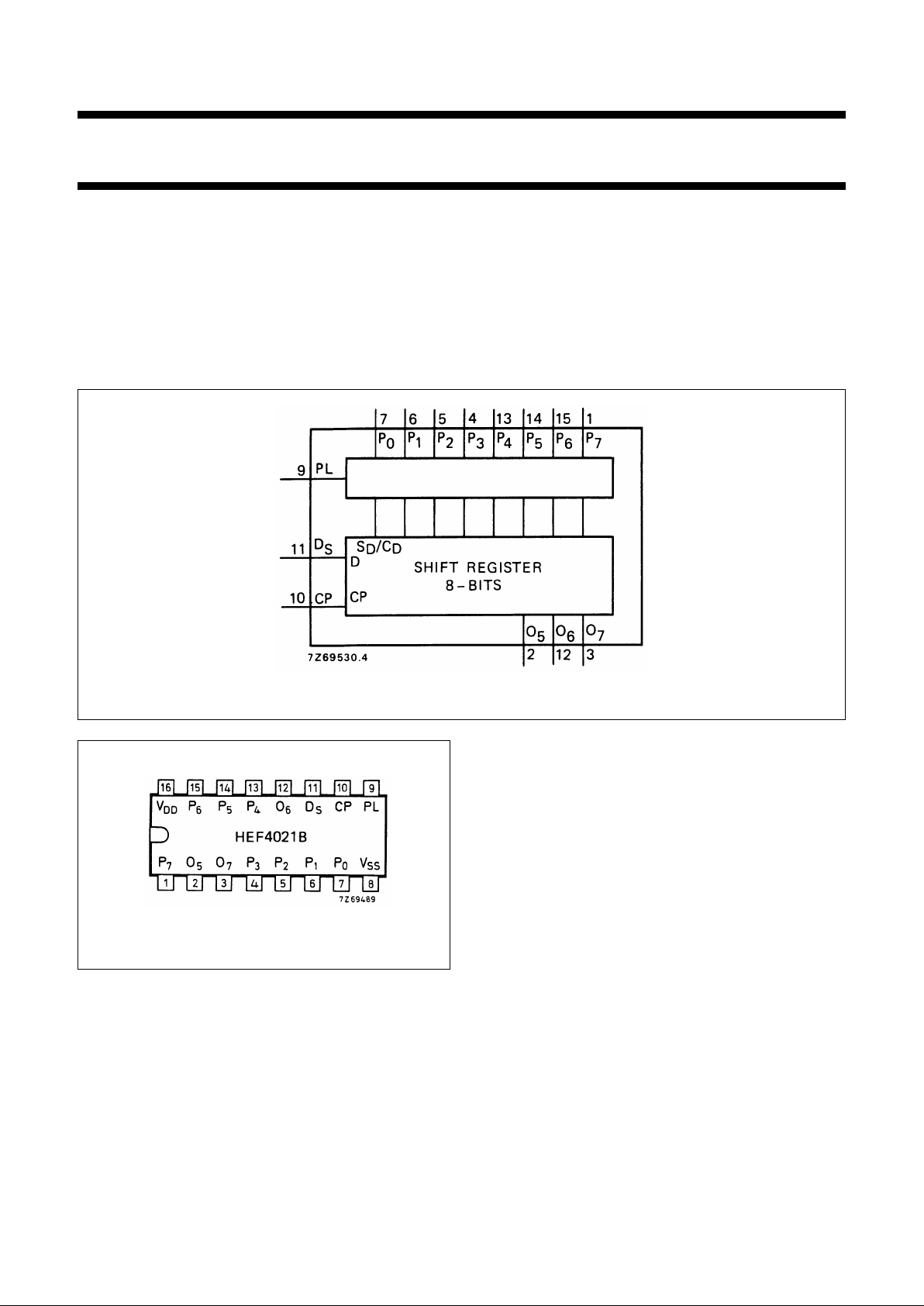

Fig.2 Pinning diagram.

FAMILY DATA, IDDLIMITS category MSI

See Family Specifications

HEF4021BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4021BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4021BT(D): 16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

PINNING

PL parallel load input

P

0

to P

7

parallel data inputs

D

S

serial data input

CP clock input (LOW to HIGH edge-triggered)

O

5

to O

7

buffered parallel outputs from the last three stages

Loading...

Loading...