Philips hef4007ub DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4007UB

gates

Dual complementary pair and

inverter

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors Product specification

Dual complementary pair and inverter

HEF4007UB

gates

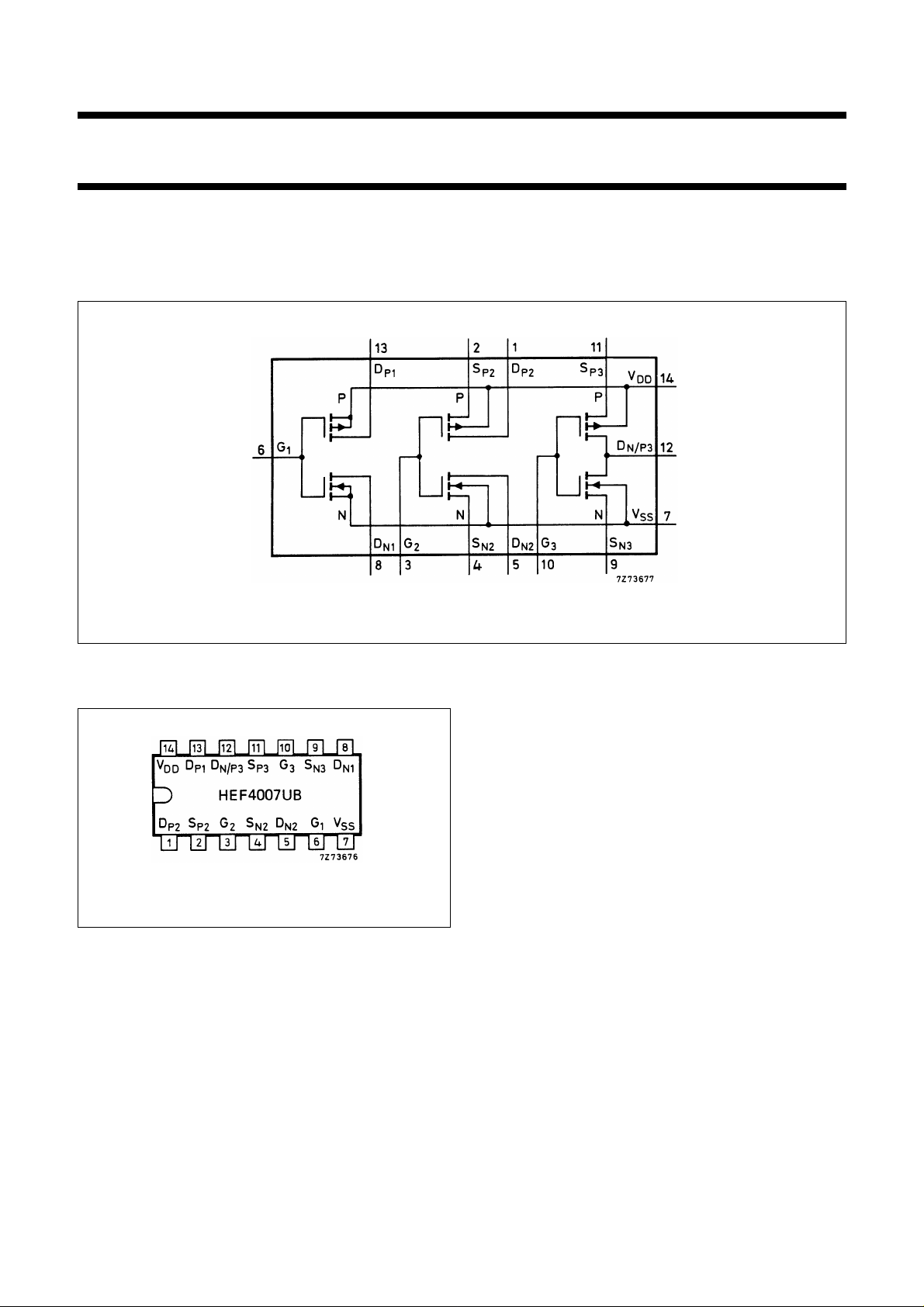

DESCRIPTION

The HEF4007UB is a dual complementary pair and an inverter with access to each device. It has three n-channel and

three p-channel enhancement mode MOS transistors.

Fig.1 Schematic diagram.

Fig.2 Pinning diagram.

HEF4007UBP(N): 14-lead DIL; plastic

(SOT27-1)

HEF4007UBD(F): 14-lead DIL; ceramic (cerdip)

(SOT73)

HEF4007UBT(D): 14-lead SO; plastic

(SOT108-1)

( ): Package Designator North America

PINNING

, S

S

P2

source connections to 2nd and 3rd

P3

p-channel transistors

D

P1

, D

drain connections from the 1st and 2nd

P2

p-channel transistors

D

N1,DN2

drain connections from the 1st and 2nd

n-channel transistors

S

N2,SN3

source connections to the 2nd and 3rd

n-channel transistors

D

N/P3

common connection to the 3rd p-channel

and n-channel transistor drains

G

to G3gate connections to n-channel and

1

p-channel of the three transistor pairs

FAMILY DATA, I

See Family Specifications for V

LIMITS category GATES

DD

IH/VIL

unbuffered stages

January 1995 2

Philips Semiconductors Product specification

Dual complementary pair and inverter

HEF4007UB

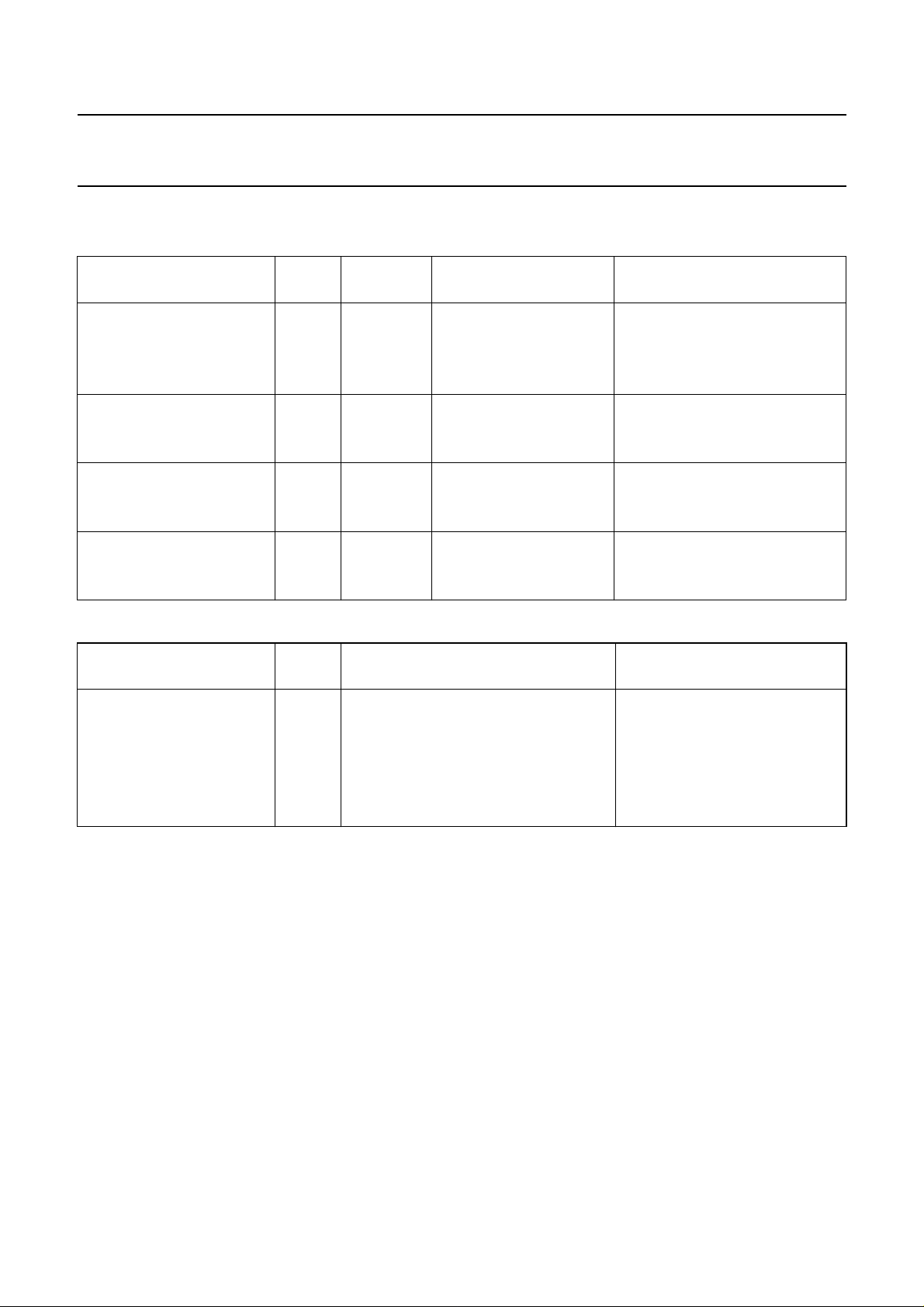

AC CHARACTERISTICS

V

= 0 V; T

SS

Propagation delays

Gn→ DN; D

HIGH to LOW 10 t

LOW to HIGH 10 t

Output transition times 5 60 120 ns 10 ns + (1,0 ns/pF) C

HIGH to LOW 10 t

LOW to HIGH 10 t

=25°C; CL= 50 pF; input transition times ≤ 20 ns

amb

V

DD

V

P

5 40 80 ns 13 ns + (0,55 ns/pF) C

SYMBOL TYP. MAX.

PHL

15 15 30 ns 7 ns + (0,16 ns/pF) C

5 40 75 ns 13 ns + (0,55 ns/pF) C

PLH

15 15 30 ns 7 ns + (0,16 ns/pF) C

THL

15 20 40 ns 6 ns + (0,28 ns/pF) C

5 60 120 ns 10 ns + (1,0 ns/pF) C

TLH

15 20 40 ns 6 ns + (0,28 ns/pF) C

TYPICAL EXTRAPOLATION

FORMULA

20 40 ns 9 ns + (0,23 ns/pF) C

20 40 ns 9 ns + (0,23 ns/pF) C

30 60 ns 9 ns + (0,42 ns/pF) C

30 60 ns 9 ns + (0,42 ns/pF) C

gates

L

L

L

L

L

L

L

L

L

L

L

L

V

DD

V

TYPICAL FORMULA FOR P (µW)

Dynamic power 5 4500 f

dissipation per 10 20 000 f

package (P) 15 50 000 f

+∑(foCL) × V

i

+∑(foCL) × V

i

+∑(foCL) × V

i

DD

DD

DD

2

2

2

where

fi= input freq. (MHz)

fo= output freq. (MHz)

C

= load capacitance (pF)

L

) = sum of outputs

∑(f

oCL

V

= supply voltage (V)

DD

January 1995 3

Loading...

Loading...