Philips DVIO-1.8-DV Service manual

DVD-Video Recorder DVIO 1.8 DV Input Board

General

The DVIO 1.8 DV input board replaces the DVIO 1.5 using a different

chip set.

Attached are the DVIO 1.8 board schematics, layout and parts list for

updating the service manuals of DVDR890 with 12NCs 3122 785

12200 (Euro) and 3122 785 12550 (APAC).

Remarks

The DVIO 1.8 board has been used in the production of the DVDR890

from week 0237 onwards.

The factory change code printed on the type plate of the sets was

increased from VN06 to VN07.

EU models:

- DVD890/001/021/051

APAC models:

-DVDR890/131/691/971

Contents Page

1 Waveforms 3

2 Circuit Diagrams And PWB Layouts Diagram PWB

DVIO 1.8 Board: 1394 Interface (Diagram 1) 4 9

DVIO 1.8 Board: Link + Codec (Diagram 2) 5 9

DVIO 1.8 Board: uP Part (Diagram 3) 6 9

DVIO 1.8 Board: Interface + DAC (Diagram 4) 7 9

DVIO 1.8 Board: Clock (Diagram 5) 8 9

3 Alignments 13

4 Circuit-, IC Descript. and 14

List of Abbreviations 47

5 Spare Part List 48

©

Copyright 2002 Philips Consumer Electronics B.V. Eindhoven, The Netherlands.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic,

mechanical, photocopying, or otherwise without the prior permission of Philips.

Published by GH 0261 Serv ice PaCE Printed in the Netherlands Subject to modification EN 3122 785 40660

EN 2 DVIO 1.8 DV

Personal Notes:

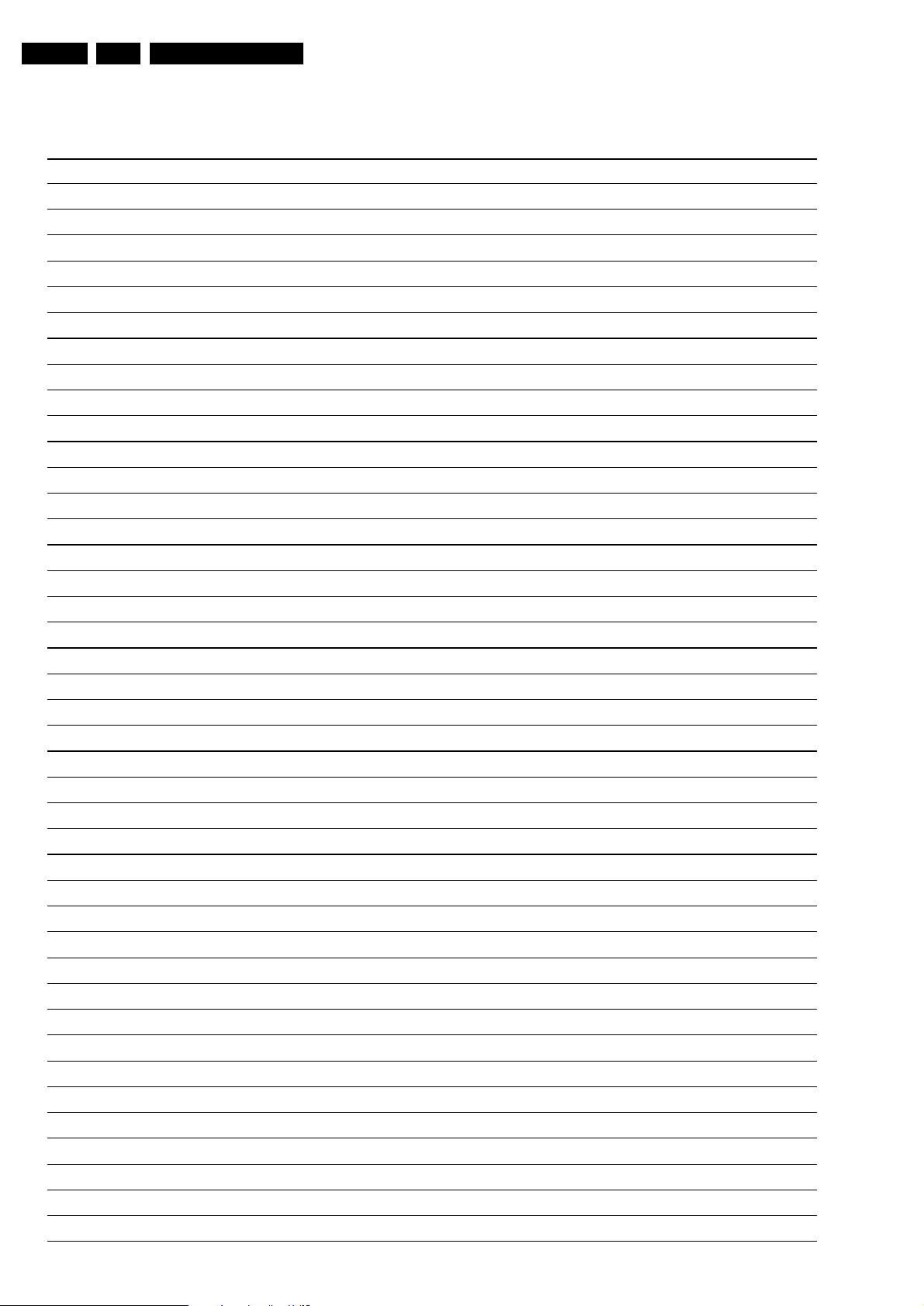

1. Waveforms

F410

Waveforms

Waveforms DVIO

F411

EN 3DVIO 1.8 DV 1.

F400/F401

A: DC, 1 V/Div, 20ns/Div

F800

A: DC, 500mV/Div, 50ns/Div

F529

A: DC, 1 V/Div, 20ns/Div

A: DC, 1 V/Div, 20ns/Div

F801

A: AC, 500mV/Div, 50ns/Div

F551

A: DC, 1 V/Div, 200ns/Div

A: DC, 1 V/Div, 20us/Div

F527

A: DC, 2 V/Div, 20ns/Div

F552

A: DC, 1 V/Div, 5us/Div

F536

A: DC, 1 V/Div, 5us/Div

F609

A: DC, 1 V/Div, 200us/Div

F603

A: DC, 1 V/Div, 20ns/Div

F620

A: DC, 1 V/Div, 10ns/Div

Figure 1-1

F610

A: DC, 1 V/Div, 20ns/Div

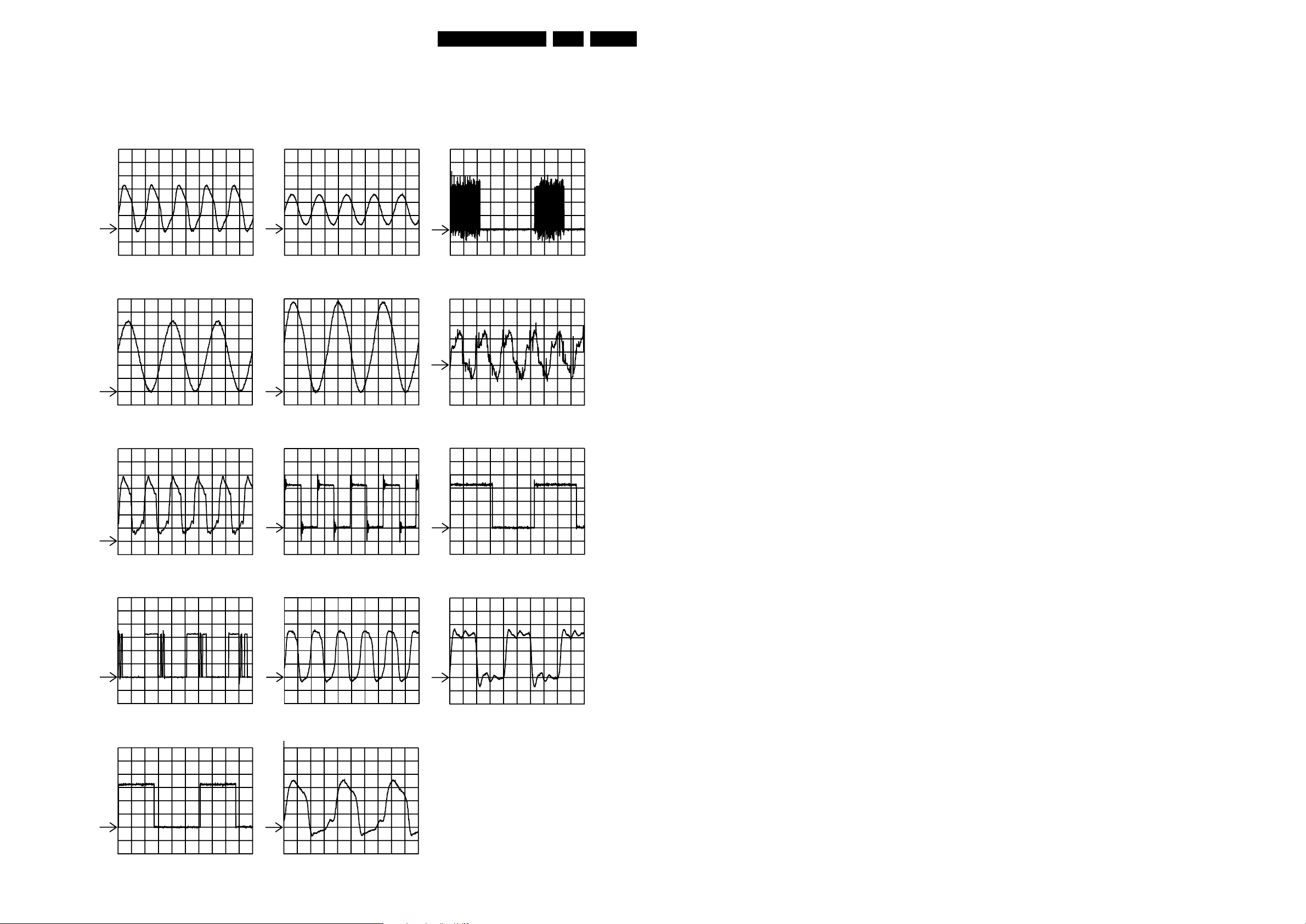

Circuit Diagrams and PWB Layouts

2. Circuit Diagrams and PWB Layouts

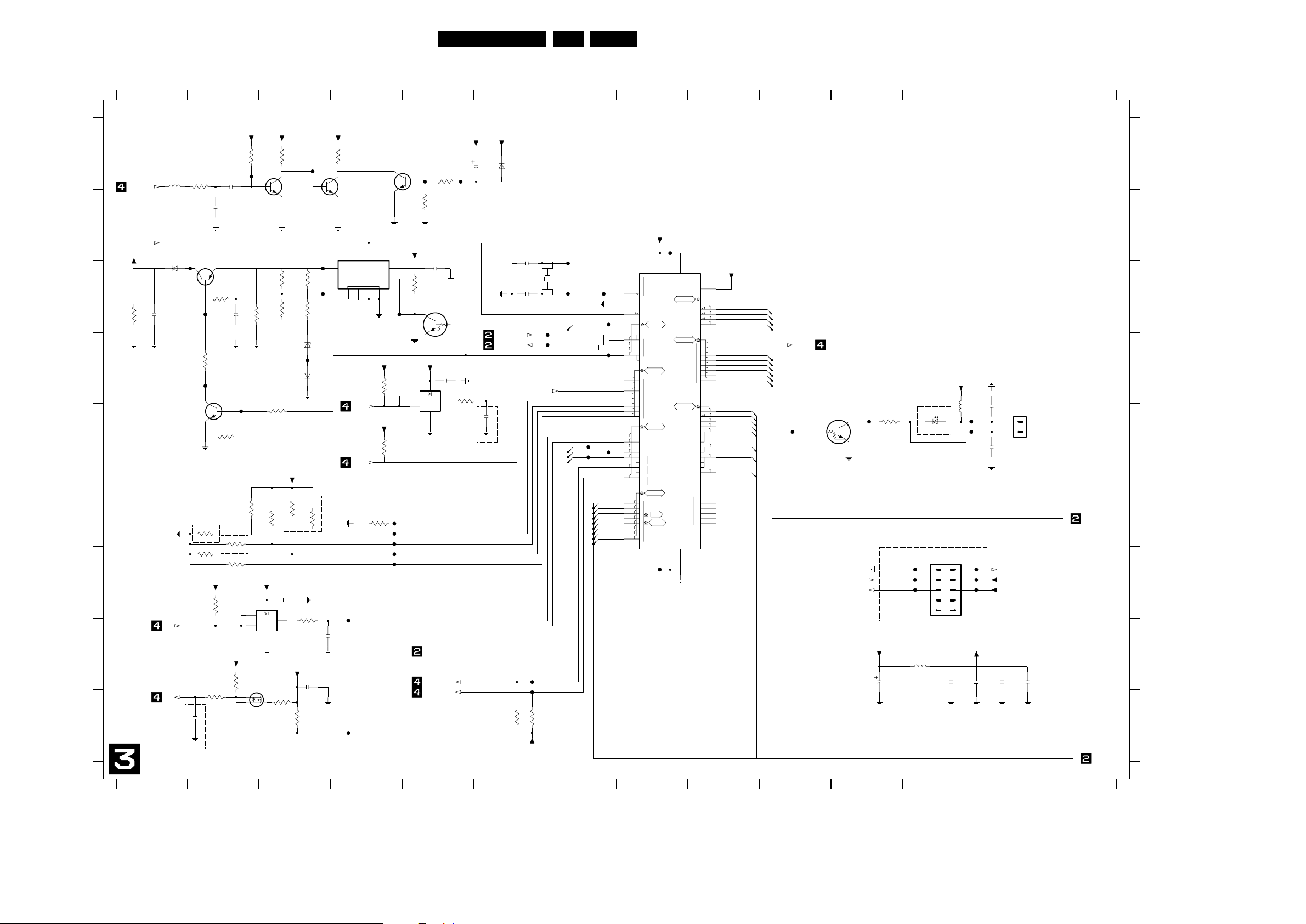

DVIO 1.8 Board: 1394 Interface

EN 4DVIO 1.8 DV 2.

A

B

C

D

E

F

3V3

1

1394 INTERFACE

F0106

GND

FROM FRONT

DV INPUT PCB

5400

100MHZ

47u

2403

GND

5401

100MHZ

47u

2415

GND

1

5678

2

1901

4

F0104

3

2

1

F0102

3404

F0103

1%

56R

F0101

3405

1%

56R

F402

5K1

3406

270p

2402

GND

F409

2404

GND

100n

2405

GND

2406

GND

100n

2407

GND

100n

F414

2417

100n

2418

100n

100n

2416

GND

GND

GND GND

2419

GND

234

3402

F122

100n

100n

1%

56R

3401

2401

GND

3V3_A

2408

GND

3V3_D

2420

GND

1%

56R

1u

100n

100n

to be 9K1 0.5%

34

7400

UPD72852

39 TPA0P

TPA0N

38

37 TPB0P

36 TPB0N

46 TPA1P

45 TPA1N

44 TPB1P

43 TPB1N

TPBIAS041

TPBIAS148

RI134

XI23

XO22

3409

8K2

F411

2413

GND

1400

CX-11F

24M576

10p

F423

F413

2412

GND

10p

4402

GND

F410

56

47

AVDDDVDD

3V3_A

31

40

LINK

INTERFACE

I/O

25

CABLE

PORT0

CABLE

PORT1

3V3_D

4

10

20

56

60

ARBITRATION

AND CONTROL

STATE MACHINE

54

LOGIC

789

CMC 30

PC0 26

PC1 27

PC2 28

SPD

TEST

LREQ 63

LPS 59

DIRECT 50

SCLK 2

LKON 58

CTL0 5

CTL1 6

F421

4401

19SUS|RES

61

62

F416

3403

F417

22R

3400

F424

F415

10K

F418

3414

22R

F419

3416

F420

22R

F400

8D0

3418

F401

9D1

22R

F403

11D2

F404

12D3

F405

14D4

F406

15D5

F407

17D6

F408

18D7

3424

22R

VOLTAGE

AND

CURRENT

GENERATOR

CRYSTAL

OSCILLATOR

PLL

SYSTEM

AND

TRANSMIT

CLOCK

GENERATOR

57

64

16

21

RECEIVE DATA

DECODER AND

TRANSMIT DATA

ENCODER

7

13

RETIMER

1

29

IC(AL)1

51

IC(AL)2

3

IC(DL)

RESETB 55

CABLE

POWER

STATUS

AGNDDGND

35

42

49

52

53

33

CPS 32

24

F425

F422

3408

GND

F412

GND

GND

567

3V3_A

3407

3420

22R

3422

22R

100K

10K

GND

3V3_D

3V3_D

GND

3410

22R

3413

22R

3415

22R

3417

22R

3419

22R

3421

22R

3423

22R

2400

GND

GND

100n

8

{CTL0,CTL1,SCLK,LKON,LPS,LREQ}

LREQ

LPS

LPS

3V3_A

SCLK

LKON

CTL0

CTL1

PHY_D(0)

PHY_D(1)

PHY_D(2)

PHY_D(3)

PHY_D(4)

PHY_D(5)

PHY_D(6)

PHY_D(7)

3411

GND

3V3_D

7401

74LVC1GU04

5

2

4

1

3

GND

10K

only for development

PHY_D(0:7)

6401

TLMH3100

only for development

9

3V3_D

3412

330R

1400 F3

1901 B1

2400 F8

2401 C2

2402 C2

2403 E1

2404 E1

2405 E2

2406 E2

2407 E2

2408 E2

A

2412 F4

2413 F3

2415 F1

2416 F1

2417 F2

2418 F2

2419 F2

2420 F2

3400 C8

3401 C2

3402 C2

3403 B8

3404 C2

3405 C2

B

3406 C2

3407 A8

3408 F7

3409 F3

3410 C8

3411 C9

3412 E9

3413 C8

3414 C8

3415 C8

3416 C8

3417 C8

3418 D8

C

3419 D8

3420 D8

3421 D8

3422 D8

3423 D8

3424 D8

4401 B7

4402 E4

5400 E1

5401 F1

6401 F9

7400 A4

7401 E8

D

F0101 B2

F0102 B2

F0103 B2

F0104 B2

F0106 A1

F122 C2

F400 C7

F401 D7

F402 C2

F403 D7

F404 D7

F405 D7

F406 D7

F407 D7

E

F408 D7

F409 E2

F410 E4

F411 E3

F412 F7

F413 E4

F414 F2

F415 C7

F416 B7

F417 C7

F418 C7

F419 C7

F420 C7

F

F421 A7

F422 E7

F423 E4

F424 C7

F425 E7

TR03014_001

090702

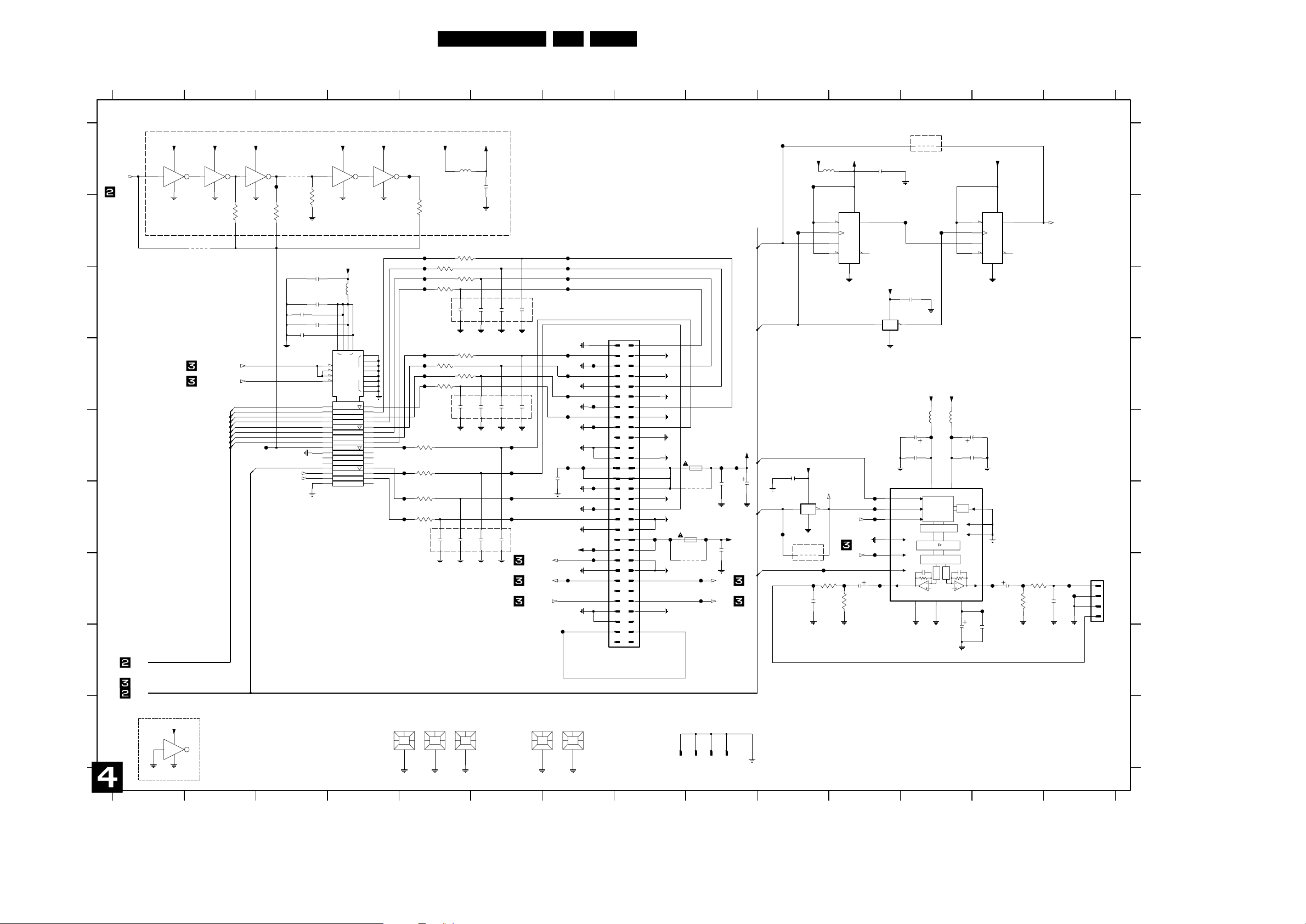

DVIO 1.8 Board: Link + Codec

1

A

B

200 199

PLLAGND

201

PLLDGND

9

GND

3456

10K

3457

10K

3458

10K

3459

10K

3460

10K

3462

10K

3465

10K

3463

10K

3455

10K

3464

10K

3466

10K

3467

10K

3468

10K

3469

10K

3454

35

56

68

82

3.3GND

99

131

148

173

188

39

91

144

2.5GND

195

32 TSSUB1

28 TSERROR1

SYNC130

C

D

E

F

3V3_LINK

G

10K

H

CLK27M_CON

HS_CLK

MD(12)

10K

3442

MD(11)

3441

10K

MD(10)

10K

3440

MD(9)

3439

10K

MD(15)

MD(14)

10K

3445

10K

10K

3444

MD(13)

3443

10K

I

3V3_LINK

145

23

{SCLK,CTL0,CTL1,LREQ,LPS,LKON}

LPS

LKON

LREQ

18LINKON

17LPS

16LREQ

IEEE 1394 LINK CORE

SELECTOR

29 TSRW1

23 STREAM14

24 STREAM15

25 STREAM16

26 STREAM17

21 STREAM12

27 PACKETEN1

MD(8)

10K

3438

22 STREAM13

ALRCK

10K

3426

GND

3563

1R

{APWM,AMCLK44,AMCLK48}

MD(7)

MD(6)

MD(5)

10K

3435

3437

10K

10K

3436

ABCK

3427

MD(4)

10K

3434

23

Circuit Diagrams and PWB Layouts

45 89

PHY_D(0:7)

CTL0

CTL1

SCLK

15

SCLK

20 STREAM11

10K

MD(0:15)

MD(3)

3433

10K

13CTL0

12CTL1

STREAM1019

38 TSSUB2

F432

10K3562

GND

PCM1

10K

3428

MD(2)

10K

3432

PHY_D(7)

PHY_D7 2

37 SYNC2

34 TSERROR2|HSYNC

F431

3471 10K

PCM2

3429

MD(1)

3431

10K

PHY_D(0)

PHY_D(1)

PHY_D(2)

PHY_D(3)

PHY_D(4)

PHY_D(5)

PHY_D(6)

6PHY_D4

8

11PHY_D0

PHY_D2

PHY_D3 7

PHY_D5 4

PHY_D6 3

PHY_D1 10

SELECTOR

STREAM26|VD646

STREAM22|VD242

STREAM24|VD4

36 TSRW2|FLD

44

45 STREAM25|VD5

47 STREAM27|VD7

33 PACKETEN2|VSYNC

YUV(7)

YUV(7:0)

GND

10K

MD(0)

3430

40 STREAM20|VD0

41 STREAM21|VD1

43 STREAM23|VD3

YUV(6)

YUV(5)

YUV(4)

YUV(3)

YUV(2)

YUV(1)

YUV(0)

MD(0)

MD(1)

MD(2)

MD(3)

MD(4)

MD(5)

{AFS1,AFS2,ALRCK,ABCK,AEMP1,PCM1,PCM2}

MD(6)

MD(7)

MD(8)

MD(9)

MD(10)

MD(11)

MD(12)

MD(13)

MD(14)

MD(15)

3531

22R

3533

22R

3537

22R

3541

22R

3545

22R

3549

22R

3553

22R

3556

22R

AFS2

49 AFS2

VD[7:0]

VSYNC

HSYNC

FLD

48 AFS1

AFS1

53 VPWM

3532

22R

3535

22R

3539

22R

3543

22R

3547

22R

3551

22R

3555

22R

3558

22R

TSSUB

51 VCLKO

SYNC

50 VCLKI

APWM

PACKETEN

94 ABCK

93 ALRCK

ALRCK

ABCK

40

33

37

TSRW

STREAM[7:0]

100 AEMP2

2 DQ0

DQ13

DQ25

DQ36

DQ48

DQ59

DQ611

DQ712

DQ839

DQ9

DQ1042

DQ1143

DQ1245

DQ1346

DQ1448

DQ1549

NC

98 AEMP1

AEMP1

22R

97 PCM2

PCM2

3564

3V3_LINK

GND

10K

3446

F440

206IC3

208IFIROME

IC4 207

BLOCK

96 PCM1

101 AMCLKO

102 APWM

103 AMCLK44

104 AMCLK48

PCM1

AMCLK48

AMCLK44

LWE

LDQM

OUTPUT BUFFER

104147

GND

3449

10K

F441

203IC1

IC2 205

TEST

MD13

72 MD14

73 MD15

70 MD12

71

MD(15)

MD(14)

MD(13)

MD(12)

MD(0:15)

VDDQ

I/O CONTROL

512Kx16

512Kx16

SENSE AMP

COLUMN

DECODER

LATENCY &

BURST LENGTH

PROGRAMMING

REGISTER

LWCBR

GND

HS_CLK

RESTB

1K

3453

F443

202HS_CLK

197HCLKSEL

RESETB 1

SYSTEM

CONTROL

DV CODEC

MD864

66 MD10

69 MD11

65 MD9

MD(11)

MD(10)

MD(9)

MD(8)

MD(7)

3V3_RAM

DATA INPUT

REGISTER

VSSVSSQ

26504

3V3_LINK

GND

47K

3461

3470

GND

PD(15)

PD(14)

F438

143P_D15

105PSSEL0

106PSSEL1

P_D14 142

MD257

MD358

MD459

MD560

MD661

MD155

MD7

62

MD(6)

MD(5)

MD(4)

MD(3)

MD(2)

MD(1)

7430

MT48LC1M16A1TG

1257133844

VDD

SELECT

ROW DECODER

ROW BUFFER

REFRESH COUNTER

LRAS

LCBR

COL. BUFFER

LRAS

LCBR

LCAS

LWE

LQDM

EN 5DVIO 1.8 DV 2.

67

PD(0)

AD(10)

125P_D0

HOST

MA079

MWE

MA(0)

MA(11)

22R

22R

22R

22R

22R

22R

22R

22R

AD(9)

116AD10

74 MWE

MCAS

MA(0:11)

MA(10)

115

AD9

75 MCAS

MA(0)

MA(1)

MA(2)

MA(3)

MA(4)

MA(5)

MA(6')

MA(7)

MA(8)

MA(9)

AD(8)

114AD8

76 MRAS

MRAS

PD(0:15)

AD(7)

AD(6)

AD(5)

AD(4)

AD(3)

110AD4

112AD6

AD3 109

AD5 111

AD7 113

177 WRZ

176 RDZ

77 MCLK

MCLK

{MCAS,MRAS,MCLK,MWE}

MCLK

MRAS

MCAS

MWE

10K

1905

1

2

only for development

PD(9)

PD(8)

PD(7)

PD(6)

PD(5)

PD(4)

PD(3)

PD(2)

134

P_D7

133P_D6

PD(1)

126P_D1

P_D2 128

P_D3 129

P_D4 130

P_D5 132

PD(13)

141

P_D13

PD(12)

P_D12 139

PD(11)

138P_D11

PD(10)

P_D10 137

136P_D9

P_D8 135

INTERFACE

CORE

MA9

MD054

MA11

89

90 MA10

92

MD(0)

MA(11)

MA(10)

MA(9)

BANK

ADDRESS REGISTER

A10 20

LCKE

CLK 35

CKE 34

CS_

RAS_ 17

CAS_ 16

WE_ 15

TIMING REGISTER

DQML 14

MA888

MA(8)

MA(7)

A0 21

A1 22

A2 23

A3 24

A4 27

A5 28

A6 29

A7 30

A8 31

A9 32

MA281

MA585

MA686

83 MA3

84 MA4

87 MA7

80 MA1

MA(6)

MA(5)

MA(4)

MA(3)

MA(2)

MA(1)

3530

19BA

22R

3534

3536

22R

3538

3540

22R

3542

3544

22R

3546

3548

22R

3550

3552

22R

3554

3557

22R

18

3559

3560

3561

22R

36DQMH

67

{INT,IOR,RWZ,CS}

INT

AD(1:10)

AD(2)

AD(1)

124INT

108AD2

AD1 107

192 D12

193 D13

194 D14

196 D15

D(15)

D(14)

D(13)

D(12)

3447

10K

3451

10K

CS

IOR

RWZ

3V3_LINK

342510K

F439

F442

151SCS|P45

PORT4

CTRL

172 A15

174 A16

175 A17

A(15)

A(17)

A(16)

D(0:15)

7432

M29W800AT

37

SIO_CNTI

SIO_CNTO

MEMORY

169 A13

171 A14

A(14)

A(13)

11

VCC

SI|P41 146

<SCI>

A12

168

A(12)

GND

W_

145SO|P40

SERIAL

INTERF

167 A11

A(11)

F433

26

147SCK|P42

165 A10

A(10)

E_

164 A9

A(8)

A(9)

28

G_

D(0)

3489

120IOR

123

IOCHRDY

191 D11

190 D10

D(11)

D(10)

3452

10K

3448

INTC

10K

119RWZ

155P34

204P30

152P31

153P32

154

122DMAREQ

117CS

P33

DMAACK 121

PORT3

D5183

D2180

184 D6

185 D7

186 D8

189 D9

181 D3

182 D4

178 D0

179 D1

D(9)

D(8)

D(7)

D(6)

D(5)

D(4)

D(3)

D(2)

D(1)

D(0)

3V3_F

3V3_RAM

GND

89

3474

1K

3450

10K

3477

10K

3475

10K

149TXD|P43

150RXD|P44

SERIAL

INTERF

<UART?>

60K BYTE

HIGH-SPEED

INTERNAL RAM

A7162

161 A6

163 A8

A(6)

A(7)

F434

12

RP_

D(1)

10K

3481

10 11

3472

1K

3478

1K

3473

10K

3476

10K

7431

UPD72893

PLLAVDD

198

PLLDVDD

5

31

52

UNIT D

<TMD>

16-BIT TIMER

63

78

3.3VDD

95

127

140

CPU

CORE

166

187

14

67

192K BYTE

HIGH-SPEED

INTERNAL ROM

118

2.5VDD

170

A2157

A4

156 A1

159

160 A5

158 A3

A(1)

A(2)

A(3)

A(4)

A(5)

3V3_F

A(1)

47

25

15

R-B_

D(2)

3490

10K

BYTE_

DQ0

29

D(0)

D(3)

10K

3482

A0

DQ1

DQ233DQ335DQ438DQ5

31

D(2)

D(1)

D(5)

D(4)

10K

3491

10K

3483

10 11

A(1:17)

A(4)

A(3)

A(2)

24

A223A322A421A520A6

A1

D(4)

D(3)

D(8)

D(7)

D(6)

10K

3493

3492

10K

10K

3484

GND

GND

3V3_LINK

2V5

3V3_LINK

2V5

A(5)

DQ6

40

42

D(6)

D(5)

D(9)

10K

3485

3V3

2431

GND

3V3

A(7)

A(6)

19

DQ744DQ830DQ9

D(7)

D(10)

3494

10K

D(8)

D(11)

10K

3486

3V3

2449

GND

47u

A(8)

18

A7

D(12)

3495

10K

IN OUT

100n

5432

100MHZ

5433

100MHZ

A(9)

A88A9

32

D(9)

D(13)

10K

3487

7433

LF25C

GND

GND

A(10)

7

DQ10

34

D(10)

D(14)

3496

10K

F430

100MHZ

10u

2450

GND

3V3_LINK

F435

100n

2432

GND

2436

100n

2439

GND

A(14)

A(13)

A(12)

A(11)

A106A115A124A133A142A15

DQ11

DQ12

DQ1341DQ14

36

39

43

45

D(15)

D(14)

D(13)

D(12)

D(11)

D(15)

10K

10K

3488

12 13

10K

3499

GND

10K

3497

2V5

2451

100n

2452

GND

100n

5431

GND

2437

100n

2434

2433

100n

2435

100n

F437

2444

100n

100n

100n

A(16)

A(15)

1

DQ15|A-1

9

2441

A(17)

101314

GND

16

A1648A1717A18

VSS1

VSS2

NC

2446

not used

27

46

LINK + CODEC

12

F0201

GND

F0202

F0203

F0204

+5V

2454

100n

3V3_LINK

2455

100n

2440

100n

F0205

100n

2442

2456

2453

3498

GND

100n

10K

100n

2438

3V33V3_RAM

5434

100MHZ

100n

100n

2447

not used

not used

3479

GND

GND

13 14

100n

not used

47K

1

2

3

4

5

100n

F436

3480

14

1902

2443

3V3_F

1K

DV_STATUS

only for development

2445

100n

100n

2448

GND

100n

RESTB

1902 B14

1905 A6

2431 D11

2432 D12

2433 D12

2434 D12

2435 D12

2436 E12

2437 D13

2438 D13

2439 E12

2440 D13

2441 E12

2442 D14

A

2443 D14

2444 E12

2445 D14

2446 E13

2447 E13

2448 E14

2449 C11

2450 C12

2451 C12

2452 C13

2453 C13

2454 C13

2455 C13

2456 C14

B

3425 A8

3426 H2

3427 H2

3428 H2

3429 H3

3430 I3

3431 I2

3432 I2

3433 I2

3434 I2

3435 I2

3436 I2

3437 I2

C

3438 I1

3439 I1

3440 I1

3441 I1

3442 I1

3443 I1

3444 I1

3445 I1

3446 B4

3447 H7

3448 I8

3449 B5

3450 A9

D

3451 I8

3452 H8

3453 A5

3454 G1

3455 E1

3456 E1

3457 F1

3458 F1

3459 F1

3460 G1

3461 A5

3462 G1

3463 E1

E

3464 F1

3465 F1

3466 F1

3467 F1

3468 G1

3469 G1

3470 A6

3471 F3

3472 A10

3473 A10

3474 A9

3475 B9

3476 A10

3477 A9

F

3478 A10

3479 G14

3480 G14

3481 I9

3482 I10

3483 I10

3484 I10

3485 I11

3486 I11

3487 I11

3488 I11

3489 I9

3490 I10

G

3491 I10

3492 I10

3493 I10

3494 I11

3495 I11

3496 I11

3497 B13

3498 B13

3499 A13

3530 F7

3531 F4

3532 F4

3533 F4

H

3534 F7

3535 G4

3536 G7

3537 G4

3538 G7

3539 G4

3540 G7

3541 G4

3542 G7

3543 G4

3544 G7

3545 G4

3546 G7

I

3547 G4

3548 G7

3549 H4

3550 H7

3551 H4

3552 H7

3553 H4

3554 H7

3555 H4

3556 H4

3557 H7

TR03015_001

090702

3558 H4

3559 I7

3560 I7

3561 I7

3562 F2

3563 H2

3564 E4

5431 C12

5432 D11

5433 E11

5434 E14

7430 F6

7431 B10

7432 H9

7433 C11

F0201 B14

F0202 B14

F0203 B14

F0204 B14

F0205 B14

F430 C12

F431 F3

F432 F2

F433 G9

F434 G9

F435 D12

F436 E14

F437 E12

F438 B5

F439 B9

F440 B4

F441 B5

F442 B8

F443 B5

DVIO 1.8 Board: uP Part

123

uP- Part

A

5802

BAS316

2811

not used

RXD

TXD

10u

6803

F837

7811

BC847BW

GND

2819

GND

3838

1K

not used

GND

7810

BC857BW

F838

3839

F831

GND

3804

10K

3806

10K

3V3_uP

3826

100R

22p

not used

2822

RESETn

B

RESET_FM

VPP

C

10n

10K

3801

GND

GND

D

E

F

G

H

I

156

Circuit Diagrams and PWB Layouts

45

3815

3816

6801

F834

6802

GND

10K

3825

100R

2818

100n

10K

F827

F832

330R

F833

1K

BZX384-B5V1

BAS316

3813

GND

1%

1%

to be 1%

not used

10K

2817

GND

not used

GND

3V3_uP

3819

GND

7801

LM2931D

4

22p

1K

7804

BC847BW

VOUT

ADJ

GND

F826

F806

CTSN

GND

ISPN

7803

BC847BW

VIN

INHIBIT

2367

GND

3V3_uP

3831

3V3_uP

3832

3803

10K

GND

81

5

F835

7806

PDTC144EU

100K

10K

F822

F823

F824

F825

F804

+12V

GND

7809

74LVC1G32

1

2

3814

2K2

3822

4K7

3836

4K7

2813

100n

1n

100K

2805

GND

3805

10K

3807

10K

+5V

F839

7807

74LVC1G32

3829

3V3_uP

3820

F830

47u

GND

3810

not used

1

2

7808

47K

BSH111

47K

3821

10K

3V3_uP

10K

5

GND

3

3V3_uP

3835

1K

3812

3817

GND

3823

3824

10K

2816

100n

3827

10K

10K

7805

BC847BW

1%

1K

1%

3K9

3V3_uP

3811

4

3V3_uP

3837

234

3809

F829

3802

GND

2806

100n

10K

3V3_uP

5

3

GND

BUFENn_VID

BUFENn_AUD

F836

3818

10K

22K

GND

2820

100n

4

{CS,RWZ,IOR,INT}

3828

100R

3V3_uP

2814

VCTL

GND

EN 6DVIO 1.8 DV 2.

6 7 11 12 13 14

3V3_uP

22u

6804

BAS316

2821

GND

not used

GND

DV_STATUS

22p

2801

27p

2802

27p

RESTB

F808

F809

RESETn

1800

CX-5F

F800

6M

F801

UPD78F0988A

F811

3808

GND

F819

INT

F810

CS

F817

RWZ

F820

IOR

F818

PD(0)

PD(1)

PD(2)

PD(3)

PD(4)

PD(5)

PD(6)

PD(7)

F816

F815

10K

10K

3833

3834

3V3_uP

78910

8910

3V3_uP

F805

7802

41

40

34

36

43

44

37

38

33

32

31

30

29

28

27

26

17

18

19

20

21

22

23

57

58

59

60

61

62

63

64

1

XTAL

2

AVREF

RESET

TOFF7

0

1

INTP

2

3

ADTRG

0

1

2

3

ANI

4

5

6

7

RXD00

TXD00

RXD01

TXD01

TO

TI

TO

TI

TO

TI

0

1

2

3

4

5

6

7

P0<0:3>

P1<0:7>

P2<0:6>

0

1

2

P4<0:7>

ADR

DATA

10

24

35

Φ

CPT

TEST

P6<4:7>

WR

WAIT

ASTB

P3<0:7>

RTP

P5<0:7>

SCK

INTP4

TI000

TO00

INTP5

TI010

INTP6

TO001

TO01

INTP7

TO

9

25

42

F812

GND

VPP

39

PD(8)

PD(9)

PD(10)

PD(11)

PD(12)

PD(13)

PD(14)

PD(15)

AD(7)

AD(8)

AD(9)

AD(10)

AD(1)

AD(2)

AD(3)

AD(4)

AD(5)

AD(6)

A_MUTE

F803

53

RD

54

55

56

45

0

46

1

47

2

48

3

49

4

50

5

51

6

52

7

1

2

3

SI

4

SO

5

6

7

8

11

70

12

71

13

72

14

73

15

74

16

75

+5V

F802

7800

PDTC144EU

3800

330R

only for development

TLMH3100

6800

5800

GND

AD(1:10)

1904

RF

GND

TXD

RXD

3V3

not used

F0401

1

F0403

34

F0405

56

78

9

2

10

3V3_uP

F0402

F0404

F0406

5801

100MHZ

PD(0:15)

2807

GND

47u

2808

GND

100n

11 12 13

F0301

F0302

2809

GND

GND

GND

100n

2803

2804

100n

100n

RESET_FM

3V3_uP

VPP

2810

GND

1

2

100n

1903

2812

GND

PH-S

To front DV input PCB

100n

14

A

B

C

D

E

F

G

H

I

TR03016_001

090702

1800 C6

1903 E13

1904 G12

2801 B6

2802 C6

2803 E13

2804 E13

2805 C2

2806 C5

2807 H11

2808 H12

2809 H12

2810 H13

2811 C1

2812 H13

2813 A2

2814 A5

2816 G3

2817 H3

2818 H3

2819 I2

2820 D5

2821 E6

2822 B2

3800 E11

3801 C1

3802 B5

3803 F4

3804 F2

3805 F2

3806 G2

3807 G2

3808 C7

3809 C5

3810 F2

3811 F3

3812 F3

3813 F3

3814 C2

3815 C3

3816 C3

3817 A3

3818 A5

3819 A4

3820 A2

3821 C2

3822 G2

3823 C3

3824 C3

3825 G3

3826 I2

3827 I3

3828 D5

3829 H2

3831 D4

3832 E4

3833 I6

3834 I6

3835 E3

3836 E2

3837 I3

3838 A2

3839 D2

5800 E12

5801 H12

5802 A1

6800 E12

6801 D3

6802 D3

6803 C1

6804 A6

7800 E11

7801 B4

7802 C8

7803 A4

7804 A4

7805 A3

7806 C4

7807 G2

7808 H2

7809 D5

7810 B2

7811 E1

F0301 E13

F0302 E13

F0401 G12

F0402 G13

F0403 G12

F0404 G13

F0405 G12

F0406 G13

F800 B7

F801 C7

F802 E11

F803 E10

F804 G4

F805 B8

F806 I4

F808 C7

F809 D7

F810 D7

F811 C7

F812 G8

F815 H6

F816 H6

F817 E7

F818 E7

F819 C7

F820 E7

F822 F4

F823 F4

F824 F4

F825 G4

F826 G4

F827 A3

F829 A5

F830 A2

F831 D2

F832 C3

F833 C3

F834 D3

F835 C4

F836 A5

F837 C2

F838 C2

F839 E2

DVIO 1.8 Board: Interface + DAC

123456

Interface + DAC

+3V3_dly +3V3_dly+3V3_dly +3V3_dly

A

CLK27M_CON

7500-A

74LVC04A

B

C

D

E

F

G

H

I

7500-F

74LVC04A

GND

OPTION

12345678

7500-B

74LVC04A

14

1

7

GND

not used

14

2

3

7

GND

4501

BUFENn_VID

BUFENn_AUD

YUV(7:0)

{ALRCK,ABCK,PCM1,AEMP1,AMCLKO}

+3V3_dly

14

13

12

7

GND

7500-C

74LVC04A

4

5

47R

3512

YUV(0)

YUV(1)

YUV(2)

YUV(3)

YUV(4)

YUV(5)

YUV(6)

YUV(7)

GND

Circuit Diagrams and PWB Layouts

+3V3_dly

7500-D

74LVC04A

14

10

7

GND

Clock delay

3V3

5501

100MHZ

31

718 42

VC

EN1

EN2

EN3

GND

EN4

2111

3

1

4

1

Buffer

14

F501

8

9

7

GND

3500

F510

F508

F506

F504

4

10

15

21

28

34

39

45

GND

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

F519

F520

F522

F524

F529

F554

F555

F556

Hole 4.9mm

0003

GND

14

7

ABCK

F527

6

F502

3501

PCM1_NEW

ALRCK_NEW

47R

GND

4500

GND

3511

GND

2502

100n

2504

100n

74LVT16244

GND

7500-E

74LVC04A

47R

2505

100n

2501

100n

2503

100n

7505

1

48

25

24

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

11

3V3

+3V3_dly

5500

100MHZ

2500

100n

47R

GND

3502

3503

47R

3504

47R

47R

3505

47R

18p

18p

2509

not used

GND

GND

2510

2511

GND

3506

47R

3507

47R

3508

3509

47R

47R

18p

18p

2518

2517

2516

not used

GND

GND

3510

GND

47R

3514

47R

3515

47R

3516

47R

not used

18p

2530

GND GND

2531

18p

18p

2532

2533

GND

GND

Shielding connection on mounting holes

0005

0004

GND

GND

F516

F559

F558

F557

EN 7DVIO 1.8 DV 2.

7 8 9 1011121314

F567

3V3 3V3_32KHz

5505

F563

7507-A

74LV74

F565

PCM1

F509

4

3

2

1

F507

F505

F503

18p

18p

2515

1500

GND

F511

F512

F514

18p

18p

2519

F515

GND

F530

2513

100n

GND

18p

RESETn

ISPN

TXD

+12V

F538

F549

179161

1

GND

3

F513

5

GND

78

9

GND

11 12

F518

13 14

GND

15 16

F521

17 18

GND

19

21 22

GND

23 24

F531

25 26

27

F534

29

GND

31 32

F535

33 34

GND

35 36

37 38

GNDGND

39

F562

41 42

F550

43 44

45 46

GND

47 48

49

51 52

53 54

55

57 58

59

2

4

6

10

GND

GND

GND

GND

20

28

30

GND

GND

1502

750mA F

4502

not used

F532

2520

GND

GND

not used

1503

GND

GND

750mA F

4503

F539

F547

F537

2529

CTSN

RXD

F523

F528

40

50

56

60

F533

100n

100n

+5V

2521

ABCK

3V3

ABCK

47u

ALRCK

GND

2534

100n

7501

74LVC1GU04

F517

2

not used

3V3_LINK

5

1

3

GND

ALRCK_NEW

4

PCM1_NEW

4504

F560

AEMP1

F553

F540

3517

100R

10n

2523

220K

GND

GND

GND

A_MUTE

7

14

2514

3519

2527

100n

5

6

3V3_32KHz

7508

74LVC1GU04

2

7506

UDA1334ATS

F551

F552

F536

GND

F561

F54547u

GND

DAC

14

To digital PCB

Hole 3.6 mm

0006

0007

1

1

1

1

1907

GND

1906

GND

1908

1909

GND

not used

4507

GND

F564

F566

2528

100n

5

1

3

GND

4

3V33V3

5504

5503

2506

F525

F526

47u

2508

100n

GND GND

13

1

BCK

2

WS

3

DATAI

SYSCLK|PLL16

MUTE8

9 DEEM|CLKO

VOL

VDDA4VDDD

DIGITAL

INTERFACE

DE-EMPHASIS

INTERPOLATION

NOISE SHAPER

VSSA5VSSD

15

GND

GND

DAC

PLL

FILTER

DAC

VREF-DAC

2525

12

GND

2507

2512

100n

10

11

12

47u

PLL0

VOR

47u

3V3_32KHz

7507-B

74LV74

GND

10

11SFOR0

7SFOR1

GND

16

F544

F548

2526

100n

14

9

PCM1_NEW

813

7

2522

F541

47u

3520

220K

GND

3518

100R

10n

GND

F542

2524

F543

GND

1

2

3

4

PH-S

1501

To analog PCB - Sound Processing

9 1011121314

0003 I4

0004 I5

0005 I5

0006 I6

0007 I7

1500 C7

1501 H14

1502 E9

1503 F9

1906 I8

1907 I9

1908 I9

1909 I9

2500 A6

A

2501 C3

2502 C3

2503 C3

2504 C3

2505 C3

2506 E12

2507 E12

2508 E12

2509 C5

2510 C6

2511 C6

2512 E12

2513 E7

2514 G11

B

2515 C6

2516 D5

2517 D6

2518 D6

2519 D6

2520 F9

2521 F9

2522 G13

2523 G10

2524 G14

2525 H12

2526 H13

2527 A11

C

2528 C12

2529 F9

2530 F5

2531 F5

2532 F6

2533 F6

2534 E10

3500 B5

3501 B3

3502 B5

3503 B5

3504 C5

3505 C5

3506 D5

D

3507 D5

3508 D5

3509 D5

3510 E5

3511 B3

3512 B2

3514 E5

3515 F5

3516 F5

3517 G10

3518 G13

3519 G11

3520 G13

E

4500 A3

4501 B2

4502 F9

4503 G9

4504 G10

4507 A12

5500 A5

5501 C4

5503 E12

5504 E12

5505 A10

7500-A A1

7500-B A2

7500-C A2

F

7500-D A4

7500-E A3

7500-F I1

7501 F10

7505 D4

7506 E11

7507-A B11

7507-B B13

7508 C11

F501 A5

F502 A3

F503 C7

F504 C5

G

F505 C7

F506 C5

F507 B7

F508 B5

F509 B7

F510 B5

F511 D7

F512 D7

F513 D7

F514 D7

F515 E7

F516 E6

F517 F10

F518 D7

H

F519 D5

F520 D5

F521 E7

F522 D5

F523 F8

F524 D5

F525 E12

F526 E12

F527 E3

F528 F8

F529 E5

F530 E7

F531 E7

I

F532 E9

F533 E9

F534 F7

F535 F7

F536 F11

F537 F9

F538 G7

F539 G9

F540 G11

F541 G13

TR03017_001

090702

F542 G14

F543 G14

F544 G13

F545 G11

F547 G9

F548 G13

F549 H7

F550 G7

F551 F11

F552 F11

F553 G10

F554 E5

F555 F5

F556 F5

F557 F6

F558 F6

F559 E6

F560 G10

F561 F11

F562 F7

F563 A10

F564 B12

F565 B10

F566 B12

F567 A10

DVIO 1.8 Board: Clock

Circuit Diagrams and PWB Layouts

EN 8DVIO 1.8 DV 2.

A

B

C

D

E

F

12

HS_CLK

F603

2619

not used

GND

Audio CLOCK

3V3_AC

7606-B

74LV74

14

9

813

7

GND

{APWM,AMCLK44,AMCLK48}

3V3_AC

10

11

12

GND

3601

1R

18p

3618

10K

GND

2616

100n

not used

AMCLK44

AMCLK48

F609

APWM

5V_PLL

3606

3612

GND

3V3_LINK

7600

74LVC1GU04

5

4

1

3

GND

4606

4608

4609

7602

74HCT1G04

2

F605

1%

10K

1%

10K

2605

GND

2

5V_PLL

5

3NC1

GND

100n

F624

2612

100n

180K

F610

3607

34

7601

FXO-31FL

4

OUT

VDD

OSC

GND

2

GND

TS

27MHz

1

3

2600

GND

5602

100MHZ

100n

Host CLOCK

3603

1R

GND

2602

GND

470n

F604

F601

2614

GND

470n

3608

220K

GND

5.1V

2.1V

2.1V

2.4V

2.5V

2.5V

F614

15

16

4

5

6

12

11

13

4

F611

3600

220K

not used

2604

T

3-10p

2618

22p

4602

not used

2615

100n

1%

+5V

4604

2617

GND

7604

BA7082F

3602

IN2

IN1

BW

BWB

FB

CT1

CT2

VCTL

3V3_LINK

not used

100n

+5V

10K

567

F621

F615

3609

GND

10K

560K

3V3_AC

2608

GND

4603

not used

100n

F619

3610

18K

1%

3605

3

15

10

13

9

GND

CLK27M

CLK33M

CLK512FS

CLK16M

CLKA

4605

5600

100MHZ

+

VCO

GND

5V_PLL

10

VCC

GND

8

GND

3V3_AC 3V3

2611

100n

7606-A

14

74LV74

5

61

7

GND

2601

10u

2603

100n

GND

VO

SW1

SW2

SW3

FOUT

SW

1/2

FADJ

14

5.1V

2.6V

3V3_AC

3617

4

3

2

F622

2.4V

1

2

3

7

9

GND

33K

100MHZ

FSEL

FSEL

3604

not used

GND

3V3_AC

5603

2607

100n

1211

DVDD

1/4 PLL1

1/6

1/8

1/4

1/6

DVSS

1R

89

3V3_AC

5601

2609

100n

GND

12

56

7605

BU2288FV

VDD2

AVDD

PLL2

GND

F616

3613

GND

VSS2

XTALO

XTAL

AVSS

2606

1n

5K1

XTALI

TEST

OE

FSEL1

F617

7

8

4

16

F618

14

3V3_AC

7608

74LVC1GU04

2

AFS1

3614

100K

1

GND

F620

F623

10K

3V3_AC

5

3

3616

2613

100n

F606

4

2610

100n

not used

GND

A

B

C

D

E

F

2600 B4

2601 C5

2602 D3

2603 D5

2604 E3

2605 E2

2606 F8

2607 A8

2608 B7

2609 A8

2610 B9

2611 A5

2612 C3

2613 E9

2614 D3

2615 F3

2616 A2

2617 B4

2618 E3

2619 B1

3600 D3

3601 A1

3602 D5

3603 B3

3604 F8

3605 F7

3606 E2

3607 F3

3608 D4

3609 F6

3610 F7

3612 E2

3613 F8

3614 E9

3616 C9

3617 A6

3618 E1

4602 F3

4603 F7

4604 A4

4605 A5

4606 B2

4608 B2

4609 C2

5600 C5

5601 A8

5602 A4

5603 A8

7600 A2

7601 A3

7602 C2

7604 D4

7605 B8

7606-A B5

7606-B D1

7608 F8

F601 D4

F603 A1

F604 F3

F605 D2

F606 F9

F609 D2

F610 B3

F611 D3

F614 D4

F615 F6

F616 F8

F617 F8

F618 B9

F619 B7

F620 B9

F621 B6

F622 C6

F623 B9

F624 F2

123

45

TR03018_001

6

78

9

090702

Circuit Diagrams and PWB Layouts

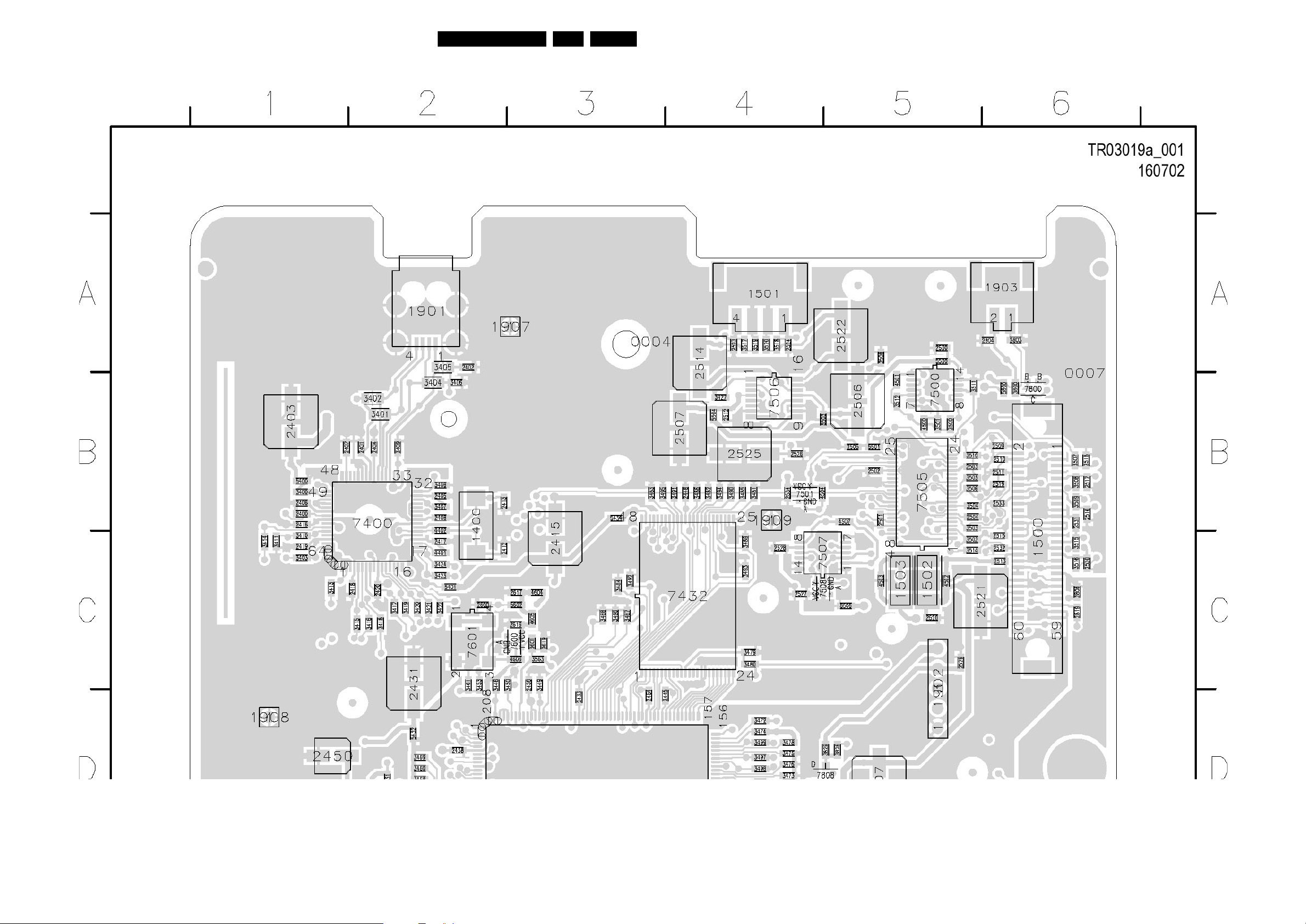

Layout DVIO 1.8 Board (Overview Top View)

EN 9DVIO 1.8 DV 2.

Circuit Diagrams and PWB Layouts

Layout DVIO 1.8 Board (Part 1 Top View)

EN 10DVIO 1.8 DV 2.

Circuit Diagrams and PWB Layouts

Layout DVIO 1.8 Board (Part 2 Top View)

EN 11DVIO 1.8 DV 2.

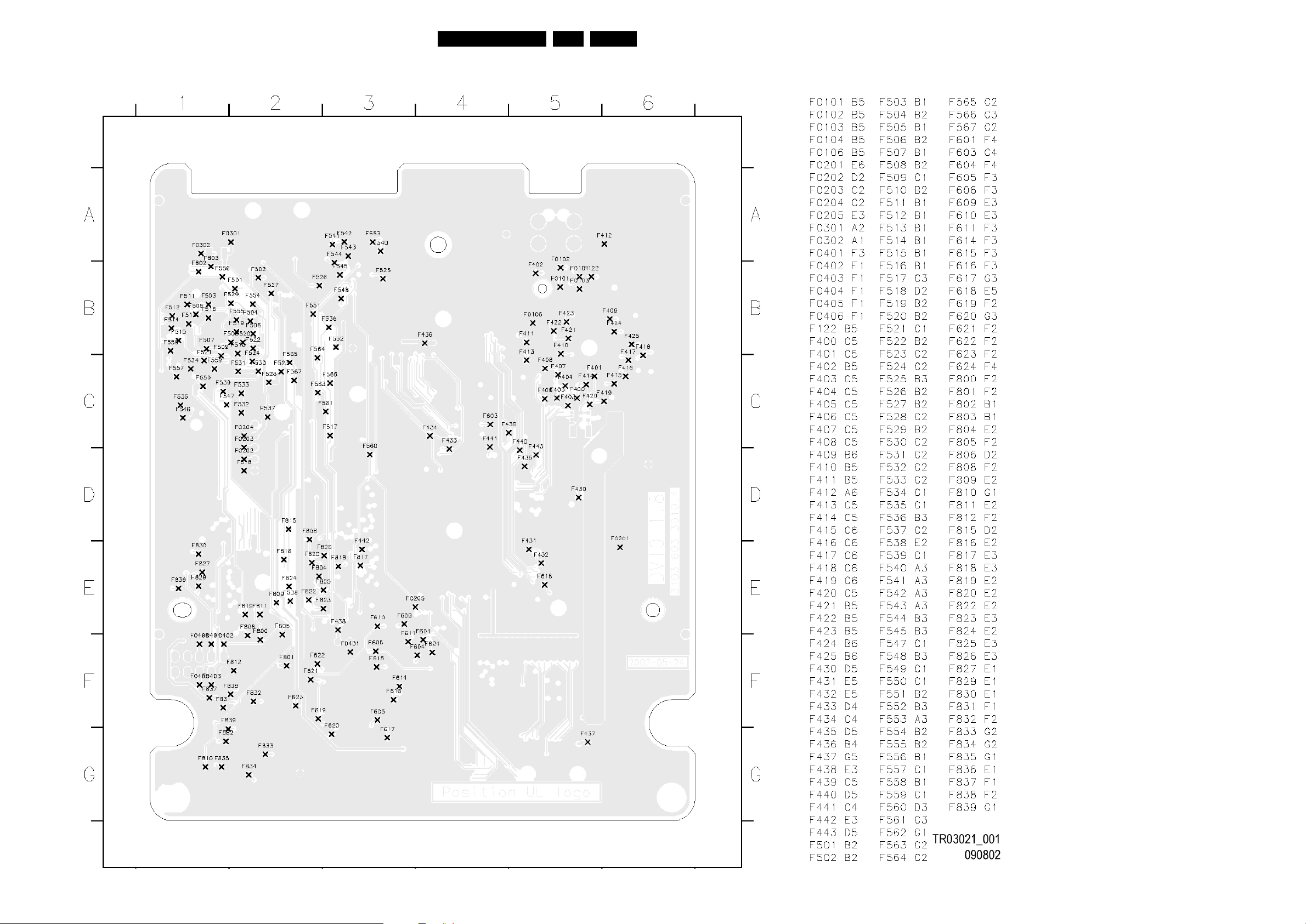

Circuit Diagrams and PWB Layouts

Layout DVIO 1.8 Board (Testlands Bottom View)

EN 12DVIO 1.8 DV 2.

3. Alignments

3.1 Adjustment DVIO 1.8 PC B

This adjustment sets the free running frequency of the VCO of

the audio PLL. It should be carried out after replacement of IC

7604.

1. Disconnect DVD+RW set from the mains.

2. Plug DVIO1.8 board via edge-connector onto Digital Board

(DVIO board is vertically oriented, so that both sides of the

PCB are accessible for measurements).

3. Connect DVD+RW set to the mains.

4. Turn DVD+RW set on and select any video input source

except the DV input.

5. Check the signal at test point F611 with an oscilloscope.

The signal should be 5V digital with 50% duty-cycle.

6. Measure the frequency of the signal at test point F610 and

adjust the potentiometer 3605 to get a frequency of

12.288MHz ±50kHz (after removing the screwdriver from

the potentiometer).

6a. In case the frequency can not be increased sufficiently,

replace capacitor 2618 by NP0-type capacitor with

18pF. Adjust afterwards again the frequency with the

potentiometer.

6b. In case the frequency can not be decreased

sufficiently, add (3pF-10pF) trim-capacitor in parallel to

capacitor 2618 or replace capacitor 2618 by NP0-type

capacitor with 27pF.Adjust afterwards again the

frequency with the potentiometer (and/or trimcapacitor).

7. Switch DVD+RW set to Stand-by mode.

8. Disconnect the DVD+RW set from the mains.

9. Plug DVIO1.8 board directly (without edge connector) onto

Digital Board.

10. Connect DVD+RW set to the mains.

11. Connect a DV-source that transmits DV-video data with

audio to the DVD+RW set.

12. Turn DVD+RW set on, select DV input, and switch

DVD+RW set appropriately to output the decoded signal.

Audio should be output without distortion.

Alignments

EN 13DVIO 1.8 DV 3.

EN 14 DVIO 1.8 DV4.

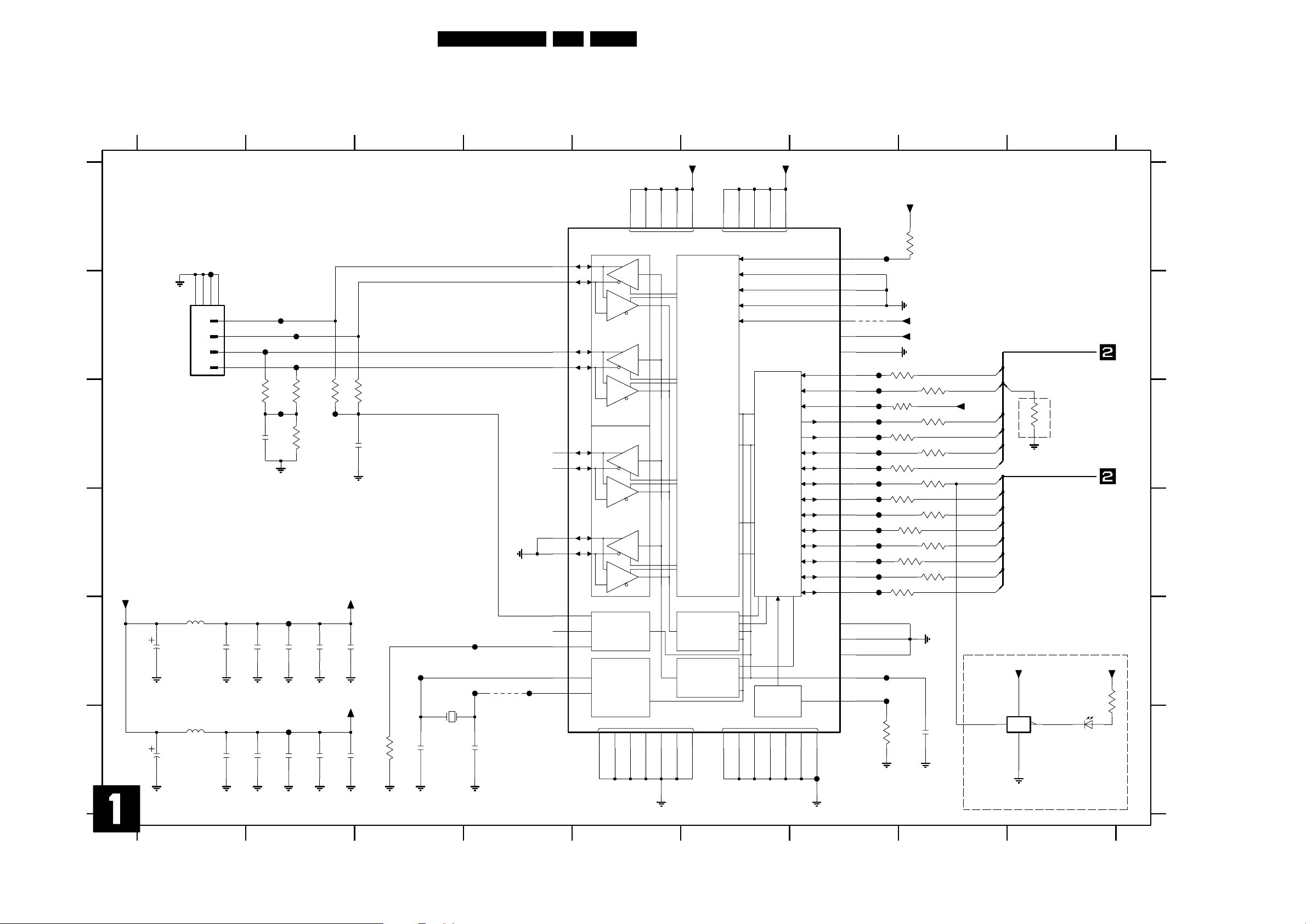

Circuit-, IC Descriptions and List of Abbreviations

4. Circuit-, IC Descriptions and List of Abbreviations

4.1 Divio 1.8 Board

4.1.1 Short Description of the Module:

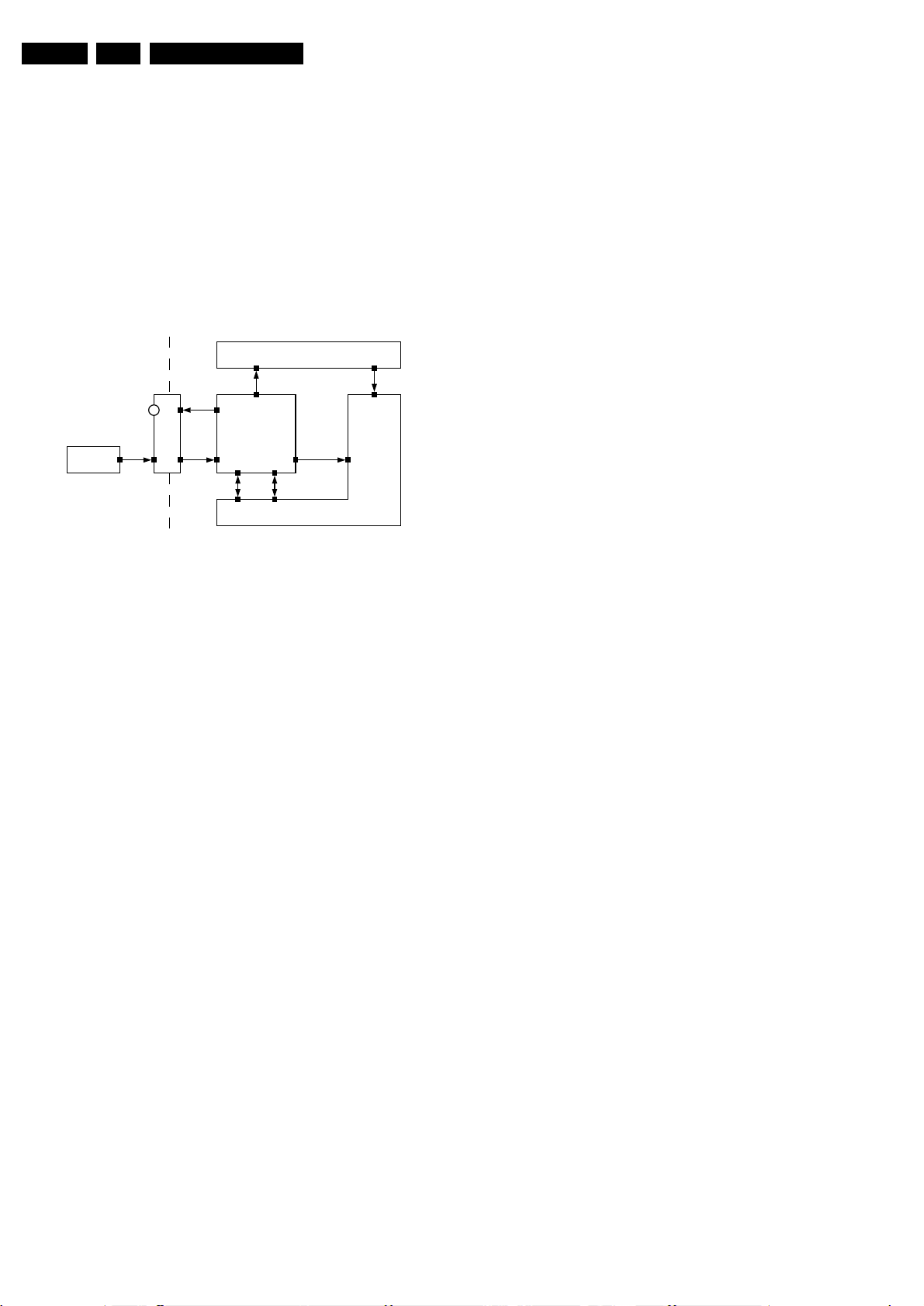

The DVIO Module is a decoder for DV streams. Input is a

stream from a DV-camcorder via IEEE1394. Outputs are

CCIR656 Video and Analog audio (L+R). A serial control

interface is present.

The following picture shows the location of the DVIO Module

inside the DVDR set.

Description DIVIO Module

ADC (analog PCB)

camcorder

LED

IEEE1394

Front DV PCB

Analog

audio L+R

On/Off

IEEE1394

Host decoder STi5505

DVIO Module

Digital video

Control RS232Control Misc.

(dig. PCB)

CCIR656

Digital

Audio I2S

Audio

Encoder

(dig. PCB)

Video

Encoder

(dig. PCB)

CL 16532095_118.eps

150801

Figure 4-1

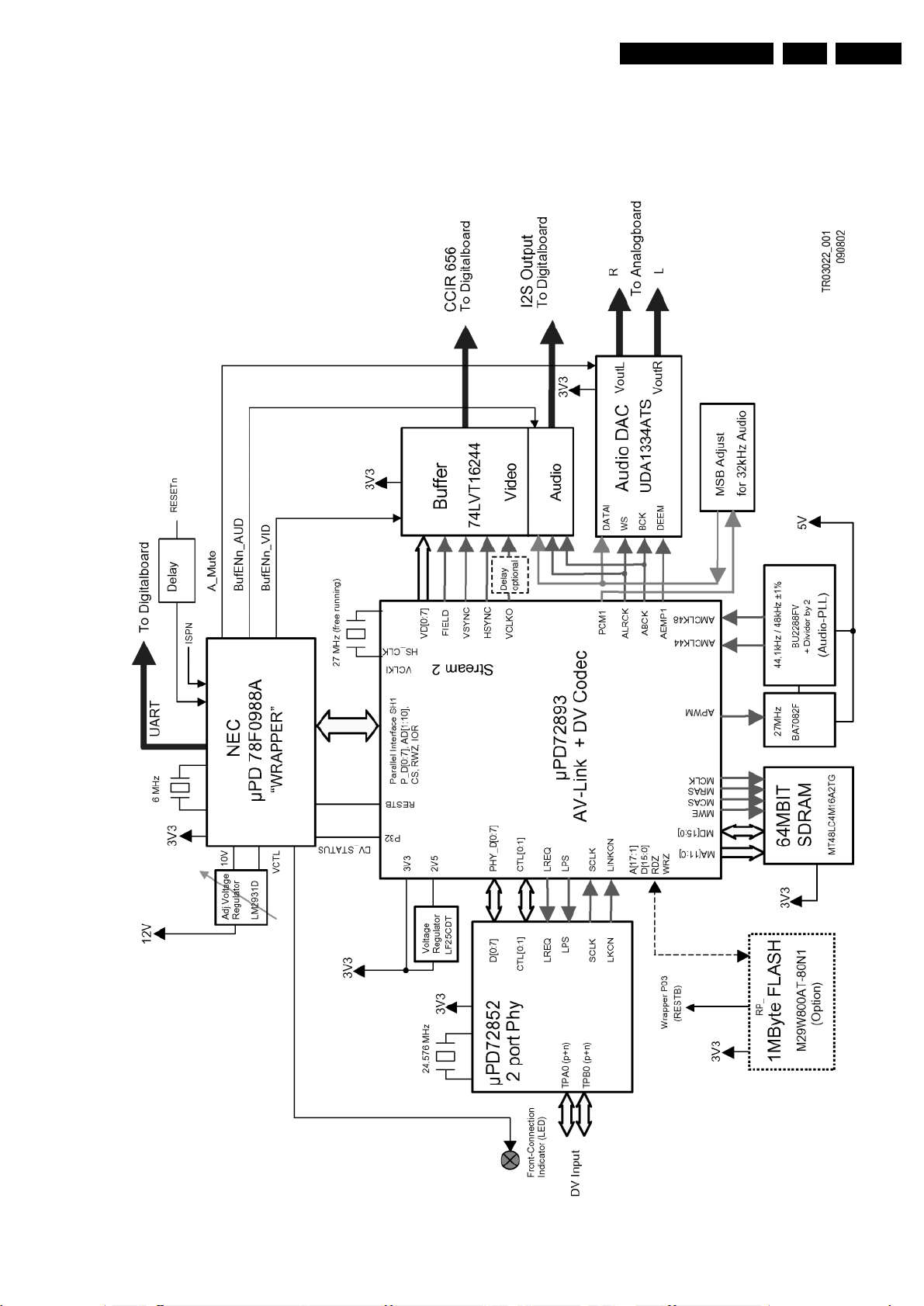

4.1.2 Block Diagram

Block Diagram DVIO1.8

Circuit-, IC Descriptions and List of Abbreviations

EN 15DVIO 1.8 DV 4.

Figure 4-2

Loading...

Loading...