Page 1

DVD-Video Recorder

DVDR3350H

#,!33

,!3%202/$5#4

Conteúdo Página

Especifi cações Técnicas 2

Localização dos Paineis 2

Instruções de Segurança 4

Instruções Mecânicas 6

Atualização da Memória ROM 9

Fluxos de Manutenção 12

Diagrama em Bloco 21

Diagrma de Conexões 23

Painel analógico- Formas de ondas 24

Painel analógico- Layout 26

Painel analógico- Vídeo frontal 28

Painel analógico- Entrada-Saída Vídeo 29

Painel analógico- Entrada-Saída Áudio 30

Painel analógico- Fonte de alimentação 31

Processamento de Multi áudio 32

Conversor de áudio 33

Painel analógico Digital- Entrada-Saída 34

Painel analógico Unidade de Controle 35

Painel analógico- Layout 36

Painel Frontal 38

Painel Frontal Entrada de áudio/vídeo 39

Layout 40

Pinel Frontal standby 41

Painel Digital- Processador Traseiro 42

Painel Digital- Memória 43

Painel Digital- Camada Fisíca 44

Painel Digital- Processador Entrada de Vídeo 45

Painel Digital- Interfaces 46

Layout 47

Circuito e descrição de IC 49

Vista Explodida 73

Impresso no Brasil Sujeito a Alterações Todos os Direitos Reservados 4806 727 17314

06/2006

Page 2

2 DVDR3350H

1. Especificação Técnica e Conexões

1.1 Localização dos Paineis

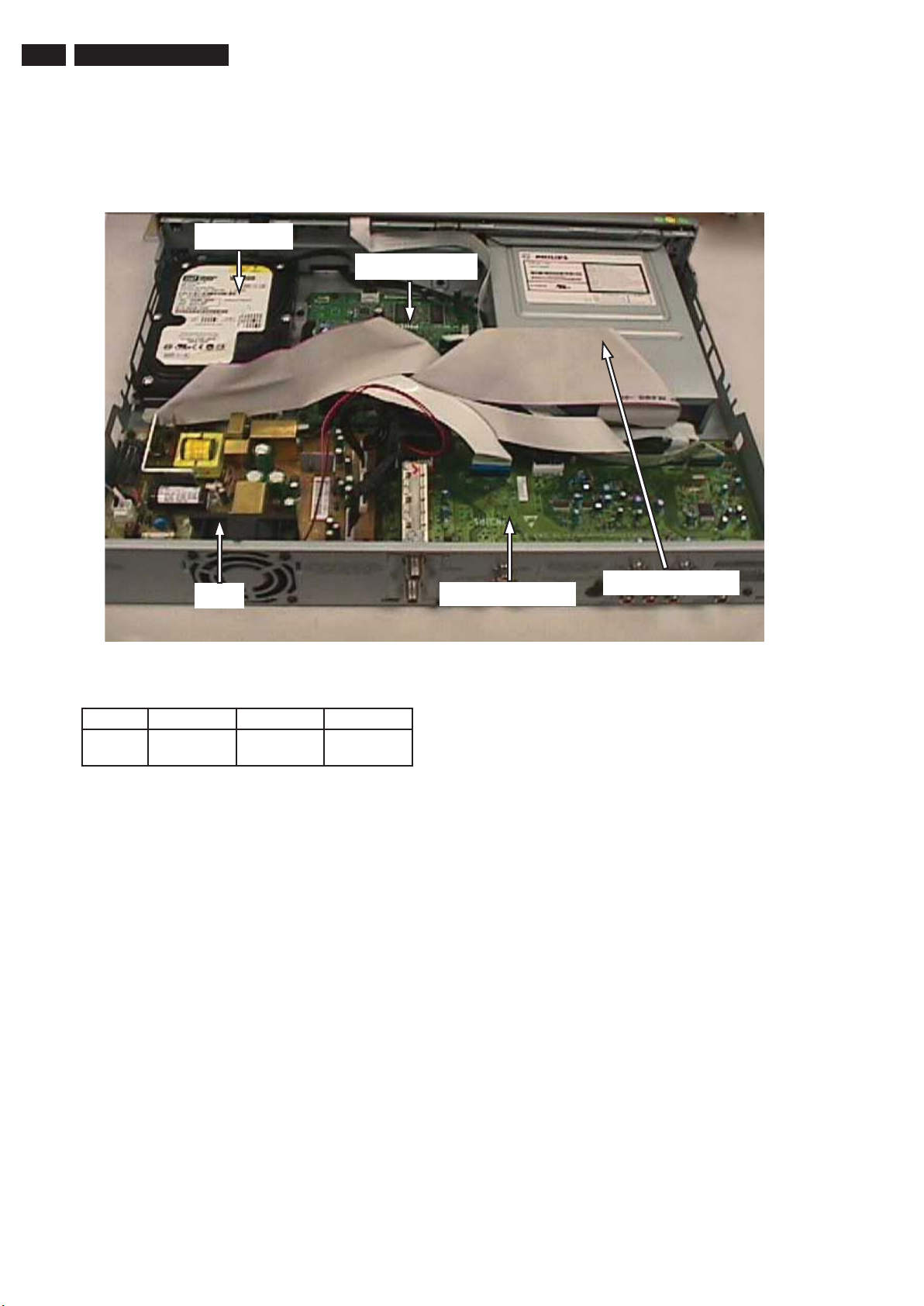

Disco-Rígido

Painel Digital

PSU

1.2 Diversidade da Matriz

DVDR3350H DVDR3360H DVDR3370H

HDD

Capacity

1.3 Geral:

Fonte de alimentação : 127V /37

: 110V - 240V /55

: 220V - 240V /75/97

Consumo : 25 W (típico)

Consumo em standby : < 3 W

1.4 RF Tuner

Teste equipmento: Fluke 54200 Gerador sinal de TV

Teste streams: Philips Standard teste padrão

1.4.1 Sistema

NTSC-M

1.4.2 RF - Loop Through:

80GB 160GB 250GB

Painel Analógico

1.4.4 Receiver:

PLL sintonizando com AFC para melhor recepção

Relação de frequência : 55 - 805 MHz

Sensibilidade em 40 dB S/N :

(video unweighted)

1.4.5 Desempenho de Vídeo:

Canal 25 / 503,25 MHz,

Teste padrão: teste padrão standard.

Nível RF 74dBμV

Medido na saída Cinch

Resposta de frequência : 0.1 - 3.58 MHz -1 ± 3dB

1.4.6 Desempenho de Áudio:

Desempenho Analógico de Áudio- HiFi:

Resposta de frequência em Cinch (L+R)

saída : 100 Hz - 10 kHz / 0 ±

3dB

S/N de acordo com DIN 45405, 7, 1967

e teste padrão standard PHILIPS

sinal de vídeo : ≥ 45dB

Distorção de harmônia (1 kHz, ± 25

kHz desvio) : ≤ 1.5%

Motor Básico

≤ 60dBμV em 75 Ω

Relação de frequência : 45 - 860 MHz

Ganho: (ANT IN - ANT OUT) : ≥ -6dB

Interferência de rádio / entrada max. de

tensão, em 75Ω

-40dB) : sem limite

1.4.3 Modulador:

Modulação de vídeo : 80%±15%

Resposta de frequência : 0 ± 3dB, 0...4.2MH

Modulação de áudio 1kHz tom : ± 12kHz, tol. ± 4kHz

, método de 3 tons (

≤

1.4.7 Sintonizando

Sintonizando Procura Automática

Explorando tempo sem antena : tip. 3 min.

Nível parado (visão carregado) : ≥ 37dBμV

Sintonia máxima -erro durante

operação : ± 100 kHz

Sintonia Manual

Seleção manual no modo “STORE”

Page 3

DVDR3350H

3

1.5 Entradas/Saídas Analógicas

1.5.1 Entrada Externa (Traseira)

Video - Y/C (Hosiden)

de acordo IEC 933-5

Sobreposição do nível DC no pino 4 - carga ≥ 100kΩ

< 2.4V é detectado como 4:3 taxa aspecto

> 3.5V é detectado como 16:9 taxa aspecto

Tensão entrada Y : 1 Vpp ± 3dB

Impedância de entrada Y : 75

Tensão de entrada C : burst 300 mVpp ± 3dB

Impedância de entrada C : 75 Ω

Video Cinch

Tensão de entrada : 1 Vpp ± 3dB

Impedância de entrada : 75

Audio Cinch

Tensão de entrada : 2.2 Vrms max.

Impedância de entrada : > 10k

1.5.2 Conectores de Entrada Frontal Áudio/Video

Audio

Tensão de entrada : 2 Vrms max.

Impedância de entrada : > 10k Ω

Video - Cinch

Tensão de entrada : 1 Vpp ± 3dB

Impedância de entrada : 75 Ω

Video - YC (Hosiden)

de acordo IEC 933-5

Sobreposição do nível DC no pino 4 (carga≥ 100 kΩ):

< 2.4V é detectado como 4:3 taxa aspecto

> 3.5V é detectado como 16:9 taxa aspecto

Tensão de entrada Y : 1 Vpp ± 3dB

Impedância de entrada Y : 75

Tensão de entrada C : burst 300 mVpp ± 3dB

Impedância de entrada C : 75 Ω

1.5.3 Saída 1

Component Video Cinch Y/Pb/Pr / Progressive Scan

de acordo EIO-770-1-A, EIA-770-2-A

Audio - Cinch

Tensão de saída : 2 Vrms max

Impedância de saída : < 2k Ω

1.5.4 Saída 2

Video - Y/C (Hosiden)

Tensão de saída Y : 1 Vpp ± 3dB

C : burst 300 mVpp ± 1dB

Impedância de saída Y, C : 75

Video - Cinch

Tensão de saída : 1 Vpp ± 1dB

Impedância de saída : 75 Ω

Ω

Ω

Ω

Ω

Ω

1.7 Desempenho de àudio DVD

1.7.1 Saída Traseira Cinch

Tensão de saída modo 2 canais : 2Vrms ± 1dB

Canal sem balanço (1kHz) : <1dB

Crosstalk 1kHz : >100dB

Crosstalk 20Hz-20kHz : >87dB

Resposta de frequência 20Hz-20kHz : ±0.2dB max

Taxa sinal/ruído (A-resistência) : >90dB

Relação dinâmica 1kHz : >83dB

Distorção e ruído 1kHz : >83dB

Distorção e ruído 20Hz-20kHz : >75dB

Distorção intermodução : >70dB

Mute : >95dB

Atenuação saída de faixa: : >40dB above 30kHz

1.8 Saída Digital

1.8.1 Coaxial

CDDA / LPCM : de acordo IEC60958

MPEG1, MPEG2, AC3 audio : de acordo IEC61937

DTS : de acordo IEC61937

correção 1

1.9 Entrada de Vídeo Digital (IEEE 1394)

1.9.1 Aplicações Standards

Acordo implementado:

IEEE Std 1394-1995

IEC 61883 - Parte 1

IEC 61883 - Parte 2 SD-DVCR (02-01-1997)

Especificação do consumidor usando VCR digital 6.3 mm

fita magnética - dec. 1994

Acordo de conexão mecânica:

Anexo A do 61883-1

1.10 Dimensões e Peso

Altura do pé : 5.5mm

Com a bandeja fechada : WxDxH :435x285x65mm

Com a bandeja aberta : WxDxH :435x422x65mm

Peso sem caixa : app. 4 kg ± 0.5 kg

Peso na caixa : app. 6.0 kg

1.11 Potência de saída do Laser & Comprimento da Onda

1.11.1 DVD

Saída durante leitura : 1.0mW

Saída durante escrita : 30mW

Comprimento da onda : 650nm

1.11.2 CD

Saída de potência : 1.0mW

Comprimento da Onda : 780nm

1.12 Velocidade de escrita

Audio - Cinch

Tensão de saída : 2 Vrms max

Impedância de saída : < 1k Ω

1.6 Desempenho de Vídeo DVD

Todas saídas carregadas com 75 Ohm

SNR- medição sobre largura da faixa total sem resistência.

1.6.1 Todas as Saídas

SNR : > 48dB

Largura da faixa : 4.2 MHz - 3dB

Tipo do disco (Função) Veloc. Rotação disco

ler velocidade do CD 7X CAV (25Hz)

ler velocidade do DVD 4X CAV (40Hz)

velocidade DVD+RW 2.4X ZCAV

velocidade DVD+R 2.4X ZCAV

Page 4

4 DVDR3350H

2. Informações de segurança, Notas Gerais & Exigência de Sem Clumbo

2.1 Instruções de Segurança

2.1.1 Segurança geral

Os regulamentos de segurança requerem que durante um reparo:

• Conecte a unidade aos cabos principais um transformador

de isolamento.

• Recoloque os componentes de segurança, indicados pelo sím-

bolo , somente pelos componentes idênticos aos originais.

Qualquer outra substituição de componente (com exceção

do tipo original) pode aumentar o risco de fogo ou choque

elétrico.

Os regulamentos de segurança requerem que depois de um

reparo, você deve retornar a unidade na sua condição original.

Preste atenção, particularmente, nos seguintes pontos:

• Distribua os fi os e cabos corretamente, e repare-os com os

acampamentos montados do cabo.

• Verifi que a isolação da condução dos fi os principais para danos

externos.

• Verifi que a resistência elétrica DC entre os fi os dos plugs princi-

pais e o lado secundário:

1. Desplugue os cabos principais, e conecte um fi o entre os

dois pinos do plugue principal.

2. Ajuste os fi os do interruptor principal na posição “ON”

(mantenha o cabo dos fi os principais plugados!)

3. Meça o valor da resistência entre os fi os dos plugues princi-

pais e do painel frontal, controle e botão de chassis.

4. O reparo ou a unidade correta quando a resistência está

sendo medida é de menos de 1 MΩ.

5. Verifi que isto, antes de retornar a unidade ao cliente / usuá-

rio (ref. UL- padrão no. 1492).

6. Mude a unidade para “OFF”, e remova o fi o entre os dois

pinos do plugue principal.

2.1.2 Segurança de laser

Essa unidade emprega um laser. Somente pessoal de serviço

qualifi cado pode remover a tampa, ou tente prestar serviços de

manutenção nesse dispositivo (devido a possível ferimento nos

olhos).

Unidade do dispositivo de Laser

Tipo: laser semi-condutor GaAlAs

Comprimento de onda: 650 nm (DVD)

Energia de saída: 20 mW (DVD+RW writing)

: 0.8 mW (leitura de DVD)

: 0.3 mW (leitura de VDC/CD)

Divergência do feixe: 60 graus

2.2 Cuidados

2.2.1 Geral

• Todos os ICs e muitos outros semicondutores são suscetí-

veis as descargas eletrostáticas (ESD, ") a manipulação

descuidada durante o reparo pode reduzir a vida drasticamente.

Certifi que-se que durante o reparo, você está no mesmo

potencial que a massa do aparelho por uma pulseira com resis tência. Mantenha os componentes e ferramentas na mesma

potência.

Equipamentos de proteção disponíveis ESD:

- Kit completo ESD3 (pequenas TABLEMAT, WRISTBAND, caixa

de conexão, cabo de extensão e fi o terra) 4822 310 10671.

- Verifi cador Wristband 4822 344 13999

• Tenha cuidado durante a medida da seção viva da tensão. O

lado primário da fonte de energia (pos. 105), incluindo o dissi pador de calor, carrega a tensão viva dos fi os principais quando

você conecta o aparelho nos fi os principais (mesmo quando o

aparelho está desligado!). É possível tocar nas trilhas e nos

componentes de cobre nesta área preliminar desprotegida,

quando você prestar serviços de manutenção no aparelho.

O pessoal de serviço deve tomar precauções para evitar tocar

esta área ou componentes desta área. Um “lightning stroke” e

uma listra marcada impressa no painel de fi ação, indica o lado

preliminar da fonte de alimentação.

• Nunca substitua módulos ou componentes enquanto a unidade

estiver ligada.

2.2.2 Laser

• O uso de instrumentos ópticos com este produto irá aumentar o

perigo de atingir o olho.

• Apenas o pessoal de serviço qualifi cado pode remover a tampa

ou tentar prestar serviço de manutenção a esse dispositivo,

devido a possível ferimento nos olhos.

• A manipulação do reparo deve ocorrer tanto quanto possível

com um disco carregado dentro do aparelho

• O texto abaixo é colocado dentro da unidade, no protetor de

tampa do laser:

CAUTION VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID EXPOSURE TO BEAM

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING VED ÅBNING UNDGÅ UDSÆTTELSE FOR STRÅLING

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING NÅR DEKSEL ÅPNES UNNGÅ EKSPONERING FOR STRÅLEN

VARNING SYNLIG OCH OSYNLIG LASERSTRÅLNING NÄR DENNA DEL ÄR ÖPPNAD BETRAKTA EJ STRÅLEN

VARO ! AVATTAESSA OLET ALTTIINA NÄKYVÄLLE JA NÄKYMÄTTÖMÄLLE LASER SÄTEILYLLE. ÄLÄ KATSO SÄTEESEEN

VORSICHT SICHTBARE UND UNSICHTBARE LASERSTRAHLUNG WENN ABDECKUNG GEÖFFNET NICHT DEM STRAHL AUSSETSEN

DANGER VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID DIRECT EXPOSURE TO BEAM

ATTENTION RAYONNEMENT LASER VISIBLE ET INVISIBLE EN CAS D’OUVERTURE EXPOSITION DANGEREUSE AU FAISCEAU

Figura 2-2

2.2.3 Notas

Dolby

CLASS 1

LASER PRODUCT

Manufaturado sob licença do Dolby Laboratories. "Dolby", "Pro

Logic" e o símbolo duplo-D são marcas resgistradas do Laborató

rio Dolby.

© 1992-1997 Laboratório Dolby, Inc. Todos os direitos reservados.

Figura 2-1

Nota: o uso dos controles ou do ajuste ou o desempenho do pro-

cedimento à excepção daqueles especifi cado nisto, podem resul-

tar na exposição perigosa da radiação. Evite a exposição direta ao

feixe.

Figura 2-3

Trusurround

TRUSURROUND, SRS e o símbolo (fi g. 2-4) são marcas registra

das do Laboratório SRS, Inc. A tecnologia TRUSURROUND é

manufaturada sob licençã do laboratório SRS, Inc.

Figura 2-4

Page 5

DVDR3350H

5

Vídeo Plus

"Video Plus+" e "Plus Code" são marcas registradas do Gemstar

Development Corporation. O sistema "Video Plus+" é fabricado

sob a licença da Gemstar Development Corporation.

Figura 2-5

Microvision

Este produto incorpora tecnológia de proteção de cópia que é

o metódo de proteção exigido da certifi cado U.S de patentes e

outros proprietários intelectuais da própria Macrovision Corporation.

O uso desta tecnológia de proteção de cópia deve ser autorizada

pela Macrovision Corporation e é permitido para casa e outros

limites somente com autorização da Macrovision Corporation. A

desmontagem é proíbida.

2.3 Solda sem chumbo

A Philips CE está produzindo aparelhos sem chumbo (PBF) de

1.1.2005 para frente.

Identifi cação: A linha principal de um tipo de prato dá um número

de série de 14 dígitos. Os dígitos 5 e 6 referem-se ao ano de

produção, os dígitos 7 e 8 referem-se à semana de produção (no

exemplo abaixo, é 1991 na semana 18).

companhias externas.

• Informações especiais para ICs BGA sem chumbo: estes ICs

serão entregues no chamado “pacote a seco” para proteger o IC

contra umidade. Este pacote só pode ser aberto pouco antes de

ser usado (soldado). Ou então o corpo do IC fi ca “molhado” dentro

e durante o tempo de aquecimento a estrutura do IC será destruída por causa da alta temperatura dentro do corpo. Se o pacote for

aberto antes do uso,, o IC deve ser esquentado por algumas horas

(em torno de 90

o

) Para secar (pense na proteção ESD!). NÃO RE-

USE BGAs de modo algum!

• Para produtos produzidos ante de 1.1.2005, contendo ferramenta

de solda com chumbo e componentes, toda a lista de peças será

avaliada até o fi m do período de serviço. Para reparo destes

aparelhos, nada muda.

• No website www. atyourservice.ce.Philips.com você encontra mais

informações sobe:

• (De) Solda BGA (+ instruções de operação bancária).

• Perfi s de aquecimento dos BGAs e outros ICs usados em apare-

lhos Philips.

Você encontra estas e mais informações técnicas em “magazine”,

capítulo “workshop news”.

Para questões adicionais, por favor, contate o help desk local.

3. Instrução de Uso

Veja o Manual no GIP.

Apesar do logo especial sem chumbo (que nem sempre é indi-

cado), ONE MUST TREAT todos os aparelhos de sua data pra

frente de acordo com as regras descritas abaixo.

Com a tecnologia sem chumbo, algumas regras devem ser respei-

tadas pelo workshop durante o reparo:

• Use apenas ferramentas de solda sem chumbo Philips SAC305

com o código de pedido 0622 149 00106. Se a pasta de solda sem

chumbo é necessária, por favor contate o fabricante do equipamento de solda. No geral, o uso de pasta de solda em workshops

deve ser evitada pois a pasta não é facilmente manuseada nem

armazenada.

• Use apenas ferramentas de solda aplicáveis para ferramenta de

solda sem chumbo. A ferramenta de solda deve:

- Alcançar na ponta da ferramenta a temperatura de pelo menos

o

400

- Estabilizar o ajuste de temperatura na ponta da solda.

- Troque a ponta de solda para diferentes aplicações.

• Ajuste sua ferramenta de solda para que a temperatura de 360o

o

- 380

seja alcançada e estabilizada na junção da solda. O tempo

de aquecimento da junção da solda não deve exceder ~ 4s. Evite

temperaturas acima de 400

o

, ou então "wear-out" das pontas

irá aumentar drasticamente e o fl uxo- fl uido será destruído. Para

evitar "wear-out" de pontas, desligue o equipamento não usado

ou reduza a temperatura.

• Misturar parte/ ferramenta de solda sem chumbo com partes/

ferramentas de solda com chumbo é possível mas a PHILIPS

recomenda que se evite isso. Se não puder ser evitado, cuidadosamente limpe a solda da antiga ferramenta e re-solde com uma

nova ferramenta.

• Use apenas peças originais listadas no Manual de Serviço. Materiais padrão não listados (comodities) devem ser comprados em

Page 6

6 DVDR3350H

4. Instruções Mecânicas

4.1 Desmontando um conjunto do componente.

Para números do artigo, por favor veja vista explodida no Capítulo 9.

4.1.1 Desmontando a tampa da bandeja do carregador.

1) Insira uma chave de fenda e empurre a alavanca na direção

mostrada na Figura 4-1 para destravar a bandeja antes de deslizála para fora.

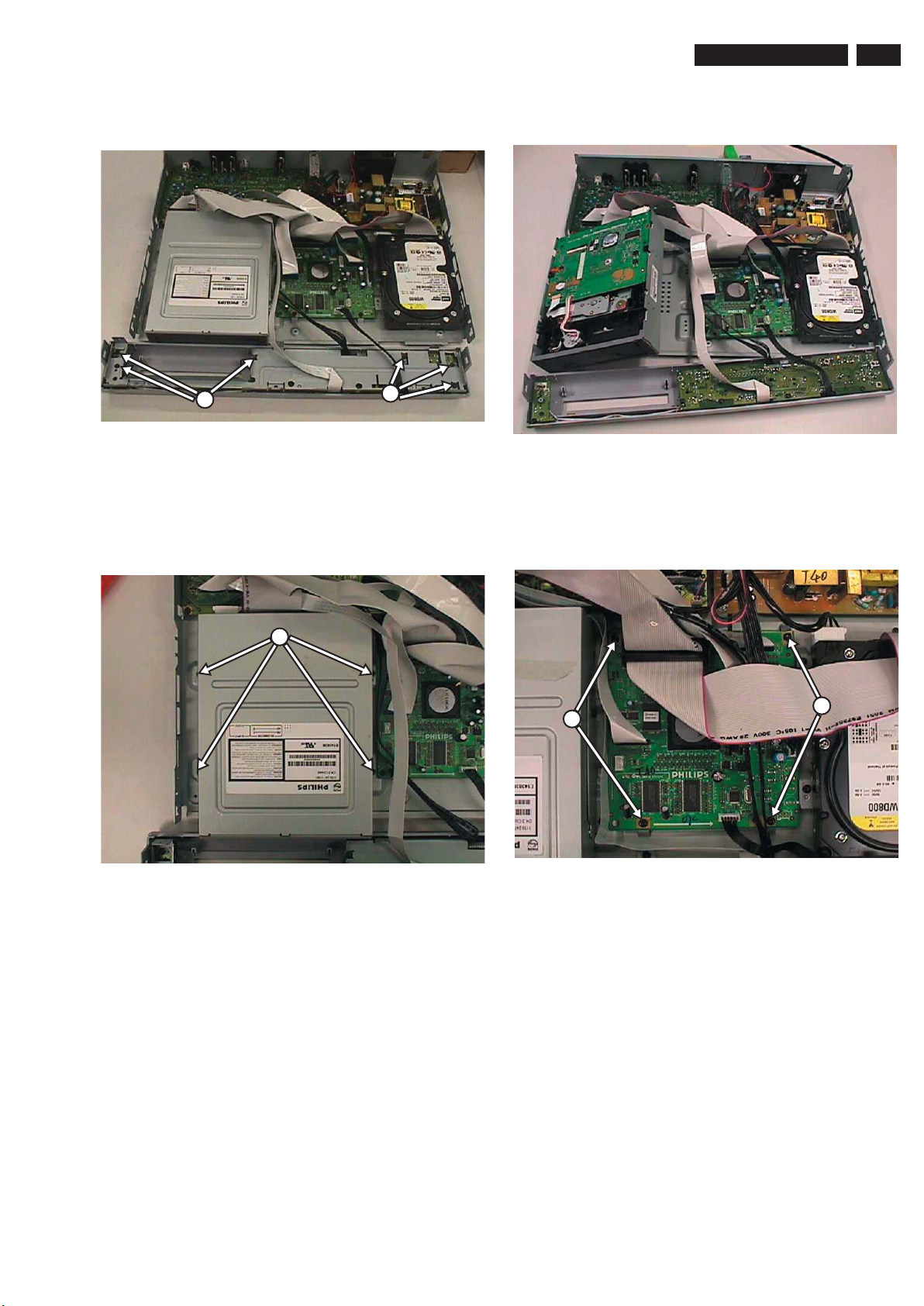

4.1.2 Desmontando o Hard-Disk e Conjunto do Painél Frontal

1) Remova os 4 parafusos do drive do Hard-Disk

1

1

Figura 4-3

2) Remova os 3 parafusos e solte os 2 ganchos de pressão ao

lado antes de remover o conjunto frontal.

Figura 4-1

2) Remova a tampa da bandeja como mostrado na fi gura 4-2

Figura 4-2

2

2

Figura 4-4

2

Page 7

DVDR3350H

7

3) Remova os 6 parafusos para remover o painel frontal 184 como

mostra a Figura 4-5.

3

Figura 4-5

4.1.3 Desmontando o Motor Básico

1) Remova a bandeja da tampa.

2) Remova os 4 parafusos para libertar o motor básico.

3

3) Coloque o motor básico na posição de serviço girando o motor

básico na posição vertical.

Figura 4-7

4.1.4 Desmontando o painel Digital

1) Remova os 4 parafusos para afrouxar o painel digital como

mostrado na fi gura 4-8.

Figura 4-6

4

5

5

Figura 4-8

Page 8

8 DVDR3350H

2) Você poderá colocar na posição de serviço girando o painel

digital para a posição vertical como na fi gura 4-9.

Figura 4-9

Nota: O cabo (apenas para transferir a conexão de serviço para

o painel MOBO) de socket 1101 pode ser removido e utilizado

para conexão hyper terminal.

4.1.5 Desmontando o painel analógico

3) Você poderá colocar na posição de serviço girando o painel

analógico para a posição vertical como na fi gura 4-10.

Figura 4-12

1) Remova os 5 parafusos 246 e os 4 parafusos 254 e parafuso

230.

6

7

Figura 4-10

2) Remova 4 parafusos 270 e libere os 2 prendedores no painel.

8

Figura 4-11

9

Page 9

5. Atualização da Memória ROM e Formatação do HDD

DVDR3350H

9

Informações importantes

• Cada um dos 3 procedimentos de upgrade deve ser gravado

em 3 discos separadamente.

• A Memória ROM FLASH e Memória ROM HDD devem ser

compatíveis (i.e. Mesma versão no.)

• O upgrade da memória ROM FLASH deve ser feita antes do

upgrade da memória ROM HDD.

5.1 Upgrade da Memória ROM

A. Preparação para upgrade da memória ROM:

1. Unzip o arquivo zip.

2. Inicie o programa de Gravação de CD e crie um novo projeto de

CD (disco de dados) com os seguintes ajustes:

File System: Joliet

Format:: MODE1: CDROM

Recording mode: SINGLE SESSION (TRACK-AT-ONCE),

FINALIZED CD

Nota: Arquivo com nome longo é necessário para a preparação do

upgrade disc.

3. Coloque o conteúdo do arquivo zip na raíz do diretório do novo

projeto CD.

4. Grave os dados em um CDR ou CD-RW virgem.

B. Procedimento para aplicar o upgrade da memória ROM

FLASH:

Nota: Não pressione nenhum botão ou interrompa a energia

elétrica durante o processo de upgrade, desta forma o aparelho

apresentará defeito.

6. Quando o processo de upgrade for concluído a bandeja abrirá e

a TV conectada ao aparelho mostrará:

System is succesfuly upgraded.

Remove disc from tray & reset system

7. Remova o disco de Upgrade e pressione o botão <OK> para

confi rmar.

8. A tela da TV não mostrará nada, a bandeja fechará e em segun

dos o Logotipo da Philips aparecerá novamente.

C. Procedimento para aplicar o upgrade da memória ROM

HDD:

1. Ligue o aparelho e abra a bandeja.

2. Insira o CDROM de upgrade preparado e feche a bandeja.

3. A TV conectada ao aparelho mostrará:

Software Upgrade Disc detected

Select OK to start or CANCEL to exit

4. Pressione o botão <OK> para confi rmar o upgrade (use o botão

esquerda/direita para selecionar)

5. A TV conectada ao aparelho mostrará:

Upgrading software, Please wait

Do not switch off the power

1. Ligue o aparelho e abra a bandeja.

2. Insira o CDROM de upgrade preparado e feche a bandeja.

3. A TV conectada ao aparelho mostrará:

Software Upgrade Disc detected

Select OK to start or CANCEL to exit

4. Pressione o botão <OK> para confi rmar o upgrade (use o botão

esquerda/direita para selecionar)

5. A TV conectada ao aparelho mostrará:

Upgrading software, Please wait

Do not switch off the power

O processo inteiro leva menos de 5 minutos.

O processo inteiro leva menos de 5 minutos.

Nota: Não pressione nenhum botão ou interrompa a energia elé trica durante o processo de upgrade, desta forma o aparelho apre sentará defeito.

6. Quando o processo de upgrade for concluído a bandeja abrirá e

a TV conectada ao aparelho mostrará:

System is succesfuly upgraded.

Remove disc from tray & reset system

Page 10

10 DVDR3350H

7. Remova o disco de Upgrade e pressione o botão <OK> para

confi rmar.

8. A tela da TV não mostrará nada, a bandeja fechará e em segundos o Logotipo da Philips aparecerá novamente.

9. Pressione <Tuner> e <Setup>.

10. No “SETUP MENU - HDD”, selecione “Delete HDD” e pressione <OK>

11. A TV conectada ao aparelho mostrará:

All video programs on the HDD will be deleted

Press OK to continue.

12. Pressione o botão <OK> para confi rmar o delete. (Use o botão

esquerda/direita para selecionar)

O processo inteiro leva menos de 5 minutos.

Nota: Não pressione nenhum botão ou interrompa a energia elé-

trica durante o processo de upgrade, desta forma o aparelho apre-

sentará defeito.

13. Quando o processo de upgrade completar, o aparelho entrará

em modo Standby.

Nota: Todos os canais programados serão perdidos.

D. Procedimento para aplicar o upgrade de memória ROM

SERVO:

1. Ligue o aparelho e abra a bandeja.

2. Insira o CDROM de upgrade preparado e feche a bandeja.

3. A TV conectada ao aparelho mostrará:

Software Upgrade Disc detected

Select OK to start or CANCEL to exit

6. Quando o processo de upgrade for concluído a bandeja abrirá e

a TV conectada ao aparelho mostrará:

Loaded upgrade process has completed succesfully.

Press OK to reboot the system.

7. Remova o disco de Upgrade e pressione o botão <OK> para

confi rmar.

8. A tela da TV não mostrará nada, a bandeja fechará e em segundos o Logotipo da Philips aparecerá novamente.

E. Como verifi car a versão da memória ROM para confi rmar o

upgrade.

1. Ligue o aparelho e pressione <Setup>.

2. Pressione os botões <321> e <Select> no controle remoto.

3. Pressione <OK> para sair.

5.2 Procedimento para substituir um novo HDD:

1. Substitua o HDD defeituoso por um novo HDD.

2. Ligue o aparelho e abra a bandeja.

3. Insira o disco de upgrade da memória HDD e siga “Procedimento para aplicar o upgrade da memória ROM HDD” (Veja 5.1 C).

O processo inteiro leva menos de 5 minutos.

Nota: Não pressione nenhum botão ou interrompa a energia elé trica durante o processo de upgrade, desta forma o aparelho apre sentará defeito.

4. Quando o processo de upgrade do HDD for concluído, o aparelho entrará no modo Standby.

5. Para atualizar o aparelho, siga “Upgrade da Memória ROM”

(Veja 5.1)

4. Pressione o botão <OK> para confi rmar o upgrade (use o botão

esquerda/direita para selecionar)

5. A TV conectada ao aparelho mostrará:

Upgrading software, Please wait

Do not switch off the power

O processo inteiro leva menos de 5 minutos.

Nota: Não pressione nenhum botão ou interrompa a energia elé-

trica durante o processo de upgrade, desta forma o aparelho apre-

sentará defeito.

Page 11

NOTAS:

1. Para referência aos níveis de votagem, Não representa medidas

de votagem que estão fora da escala de +- 10% dos valores específi cados.

2. Para referência de soldagem e substituição de componentes, OK

signifi ca que o aparelho não apresenta problemas e está funcio-

nando corretamente. Não - signifi ca que o problema continua a

existir.

3. Para referência de pulsos contínuos, OK - é a forma do sinal asse-

melhando-se a um quadrado, com ponto a ponto o nível de tensão

de 3.3V + - 10%

Não - signifi ca que a medição está fora da especifi cação OK indi-

cada acima

4. Para referências de ondas do seno,

OK - é a forma do sinal assemelhando-se a uma onda do seno,

com ponto a ponto o nível de tensão de 5.6V + - 10% (note que

este nível de tensão é obtida utilizando-se um teste de sinal de

0dB).

Não - signifi ca que a medição está fora da especifi cação OK indi-

cada acima.

5. Para referências de formas de ondas de vídeo,

OK - É a medição de forma de onda assemelhando-se as (forma e

tensão nível + - 10%) suas respectivas formas de ondas dentro da

seção FORMA DE ONDA.

Não - Se a forma de onda não combina (forma e tensão nível +

- 10%) às formas de onda na seção de FORMA DE ONDA ou se

não há nenhuma forma de onda.

DVDR3350H

11

Lembrete: Para pontos 3 - 5, por favor consulte a seção de

FORMA DE ONDA como guia.

Page 12

12 DVDR3350H

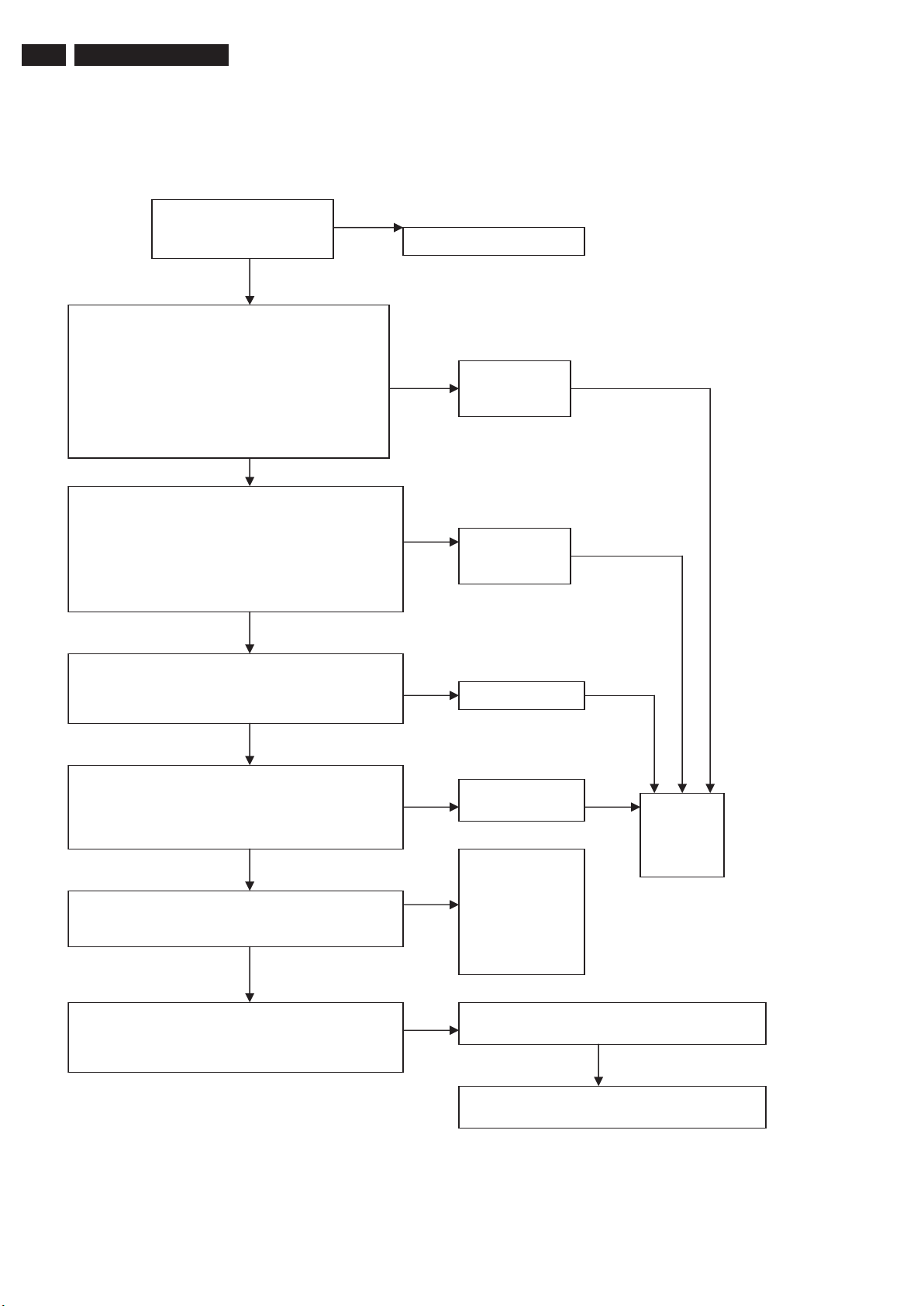

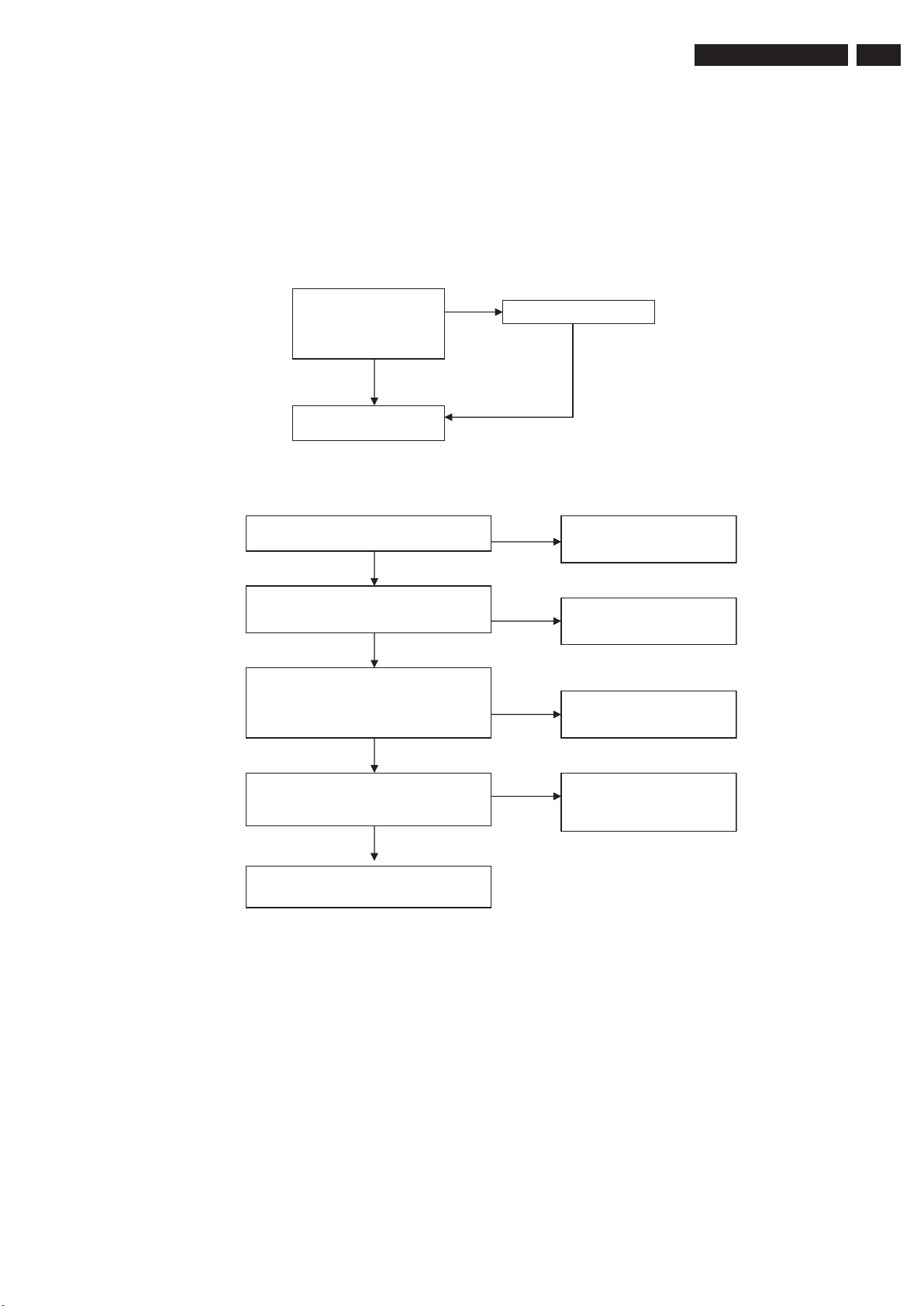

5.3 Fluxo de Manutenção

5.3.1 Aparelho completamente apagado

Cheque todas as conexões

dos cabos- observe

se existe cabos soltos

Não observa problemas

e conexão

Cheque tensão no Painel Digital conector 1501

Pino 1=3.30v

Pino 2 =3.30v

Pino 3 =3.30v

Pino 4 =3.30v

Pino 6 =12.00v

Pino 9 =5.00v

Pino 12 =-5.00v

OK

Cheque tensão no Painel Analógico conector 1400

Pino 1 = 12.00v

Pino 3 = 5.00 v

Pino 5 = 3.30v

Pino 7 = -5.00v

Pino 9 = 32.00v

Pino 11 = -26.00v

Observe problemas com

conexões

Fixe cabos desconectados

Não Não

Substitua Painel

Digital

Não

Substitua

Painel Analógico

Não

OK

Cheque tensão no PSU conector J5

Pino 1 = 12.00v

Pino 4 = 5.00v

OK

Cheque tensão no Painel Analógico conector 1803

Pino 10 = 5.00v

Pino 13 = -26.00v

Pino 14 = 12.00v

OK

Cheque tensão no PSU conector J6

Pino 1 = 12.00v

Pino 4 = 5 00v

OK

Retoque a solda em SDRAM (item 7211 & 7231 no

Painel Digital)

Não

Não

Não

Não

Não

Substitua Drive

Substitua Painel

Frontal

Substitua

Unidade de

Alimenta-

Substitua Disco

ção

Rígido(A pós a

troca do Disco

Rígido, reinstale o

Software do

Disco Rígido)

Substitua SDRAM (item 7211 & 7231 no

Painel Digital)

Não

Substitua Disco Rígido

(Após trocá-lo reinstale

o software)

Page 13

5.3.2 O Disco Não Pode Ser Lido

Cheque a alimentação do cabo do PSU

conector J5 para Drive conector pino 4. As

conexões podem estar soltas.

Cheque o cabo conector do Painel Digital

conexão 1571 para Drive conector pino 40.

As conexões podem estar soltas

Problemas visíveis com

conexões

Problemas não visíveis com

conexões

Problemas visíveis com

conexões

Problemas não visíveis com

conexões

Fixe o cabo conector

Fixe o cabo conector

DVDR3350H

13

Substitua cabo de Alimentação do PSU do Drive

5.3.3 Disco Desconhecido

Cheque tensão no PSU conector D

Pino 1 = 12.00v

Pino 4 = 5 00v

OK

Não

Substitua Carregador

Cheque conexão do cabo:

Cabo Alimentação do PSU conexão D

do Drive conector pino 4

Não

Troque PSU

OK

Substitua cabo de Alimentação do PSU do Drive

OK

Substitua Carregador

Page 14

14 DVDR3350H

5.3.4 Áudio sem Som (Reprodução)

NOTA1: Para começar eliminar erros desta seção, reproduza no modo “repeat” uma onda sine 1kHz

0dB de um CD de teste.

NOTA2: Todas as referências são do Painel Analógico a menos que sejam especificadas de outra forma.

Problemas visíveis com

Cheque os cabos na conexão 1600 e 1400

no painel Analógico. As conexões podem

estar soltas.

Problemas não visíveis com

conexões

Cheque tensão na conexão

1400 (Painel Analógico)

Pino 1 = 12.00v

Pino 3 = 5.00 v

Pino 5 = 3.30v

Pino 7 = -5.00v

Pino 9 = 32.00v

Pino 11 = -26.00v

OK

conexões

Fixe os cabos conectores

Substitua Painel

Analógico

Não

Cheque Ponto de teste

I613 = 11.2V –12V

I624 = 3.3V

I615 = alto

OK

Cheque Pontos de teste

no Painel Analógico

I603, I604, I605, I609 =

pulso “square”

OK

Monitor Ponto de teste

I618 & I620 = 1KHz

2Vrms Onda Sine

OK

Monitor Ponto de Teste

I616 & I617 = 3.3V

OK

Monitor Ponto de teste

I600 = -5V (alto)

OK

Monitor Ponto de teste

F603 = <0.6V (baixo)

Substitua Painel

Analógico

Não

Substitua Painel

Digital

Não

Troque Audio

DAC, item 7603

no Painel Analógico

Troque Audio

DAC, item 7603

no Painel Analógico

Troque transistor

item 7600

Troque Painel

Digital

OK

Monitor Ponto de Teste

I601 = 5V (alto)

OK

Monitor Ponto de teste

F408 = 5V (alto)

Troque transistor

item 7602

Troque PSU

Page 15

DVDR3350H

5.3.5 Áudio sem Som (TV & Fonte Externa)

NOTA1: Para começar eliminar erros desta seção, reproduza uma onda “sine” 0dB 1kHz de um

disco de teste na fonte externa que manifesta o problema.

15

NOTA2:

Parte 1

Todas as referências são do Painel Analógico a menos que sejam especificadas de outra forma.

Problemas visíveis com

conexões

Cheque conexões nos

conectores 1600 e 1204.

As conexões podem

estar soltas

Problemas não visíveis com

conexões

Acesse Parte 1 e então a

Parte 2

Cheque tensão da alimentação

I614 = 3.3V

OK

Cheque Ponto de Teste

SYSCLK I608 = pulso “square” 12.28MHz

F609, F610, F611 = Pulso “square ”

OK

Cheque linha de controle

I612 = 0V (baixo)

I611 = 1.7 V

I610 = 1.6V

Fixe os cabos conectores

Não

Não

Não

Não

Troque ADC

Substitua Painel Digital

Troque ADC

OK

Cheque I316 & I319 = onda “sine”

&

Check I606 & I607= onda “sine”

OK

Replace Analog Board

Não

Substitua o componente

entre estes 2 pontos de teste

(Op Amp 7300)

Page 16

16 DVDR3350H

Parte 2

Cheque I310 & I311

Compare com a Tabela Verdade abaixo

OK

IF MDX 7301 pino 3 & 13 = nenhuma onda “sine”

Verifique entrada em MDX 7301

I300, I301, I312, I313

I314, I315, I303, I305

Não

Cheque MSP (7500) Xtal em I509 =

18.432MHz

Cheque tensão da Alimentação em

F420 = 8V

I508 = 5V

I515 = 5V

OK

I503 = 4.5MHz 300~500mVpp Onda Sine

OK

Troque Painel Analógico

Tabela Verdade

Pino9 Pino10 Fonte

0 0 áudio tuner RF

0 1 entrada de Áudio Frontal

1 0 Entrada de áudio traseiro

1 1 Entrada de áudio traseiro

OK

Retoque a solda

OU

Substitua IC MSP (7500)

2 (condição)

Page 17

5.3.6 Nenhuma Saída de Vídeo Aparelho Ligado (Aparelho não morto)

NOTA: Para certificar-se que o aparelho não está morto, você pode fazer o seguinte.

1. Veja no Display Frontal a palavra “Ch001” depois de carregado.

2. Eject a baneja e feche-a.

NOTA2: Para eliminar erros desta seção, reproduza um título da Barra de Cor de 75%

DVDR3350H

17

Cheque Painel Digital formas de onda nos pontos de teste

CVBS T524

Y T522

C T523

GY T520

BPb T518

RPr T521

OK

Cheque Painel Analógico forma de onda nos pontos de teste

CVBS F235

C F236

Y F237

D-VR F238

D_YG F239

D_UB F240

OK

Cheque Painel Analógico forma de onda nos pontos de teste

D_YG F213

D_UB F214

D_VR F215

Y F219

C F220

CVBS F222

Não

Não

Não

Substitua Painel Digital

Substitua cabo FFC no

conector 1205 (painel

analógico)

Substitua transistores correspondentes

(7200, 7201, 7202,

7203, 7204, 7205)

Page 18

18 DVDR3350H

5.3.7 Nenhuma Entrada de Vídeo

NOTA1: Todas as referências são do Painel Analógico a menos que sejam especificadas de outra forma.

NOTA2: Para problema com Entrada de Vídeo Traseira, refere-se a Seção 1.Para problemas com

Entrada de Vídeo Frontal, acesse Seção 2.

Seção 2Seção1

Cheque cabo FFC no

conector 1521 . A cone-

xão pode estar solta

Cheque as rachaduras no

Painel Analógico (próximo

ao conector 1207 cinch)

Acesse D

D

Conexão solta

não visível

Rachaduras não visíveis

no Painel

Visível conexão

solta

Fixe o

conector

Rachaduras visíveis no

Painel

Substitua Painel

Analógico

Não

Cheque Relógio em

T461 & T462 = 14.318MHz

Cheque cabo FFC no

conector 1204 Painel

Analógico. A conexão pode

estar solta.

Conexão solta

não visível

Troque Painel Frontal

Não

Acesse

D

Não

Visível conexão

solta

Fixe o

conector

Substitua Cristal 1461

Cheque respectivo i/p

ponto de teste

do vídeo no painel

analógico

Não

Substitua Painel

Abalógico

Não

OK

OK

Cheque Entrada de Vídeo para forma de onda

T525, T526, T527, T528, T529, T530, T531,

T532 T533 T535

OK

Substitua VIP (7401) IC

Não

Substitua Painel Digital

Page 19

5.3.8 Tuner Não Funciona

NOTA: Todas as referências são do Painel Analógico

DVDR3350H

19

Chequeas rachadurano no Painel e as aréas

próximas do Tuner

OK

Cheque Tensão nos Pontos de Teste

I119 = 33V

F101 = 5V

OK

Cheque I100 & I102 no I2C

OK

Direcione acesso tuner para algum canal.

Se existe vídeo e nenhum áudio então cheque MSP

Xtal (item 1500) para Clock em 18.432MHz

Não

Não

Não

Não

Substitua Painel Analógico

Substitua PSU

Substitua Tuner

Substitua MSP Xtal (item 1500)

OK

Substitua Tuner

Page 20

20 DVDR3350H

ANOTAÇÕES:

Page 21

21DVDR3350H

DIAGRAMA EM BLOCO

CONTROL UNIT SLAVE

MICROPROCESSOR

UPD 16316GB-006

For Digital Video version only

DVD+RW ENGINE D4.3

TRAY CONTROL

SERVO

DISC

LASER

READ

WRITE

+12V

GND

GND

+5V

Digital Video

Input IEEE1394

1600-1

Front Keyboards

AUDIO L

AUDIO R

CVBS

S-VIDEO

6

IDE BUS

40

CONTROL LINES

1922

AFCRI

AFCLI

CVBSFIN

CFIN

YFIN

DIGITAL BOARD

1512

1571

IDE BUS

DDRAM

IDE BUS

1201

9

7

5

4

3

2

1

PHY

FLASH

DOMINO DMN-8652

MPEG 2, AC3 CODEC

I2C

EEPROM

(OPTION)

CONTROL LINES, AND SUPPLY LINES

DIG.VIDEO

RS2321671

SERVICE

VIDEO INPUT

PROCESSING

1111

ANALOG VIDEO

DIGITAL AUDIO

DIGITAL AUDIO

3V3

3V3

3V3

3V3

GND

12V

1

1501

ANALOG AUDIO / VIDEO

1551

1522

1536

GND

GND5VHDDSW

GND

NC

12

21

20

18

16

14

12

11

9

7

2

A_BCLK

A_WCLK

A_DATA

A_PCMCLK

D_BCLK

D_WCLK

D_DATA0

D_PCMCLK

D_KILL

SPDIF_OUT

A_xCLK

D_xCLK

ANALOG BOARD

1803

7

9

11

12

13

14

15

1205

12

14

16

18

20

22

1

3

5

7

9

1600

OL LINES SCK,D_FM,D_HOST,RDY_FM,ATN_FM,HOST_RESET

CONTR

1204

AINFR

AINFL

CVBSFIN

CFIN

YFIN

1800

YUV-YC-CVBS

F439

D_CVBS

F440

D_Y

F441

D_C

F442

D_V

F443

D_Y1

F444

D_U

CVBS-YUV-Y/C

A_V

A_U

A_Y

A_C

F438

A_YCVBS

AUDIO ENCODER I2S

AUDIO PCM I2S

ADC

DA C

INPUT/OUTPUT

PROCESSING &

SOURCE

SELECTION

CVBS

AUDIO L/R

Y

Pb

Pr

AUDIO L/R

CVBS

AUDIO L/R

S-VIDEO

IN-EXT

OUT1

OUT2

+12V

GND

GND

HARD DISK

+5V

IDE BUS

40

+12V

CON G

GND

GND

1

CON B

POWER SUPPLY UNIT

+5V

+12V

GND

GND

+5V

3V3

3V3

3V3

3V3

GND

12

5V

NC

12V

GND

GND

GND

HDDSW

11

1

1400

12VSTBY

STBY

5VSTBY

DD_ON

3V3STBY

IPFAIL

5NSTBY

GND

33VSTBY

GND

VGNSTBY

12VSTBY

STBY

5VSTBY

DD_ON

3V3STBY

IPFAIL

5NSTBY

GND

33VSTBY

GND

VGNSTBY

1

CON A

11

BUFFER

TUNER

1804

RF IN - ANTENNA

RF OUT - TV

(LOOP THROUGH)

DIGITAL AUDIO OUT

FAN

CON D

Page 22

22 DVDR3350H

PAINEL ANALÓGICO - DIAGRAMA EM BLOCO CONTROLE

FAN_CTRL

I2C

3V3

Level Shifter

INT

HOST_Reset

Fan

I2C Bus

I2C

5V

2

Reset

>=1

Reset

AFC

5VSTBY

Front Panel Processor

NEC uPD-16316GBT

2

1

Supply

RC

1

Front

Keys

2

35

VFT

Display

FRONT Board

DVDR

Hard Disk

IDE0

IDE1

DIGITAL BOARD

D_KILL_N

I2S

Multi Sound

Processor

MSP34x5

Frontend

Tuner

ADC / DAC

RSA1,RSA2

Audio Switches

HEF4052B

MUTE

>=1

KILL

IPFAIL

AKILL

STBY

Power

Supply

Page 23

23DVDR3350H

DIAGRAMA DE CONEXÕES

B

DVDR3350H, DVDR3360H and DVDR3370H

Note: To see the pin assignments, open the corresponding group by clicking the [+] / [-] icon(s) next to the left margin.

Hide all groups to see block diagram and interconnections in one screen.

Wire list is located at the bottom.

Analog board PSU

FAN1 Fan1 Mains

EH 2.5mm VH 7.6mm

ItemNr: 1804 Item Nr: J3

1FAN1P 1 MAINS_L

2 FAN1N 2 MAINS_N

FAV FCOM COM AIO VIO1 / VIO2 ANA_PS 120mm ANA_PS

2p 2p

PH 2mm FFC 1mm FFC 1mm FFC 1mm FFC 1mm PH 2mm PH 2mm

Item Nr: 1204 Item Nr: 1803 Item Nr: 1800 Item Nr: 1600 Item Nr: 1205 / 1206 Item Nr: 1400 Item Nr: J2

1 FYIN 1 GND 1 GND 1 GND 1 DB_PB 1 12VSTBY 1 12VSTBY

2 GND 2 FPSCK 2 SCL0 2 ABCK 2 GND 2 PWRCTL 2 PWRCTL

3 FCIN 3 D_FM 3 SDA0 3 AWCK 3 DG_Y 3 5VSTBY 3 5VSTBY

4 GND 4 D_HOST 4 RDY_FM 4 GND 4 GND 4 ODD_ON 4 HDD_ON

5 FCVBSIN 5 GND 5 D_FM 5 ADA0 5 DR_PR 5 3V3STBY 5 3V3STBY

6 GND 6 RDY_FM 6 D_HOST 6 GND 6 GND 6 IPFAIL 6 IPFAIL

7 FAULIN 7 ATN_FM 7 GND 7 AMCK 7 DY 7 5NSTBY 7 5NSTBY

8 GND 8 HOSTRST 8 FPSCK 8 GND 8 GND 8 GND 8GND

9 FAURIN 9 RC 9 ATN_FM 9 DBCK 9 DC 9 33VSTBY 9 33VSTBY

10 5V 10 HOSTRST 10 GND 10 GND 10 GND 10 GND

11 PWRCTL 11 TUNDET0 11 DWCK 11 DCVBS 11 VGNSTBY 11 VGNSTBY

12 PWRFAIL 12 TUNDET1 12 DDA0 12 GND

13 VKKN 13 AINSW0 13 GND 13 TUCVBS

14 12V 14 AINSW1 14 DMCK 14 GND

9p 14p 20p 22p 24p / 30p 11p 11p

8001 8002 8003 8004 8005

340mm 480mm 340mm 280mm 180mm

Front board

FAV FCOM COM AIO VIO1 / VIO2 HDD_IDE 280mm HDD_IDE

PH 2mm FFC 1mm FFC 1mm FFC 1mm FFC 1mm IDE 2.54mm IDE 2.54mm

Item Nr: 1300 Item Nr: 1201 Item Nr: 1551 Item Nr: 1536 Item Nr: 1522 / 1521 Item Nr: 1671 Item Nr: NA

1 FYIN 1 GND 1 GND 1 GND 1 DB_PB 1 RSTN 21 DMARQ 1 RSTN 21 DMARQ

2GND 2SCK 2 SCL0 2 ABCK 2 GND 2 GND 22 GND 2 GND 22 GND

3 FCIN 3 D_FM 3 SDA0 3 AWCK 3 DG_Y 3 DD[7] 23 DIOWN 3 DD[7] 23 DIOWN

4 GND 4 D_HOST 4 RDY_FM 4 GND 4 GND 4 DD[8] 24 GND 4 DD[8] 24 GND

5 FCVBSIN 5 GND 5 D_FM 5 ADA0 5 DR_PR 5 DD[6] 25 DIORN 5 DD[6] 25 DIORN

6 GND 6 RDY_FM 6 D_HOST 6 GND 6 GND 6 DD[9] 26 GND 6 DD[9] 26 GND

7 FAULIN 7 ATN_FM 7 GND 7 AMCK 7 DY 7 DD[5] 27 IORDY 7 DD[5] 27 IORDY

8 GND 8 HOSTRST 8 FPSCK 8 GND 8 GND 8 DD[10] 28 CSEL 8 DD[10] 28 CSEL

9 FAURIN 9 RC 9 ATN_FM 9 DBCK 9 DC 9 DD[4] 29 DMACKN 9 DD[4] 29 DMACKN

10 5V 10 HOSTRST 10 GND 10 GND 10 DD[11] 30 GND 10 DD[11] 30 GND

11 PWRCTL 11 TUNDET0 11 DWCK 11 DCVBS 11 DD[3] 31 INTRQ 11 DD[3] 31 INTRQ

12 PWRFAIL 12 TUNDET1 12 DDA0 12 GND 12 DD[12] 32 IOCS16 12 DD[12] 32 IOCS16

13 VKKN 13 AINSW0 13 GND 13 TUCVBS 13 DD[2] 33 DA1 13 DD[2] 33 DA1

14 12V 14 AINSW1 14 DMCK 14 GND 14 DD[13] 34 PDIAGN 14 DD[13] 34 PDIAGN

9p 14p 20p 22p 24p / 30p 40p 40p

USB (option) Not used USB (option) HDD_PS 180mm HDD_PS

PH 2mm PH 2mm IDE_PSU EH 2.5mm

Item Nr: 1401 Item Nr: 1502 Item Nr: NA Item Nr: J6

1 USB5V 1 USB5V 1 12VH 1 12VH

2 USBP 2 USBP 2GND 2GND

3 USBM 3 USBM 3GND 3GND

4GND 4GND 4 5VH 4 5VH

4p 4p 4p 4p

STBY IEEE1394 180mm IEEE1394 DIG_PS 220mm DIG_PS

DIPMATE PH 2mm PH 2mm PH 2mm PH 2mm

Item Nr: 0100 Item Nr: 1219 Item Nr: 1511 Item Nr: 1501 2Item Nr: J1

2p 6p 6p 12p 12p

8013 ODD_IDE 280mm ODD_IDE

220mm IDE 2.54mm IDE 2.54mm

Standby board

STBY ODD_PS 340mm ODD_PS

DIPMATE IDE_PSU EH 2.5mm

Item Nr: 0013 Item Nr: NA Item Nr: J5

2p 4p 4p

15 FANCTL 15 GND 15 RCVBSIN

16 FBSCRT 16 AMUTE 16 GND

17 SBSCRT0 17 AINCOAX 17 RYIN

18 SBSCRT1 18 NC 18 GND

19 GND 19 AINOPT 19 RCIN

20 ODD_ON 20 GND 20 GND

21 SPDIFO 21 FCVBSIN

22 GND 22 FCIN

23 GND

24 FYIN

25 GND

26 AR_PR

27 GND

28 AB_PB

29 GND

30 AG_Y

Digital board

15 FANCTL 15 GND 15 RCVBSIN 15 DD[1] 35 DA0 15 DD[1] 35 DA0

16 FBSCRT 16 AMUTE 16 GND 16 DD[14] 36 DA2 16 DD[14] 36 DA2

17 SBSCRT0 17 AINCOAX 17 RYIN 17 DD[0] 37 CS0N 17 DD[0] 37 CS0N

18 SBSCRT1 18 NC 18 GND 18 DD[15] 38 CS1N 18 DD[15] 38 CS1N

19 GND 19 AINOPT 19 RCIN 19 GND 39 DASPN 19 GND 39 DASPN

20 ODD_ON 20 GND 20 GND 20 Keypin 40 GND 20 Keypin 40 GND

21 SPDIFO 21 FCVBSIN

22 GND 22 FCIN

23 GND

24 FYIN

25 GND

26 AR_PR

27 GND

28 AB_PB

29 GND

30 AG_Y

8011 8031

8012 8033

Item Nr: 1571 Item Nr: NA

40p 40p

8006

HDD

8021

ODD

8022

8000

8032

Wire list

Item 12NC Description Remark

8000 2422 070 98202 MAINSCORD UL 6A 2M3 VH BK

8001 3104 157 02021 CBLE PH 9P/340/9P PH 26ST BK Front board AV input

8002 3139 241 01371 FFC FOIL 14P/480/14P BD 1MMP Front board communication IO

8003 3139 241 01361 FFC FOIL 20P/340/20P BD 1MMP Digital board communication IO

8004 3139 111 03991 FFC FOIL 22P/280/22P BD 1MMP Audio IO

8005 3139 110 35851 FFC FOIL 24P/180/24P BD 1MMP Video IO

8006 3139 110 28181 CWAS 11PH/11PH 120 6+5 BK 26S Analog board power supply

8012 3139 110 27881 CBLE PH 06P/180/06P PH 26ST BK Front board IEEE1394

8013 3139 110 37171 CBLE HR 02P/220/02P OE26 OS BK Front board to Standby board

8021 3139 241 00921 CBLE IDE 40P/280/40P IDE UL Hard disk drive IDE

8022 3139 241 00921 CBLE IDE 40P/280/40P IDE UL Optical disk drive IDE

8031 3103 601 00472 CBLE HR 4P/180/4P LC UL Hard disk drive power supply

8032 3139 241 01211 CBLE HR 04P/340/04P LC UL Optical disk drive power supply

8033 3139 110 28301 CBLE PH 12P/220/12P PH 26ST BK Digital board power supply

Mains cord (NAFTA)

Page 24

24 DVDR3350H

PAINEL ANALÓGICO - FORMAS DE ONDAS

F219 Y_OUT F220 C_OUT F222 CVBS_OUT F236 D_C

F237 D_Y F238 D_VR F239 D_YG F240 D_UB

I302 AFER I304 AFEL I619 ALDAC I621 ARDAC

I714 D_OUT 7500MSP XTAL_IN 7500MSP XTAL_OUT

Page 25

25DVDR3350H

PAINEL ANALÓGICO - FORMAS DE ONDAS

AUD_BCKI T537 AUD_BOKO T541 AUD_DAI(0) T539 AUD_DAO(0) T543

AUD_MCKI T540 AUD_MCKO T544 AUD_WCKI T538 AUD_WCKO T542

VOA_RPr T521VOA_BPb T518

VOA_CVBS T524

VOA_GY T520

VOA_SC T523

VOA_SY T522

Page 26

Page 27

Page 28

28 DVDR3350H

ESQUEMA ELÉTRICO- PAINEL ANALÓGICO - VÍDEO FRONTAL

A

B

C

D

E

F

G

H

1

3

5624

789101112

0803 H7

1100 F1

1101 C1

2100 B6

A

B

C

D

E

F

2101 A11

2102 F5

2103 F6

2104 F6

2105 H3

2106 H3

2107 F4

2108 E7

2109 A11

2110 E6

2111 D5

2112 D5

2113 B2

2114 B3

3100 B4

3101 B5

3102 C4

3103 H5

3104 G5

3105 H6

3106 C8

3107 E11

3108 D8

3109 E8

3110 F8

3113 C11

4100 E4

4101 F3

5100 A11

5102 E7

5103 E5

5104 G3

5106 F7

5107 C5

7100 B5

7102 H6

7104-1 C10

7104-2 E10

F100 D9

F101 E3

F102 B2

F103 E3

I100 E6

I101 E7

I102 F6

I103 F7

I104 D6

I105 F3

I106 F3

I107 G3

I108 G6

I114 H4

from PS

5VSTBY

5V

33VSTBY

81

9102

VIDOUT

RENUT

SIFOUT

2ZQMT

1011

0212

SIFOUT

AFTOUT

RENUT

2ZQMT

0011

AFT

GND2

VTU

NC5

MB

RFAGC

SDA

SCL

GND1

AOUT

NC4

NC3

NC2

NC1

BB

12

91

VOUT

NC4

TU

AOUT

DATA

CLK

NC3

NC2

NC1

VIN

CRTL

PLUSB

CHSW

AIN

22

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

18

17

16

15

14

13

12

11

10

9

8

6

5

4

3

2

F102

3112

V52u22

4112

n01

3100

I116

100R

I119

I118

F103

F101

1014

I106

4100

7012

7100

BC857BW

I117

desuton

2013

R001

V057u4

2112

n001

2012

0u1

1112

5103

Bead

5107

10u

n01

5V_FV

1013

33VSTBY

5VSTBY

n001

0012

0K1

CVBS_TV

to IOV,FOME

5V

6013

K01

8013

K51

to MSP

SIF1

3012

I104

0112

I100

I102

desuton

4012

p74

V52u22

8012

n01

5102

I101

I103

SDA_5V

from/to CU

SCL_5V

from CU

Bead

5106

Bead

desuton

p74

F100

5V

9013

K81

0113

8K6

5VSTBY

5V

84

3

2

5

6

7104-1

LM393D

5V

84

7104-2

LM393D

33VSTBY5V

5V

3113

1

5V

7013

7

5V

0015

u22

5V_FV

V3.6u74

1012

K01

K01

9012

TUN_DET0

to CU

TUN_DET1

to CU

n01

For use with TMZH2-036 tuner only

I105

I115 H5

G

H

I116 B4

I117 B5

I118 D4

I119 C4

V5

5104

6u8

5012

GND

SBVC_D

OCMA

I107

WSC

6012

7u4

n01

MSW

I114

3103

4K7

V5

4013

I115

GND

V5

I108

K74

BC857BW

7102

5013

K74

BARCODE

0803

Frontend Video FV

FA0

123456789101112

3139_243_32694_a3_sh130_sh1.pdf 2005-07-08

Page 29

29DVDR3350H

PAINEL ANALÓGICO ENTRADA/SAÍDA DE VÍDEO

12345678910

IO0

REAR IN 2

LPR6520-G020G

11208

2

3

4

L2NIA

R2NIA

A

AR

AL

CVBS

5NESD

B

REAR IN 2

F243

F244

F210

F204

F211

F201

F202

F203

1023

GND

4200

1

3

4

2

1024

GND

3204

75R

3205

75R

3206

75R

5NESD

*

*

*

CVBS_TV

F226

F205

F206

21C-483XZB

R57

3026

%1

n001

GND

GND

GND

GND

RFNIA

%1

R57

5NESD

GND

21C-483XZB

2023

8022

5NESD

BZX384-C12

6207

BZX384-C12

6208

BZX384-C12

6209

F227

LFNIA

3022

GND

21C-483XZB

2026

4026

**

*

21C-483XZB

0026

p074

5NESD

21C-483XZB

1026

4022

p074

5NESD

GND

2205

10u

4208

4209

2206

2207

10u

1u0

%1

21C-483XZB

3023

R57

5NESD

GND

2209

DSEN5

1u0

2210

1u0

2211

10u

2212

10u

2217

10u

2218

1u0

2216

10u

21C-483XZB

5026

6026

5NESD

*

*

*

4210

4211

AR

AL

C

CVBS

T-331520-10-10

1207-1

4

3

2

1

GND

D

REAR IN

S-CONN

1202

TCS79

Y

E

GND

C

75

6

GND

GND

F

V

NIRAER

U

G

H

Y

T-331520-10-10

1207-3

CVBSFIN

YFIN

CFIN

AINFL

AINFR

11

10

9

8

1204

B9B-PH-K

GND

F207

F208

F209

1

2

3

4

5

6

7

8

9

GND

I

Video In/Out IOV

*

OPTION

0022

GND

DSEN5

5VSTBY

F200

n001

2022

n001

1022

GND

GND

5NSTBY

3200

1K0

u01

5NSTBY

IO0

4206

4207

GND

F241

822F

922F

642F

032F

542F

45678

3

BU_A

V_DNG

5021

RV_A

1

NIF_Y

V_D

NG

742F

3456789

9

01

NIF_C

NIF_SBVC

V_DNG

GND

*

6021

1

V_DNG

GY_A

5VSTBY

*

3024

132F

21314151617181

11

RAER_C

V_DNG

C_DNG

*

2024

232F

332F

Y_DNG

RAER_Y

5V

0222

432F

532F

01112131415161

91202

SBVC_D

UT_SBVC

V_DNG

RAER_SBVC

D_DNG

5V

u01

GND

IO0

632F

832F

732F

7181912021222

122232425262728292

Y_D

C_D

D_DNG

D_DNG

D_DNG

D_DNG

RV_D

5V

100n

2221

7200

R033

7201

R033

7202

R033

GND

GND

100n

2223

GND

100n

2225

GND

3423

R051

GND

4423

R051

GND

3227

150R

8223

5423

R051

R051

GND

BC847BW

I200

9023

100n

2222

5NSTBY

GND

3207

150R

04231423

8023

R051

R051

GND

GND

5V

BC847BW

I201

1113

100n

2224

5NSTBY

GND

3211

150R

2123

R051

R051

GND

GND

5V

3215

150R

2423

6123

R051

R051

GND

GND

F242

932F

042F

7C2-S42WLH

42

32

7C2-S03WLH

03

BU_D

D_DNG

GY_D

GND

D_DNG

BC847BW

I202

3123

100n

2226

5NSTBY

from / to Digital Board

WS0

11 12 13

GND_D

GND

GND_C

GND_Y

GND_C

GND_D

GND

GND_V

GND

GND

3210

1%

68R

6210

3214

68R

3218

68R

1%

5NESD

1%

BZX384-C12

6211

BZX384-C12

6212

BZX384-C12

5V

1223

R033

3219

F218

BC857BW

150R

0223

R051

7203

0522

p74

5NSTBY

5V

GND

3222

150R

3223

1522

R051

GND

7204

BC847BW

p74

I203

4223

R033

5NSTBY

5V

2229

100n

9223

5NSTBY

7205

BC847BW

R033

F221

2230

100n

F225

2213

100n

F216

2215

100n

2227

100n

3225

68R

2228

100n

DNG

3230

68R

DNG

REAR OUT

F212

DNG

F213

F214

F215

DNG

F217

2214

100n

DNG

6223

R65

DNG

F219

1%

F220

3126

DNG

5NESD

5NESD

21C-483XZB

5126

1%

TUORA

TUOLA

1201-3

T-331520-10-10

8

9

10

11

GND

21C-483XZB

21C-483XZB

4126

GND

5NESD

REAR OUT 1

GND

F222

F223

F224

T-331520-10-10

Y

U

V

S-CONN

TCS79

1

3

4

2

756

GND

CVBS

1

2

3

AL

4

AR

1201-1

1203

GND

IO0

Y

C

GND

3139_243_32694_a2_sh130_sh2.pdf 2005-07-08

12345

678

910111213

1201-1 I13

1201-3 C13

1202 E2

1203 F13

1204 H2

1205 I7

1206 I6

1207-1 C1

1207-3 G1

1208 A2

2200 A5

2201 A6

A

2202 A6

2203 C3

2204 C4

2205 D4

2206 E5

2207 E5

2208 F3

2209 F4

2210 G4

2211 G4

2212 G4

2213 E12

B

2214 E12

2215 E12

2216 H4

2217 H4

2218 H4

2220 A8

2221 A10

2222 B10

2223 C10

2224 D10

2225 D10

2226 E10

C

2227 F12

2228 G12

2229 H11

2230 I11

2250 E11

2251 F11

3111 C10

3200 A6

3201 D3

3202 E3

3203 F4

D

3204 F2

3205 G2

3206 G2

3207 A9

3208 B9

3209 B10

3210 C11

3211 C9

3212 C9

3213 E10

3214 C11

3215 E9

E

3216 E9

3218 D11

3219 E11

3220 E11

3221 E11

3222 F11

3223 F11

3224 G11

3225 F12

3226 F12

3227 H10

3228 H10

F

3229 I11

3230 H12

3240 B9

3241 C9

3242 E9

3243 E10

3244 F10

3245 H10

4200 D2

4201 E2

4202 G7

G

4203 G7

4206 G7

4207 G7

4208 D4

4209 E5

4210 H4

4211 H4

6200 C4

6201 C4

6202 D3

6203 E3

6204 E3

H

6205 F4

6206 F4

6207 F3

6208 G3

6209 G3

6210 C11

6211 D11

6212 D11

6213 G12

6214 G12

6215 H12

7200 A10

I

7201 C10

7202 D10

7203 E11

7204 F11

7205 H11

F200 A6

F201 B2

F202 C2

F203 C2

F204 C2

F205 E3

F206 E3

F207 G2

F208 G2

F209 G2

F210 H2

F211 H2

F212 C12

F213 C12

F214 C12

F215 D12

F216 E12

F217 E12

F218 E11

F219 F12

F220 F12

F221 H11

F222 H12

F223 I12

F224 I12

F225 H11

F226 I2

F227 I3

F228 I6

F229 I6

F230 I7

F231 I7

F232 I7

F233 I7

F234 I8

F235 I8

F236 I8

F237 I8

F238 I8

F239 I8

F240 I8

F241 H6

F242 H9

F243 H2

F244 H2

F245 I7

F246 I7

F247 I7

I200 B10

I201 C10

I202 E10

I203 F11

Page 30

30 DVDR3350H

PAINEL ANALÓGICO ENTRADA E SAÍDA DE ÁUDIO

A

B

C

D

E

F

REAR IN 1

AR

AL

T-331520-10-10

1207-2

AIN2R

AIN2L

AFER

AFEL

ARDAC

ALDAC

123456789

7

6

5

GND

F300

F301

0036

5NESD

1036

5NESD

2304

2305

I302

I304

1u0

1u0

21C-483XZB

21C-483XZB

10u

10u

2308

1u0

2309

1u0

2310

2312

16V

16V

1032

GND

3032

GND

p074

p074

I300

2033

GND

I303

I305

I306

I307

Audio In/Out IOA

2300

1u0

2302

1u0

DSEN5

0033

K001

GND

5NESD 5VSTBY 5NSTBY

1033

K001

GND

K001

I301

3033

K001

GND

3304

5033

GND

7033

GND

K001

K001

470R

3306

470R

*

OPTION

1132

GND

3132

GND

YBTSV5

p074

p074

GND

GND

YBTSN5

7302

BC817-25W

7303

BC817-25W

PDTA124EU

PDTA124EU

I308

I309

7304

7305

LFNIA

6032

2133

GND

5VSTBY

5VSTBY

RFNIA

7032

0u1

K001

3133

GND

0u1

K001

6306

BAS316

BAS316

6304

6307

BAS316

BAS316

6305

K001

GND

BMUTEC

AMUTEC

4133

LLIKA

1ASR

K001

GND

I310

100R

3311

100R

I312

I313

I314

I315

3310

DNG

5133

2ASR

I311

HEF4052B

10

9

6

12

14

15

11

1

5

2

4

7301

1

G4

0

1

2

3

0

1

2

3

2036

5NESD

3036

5NESD

5VSTBY

4X

MDX

VEE VSS

7

5NSTBY

21C-483XZB

21C-483XZB

030

61

VDD

GND

5VSTBY

I316

13

3

8

p074

4132

5132

GND

GND

I317

3316

1K0

813I

I319

7133

0K1

5VSTBY

I320

5

6

I321

5NSTBY

p074

3

2

5NSTBY

7300-2

8

MC33078D

4

GND

8

4

3139_243_32694_a3_sh130_sh3.pdf 2005-07-08

IO0

2316

6.3V47u

2317

100n

7300-1

MC33078D

1

2318

100n

2319

6.3V47u

7

REAR OUT 2

7

6

5

T-331520-10-10

1201-2

AROUT

ALOUT

DNG

DNGDNG

ARADC

DNG

ALADC

AR

AL

A

B

C

D

E

F

1201-2 E9

1207-2 A1

2300 A3

2301 A2

2302 B3

2303 B2

2304 B2

2305 C2

2306 A5

2307 A5

2308 D2

2309 D2

2310 D2

2311 E4

2312 E2

2313 F4

2314 E8

2315 E8

2316 B9

2317 B9

2318 C9

2319 C9

3300 A3

3301 B3

3302 C2

3303 C3

3304 D3

3305 E3

3306 E3

3307 F3

3310 D6

3311 E6

3312 C5

3313 C5

3314 C6

3315 C6

3316 B8

3317 C8

6300 A2

6301 B2

6302 E7

6303 F7

6304 E5

6305 F5

6306 E5

6307 F5

7300-1 B9

7300-2 C9

7301 B7

7302 E5

7303 F5

7304 E5

7305 F5

F300 A2

F301 B2

I300 B2

I301 C3

I302 D2

I303 D2

I304 D2

I305 D2

I306 D2

I307 E2

I308 E5

I309 F5

I310 A6

I311 A7

I312 B6

I313 C6

I314 C6

I315 C6

I316 B8

I317 B8

I318 C8

I319 C8

I320 C8

I321 D8

123456789

Page 31

31DVDR3350H

PAINEL ANALÓGICO - FONTE DE ALIMENTAÇÃO

A

B

C

1400 A1

2352 G4

2400 G1

2410 B4

2411 B4

2412 B5

2413 D4

2414 D4

2415 D5

2416 E4

2417 E4

2418 E5

3400 D2

3401 E2

3402 E2

3403 F2

3404 F1

3405 F2

3406 F3

3407 G3

3408 G5

3409 G5

3410 H4

3411 A4

3412 A5

5400 B5

5401 C5

5402 E4

6400 G1

6401 G1

7400 F2

7401 G3

7402 F4

7403 H4

7404 H5

7405 A4

F400 A2

F401 A2

F402 A2

F403 A2

F404 A2

F405 A2

F406 A2

F407 A2

F408 A2

F409 B2

F410 B2

F411 B2

F412 B2

F413 B2

F414 B2

F415 B4

F416 B4

F417 E5

F418 G5

123456

12VSTBY

to IOV,CU

STBY

from CU

5VSTBY2

to CU

5VSTBY

to IOV,IOA,DAC_ADC,CU

ODD_ON

from CU

3V3STBY

to CU

YLPPUSREWOPmorf

12VSTBY

5VSTBY

DD_ON

3V3STBY

5NSTBY

33VSTBY

VGNSTBY

WS0

PS0

STBY

IPFAIL

GND

GND

B11B-PH-K

1400

F400

F402

F403

F405

F406

F408

F409

F410

F412

F414

F401

F404

F407

F411

F413

12VSTBY

1

2

3

4

5

6

7

8

9

10

11

5VSTBY

3411

4K7

BC847BW

F415

0142

3142

12VSTBY

7405

5400

F416

V610m1

22u

n001

1142

5401

10u

V61u022

4142

n001

3412

4K7

2142

n001

5VSTBY

n001

5142

F419 H6

F420 H2

I400 F2

I401 G3

A

B

C

D

E

F

G

H

0046

1046

0043

R74R33

u022

V61

50V

7142

5VSTBY

K001

7403

BC857BW

5402

10u

n001

7402

SI2306DS

8142

F418

3409

3K3

n001

12VSTBY

4043

2V8C-483XZB

613SAB

1043

R74

6142

2043

3043

R33

7K4

3405

100R

n001

0042

004I

7400

BC847BW

F420

7401

PDTC124EU

3V3STBY

I401

6043

2M2

2352

100n

7043

2M2

0143

3139_243_32694_a4_sh130_sh4.pdf 2005-07-08

F417

YBTS3V3

7404

BC847BW

IPFAIL

to DAC_ADC

5NSTBY

to IOA,IOV,PROG,CU,

DAC_ADC

33VSTBY

to FV

VGNSTBY

to CU

to IOV,FOME,FV,MSP,

DAC_ADC,DIGIO,PROG,CU

8043

K01

F419

5V

3V3SW

to DAC_ADC

8VSTBY

to MSP

D

E

F

G

H

12

34

5

6

Page 32

32 DVDR3350H

PAINEL ANALÓGICO - PROCESSAMENTO DE MULTI ÁUDIO

A

B

C

D

E

F

SCL_5V

from/to CU

SDA_5V

from/to CU

SIF1

from FV

from DAC_ADC

ALDAC

from DAC_ADC

123

from PS

8VSTBY

5V

V52u01

0052

7500

12

13

14

15

16

17

21

MSP3425G

I2C_CL

I2C_DA

I2S_CL

I2S_WS

I2S_DA_OUT

I2S_DA_IN1

I2S_DA_IN2

ANA_IN-3

ANA_IN+2

MONO_IN43

SC1_IN_R41

SC1_IN_L40

SC2_IN_R38

SC2_IN_L37

DEMODULATOR

1FERV

2FERV

92

52

LC_RDA81LES_RDA

IDENT

A/D

A/D

SSVHA

GSA

93

53

8VSTBY

3502

2K2

3503

2K2

5V

3501

I504

I506

2503

1u0

2504

1u0

I500

I501

I502

I503

I505

I507

100R3500

100R

2501

56p

2502

56p

K215053

K214053

456789

1500 F6

2500 A1

2501 C1

2502 C1

A

B

2503 E2

2504 E2

2505 A5

2506 A5

2507 A6

2508 A6

2509 A6

2510 B8

2511 C7

2512 C7

2513 D7

2514 D7

2515 E7

2516 E7

2517 F5

2518 F6

2519 F6

3500 B1

3501 B1

3502 E1

3503 E1

3504 E1

2ASR

1ASR

AOIot

AOIot

V52u01

5052

6052

n01

115I

9

01

8

1OI_RTC_D

4

0OI_RTC_D

NETSET

I512

24

33

POTFERV

8VSTBY

V52u01

8052

7052

I513

43

PUSVHA

M_LPAC

STBYQ

DVSUP

RESETQ

V61u74

9052

n001

5V

613SAB

0056

6053

K01

I514

11

I515

19

I516

22

7053

7K4

5V

5015

u01

0152

n001

FA0

3505 E1

C

D

3506 B7

3507 B8

3508 C8

5105 B8

5500 F5

6500 B7

7500 A2

I500 B2

I501 B2

I502 C2

I503 C2

I504 D1

I505 D2

I506 E1

I507 E2

I508 F5

I509 F6

I510 F6

I511 A3

I512 A6

FM1

FM2

NICAM A

NICAM B

IDENT

SCART-L

SCART-R

S1...4

I2SL/R

LOUDSPEAKER R

LOUDSPEAKER L

DFP

I2SL/R

HEADPHONE R

HEADPHONE L

D/A

D/A

DACM_R 26

LOUDSPEAKER

DACM_L 27

AGNDC

1152

u01

I517

2152

I518

36

V057u4

3152

4152

n01

3508

100R

0n1

AMCO

to FV

I513 A6

I514 B7

I515 B7

I516 B7

I517 C7

I518 D7

E

F

I509

8152

SC1_OUT_R 30

SC1_OUT_L 31

NI_LATX

5

6

1500

18M432

3p3

5152

TUO_LATX

I510

9152

3p3

6152

0n1

0n1

VERSION TABLE

*

APAC

TAIWAN

S. KOREA

ALL OTHERS

MSP3425G MSP3415G

Pos. 7600

NAFTA

MSP3425G

SCART-R

SCART-L

SCART

SSVD

SSVA

44

02

Switching Facilities

NC

82

32

23

42

5V

5500

10u

D/A

D/A

PUSVA

PT

7

1

I508

7152

n001

AFER

to IOA

AFELARDAC

to IOA

Multi Sound Processing MSP

*

OPTION

3139_243_32694_a3_sh130_sh5.pdf 2005-07-08

123456789

Page 33

33DVDR3350H

PAINEL ANALÓGICO- CONVERSOR DE ÁUDIO (DAC_ADC)

123456789

DA2

A

AKILL

to CINCH

I600

0063

1063

K001

K22

5NSTBY

GND GND

B

IPFAIL

from PS

DAINOPT

from DIGIO

DAINCOAX

from DIGIO

DAOUT

to DIGIO

C

IO0

GND

DAOUT

GND

DAINOPT

draoBlatigiDot/morf

DAINCOAX

DKILL

GND

D_PCMCLK

GND

D_DATA0

D_WCLK

D

E

GND

D_BCLK

GND

A_PCMCLK

GND

A_DAT

GND

A_WCLK

A_BCLK

GND

ARADC

from IOA

ALADC

from IOA

HLW22S-2C7

F600

F601

F602

DNG

1600

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

F612

2607

47u 6.3V

2608

6.3V47u

DNG

DNG

DNG

DNG

DNG

DNG

DNG

I606

I607

DA2

F

PDTA124EU

0062DNG

n22

F603

F604

F605

F606

F607

F608

F609

F610

F611

3614

10K

3615

10K

DA2

5VSTBY

7600

613SAB

0066

5VSTBY

5063

7K4

3608 22R

3612 22R

3606

22R

3610

22R

DA2

6603

BAS316

GND

3607

22R

3609

22R

3611

22R

5VSTBY

2063

I601

7602

PDTC124EU

22R3613

12VSTBY

12VSTBY

K22

I603

I604

I605

I609

5062

4062

3062

p33

6062

p33

p33

p33

GND

3V3SW

3V3SW

MCLK

SDIN

LRCK

SCLK

DA0

F613

5V

5VSTBY

5V 5VSTBY

6163

K74

8163

K74

3V3SW

2162

AA

5NSTBY

5NSTBY

I608

n001

DA0

2263

7u4

0162

GND

A

DNG

9163

5601

10u

4162

A

CS4351

1

2

3

4

10

8

K01

7

3263

K01

7606

n001

UDA1361TS

8

3

2

1

6

7

I612

14

0K1

GND

V3.6u001

n001

5162

11

7603

SDIN

SCLK

LRCK

MCLK

RST

DIF0

SDA

CDIN

DIF1

SCL

CCLK

61

VDDA VRP

24-BIT AUDIO

SYSCLK

VINR

VREF

VINL

SFOR

PWON

MSSEL

VSSA VSSD

51

3620

4R7

I624

192 kHz DAC

I614

GND

Φ

71

6

Φ

GND

5

61

A

5

I623

AMUTEC

BMUTEC

3V3SW

VDDD

ADC

DATAO

VRN

4

01

AAA

GND

2616

100n

3V3SW

02

VLVDVA_HVA

VBIAS

AOUTA

AOUTB

DEM

9

BCK

WS

AD0

GND

2617

100n

GND

12

13

VQ

19

14

18

15

9

CS

4263

GND

n001

1162

GND

13

11

12

V057u4

0262

9162

K01

I613

3262

n22

47u16V

2621

2622

100n

I616

I617

I618

I620

V61u74

A

4262

A

BC847BW

2626

50V 4u7

2628

7604

BC807-25W

n001

6263

7605

4u750V

12VSTBY

5263

9K3

0K1

3627

4K7

8263

5262

n001

K01

A

3629

680R

0363

K72

A

3631

680R

2363

K72

A

I619

7262

0n1

I621

9262

0n1

GND

3V3SW

AMUTEC

BMUTEC

ALDAC

ARDAC

c601

A

3V3SW

SDIN

SCLK

LRCK

MCLK

3621

100K

I615

8162

3V3SW

7163

u01

V3.6u001

9062

A

I610

I611

WS3V3

V3.6u74

3162

I622

4600

Audio Converter DAC_ADC

3139_243_32694_a3_sh130_sh6.pdf 2005-07-08

123

456789

1600 C1

2600 B1

2603 D3

2604 D3

2605 D4

2606 D4

2607 E1

2608 E1

2609 D5

2610 D6

A

2611 D7

2612 F5

2613 F5

2614 A6

2615 A6

2616 A7

2617 B7

2618 C5

2619 B7

2620 B8

2621 B8

2622 B8

B

2623 B8

2624 B8

2625 C9

2626 D8

2627 D9

2628 D8

2629 E9

3600 B1

3601 B1

3602 B3

3605 C2

C

3606 D2

3607 D2

3608 D2

3609 D2

3610 D2

3611 D2

3612 D2

3613 E2

3614 E2

3615 E2

3616 D4

3617 D5

D

3618 F4

3619 F6

3620 A6

3621 B5

3622 C6

3623 C6

3624 C7

3625 B9

3626 B8

3627 B9

3628 C9

3629 D9

E

3630 D9

3631 D9

3632 E9

4600 F6

5601 A6

6600 B2

6603 C2

7600 A2

7602 C2

7603 B6

7604 A8

F

7605 B9

7606 D6

F600 B1

F601 C1

F602 C1

F603 D2

F604 D1

F605 D1

F606 D2

F607 D1

F608 D1

F609 D1

F610 D1

F611 E1

F612 E1

F613 B4

I600 A1

I601 B3

I603 D4

I604 D4

I605 D3

I606 E1

I607 E1

I608 E5

I609 D3

I610 E6

I611 F5

I612 F6

I613 A8

I614 D6

I615 C5

I616 C8

I617 C8

I618 D8

I619 D9

I620 D8

I621 D9

I622 F5

I623 A7

I624 A6

c601 F9

Page 34

34 DVDR3350H

PAINEL ANALÓGICO DIGITAL - ENTRADA E SAÍDA 1 (DIGIO 1)

A

B

C

D

E

DAINCOAX

to DAC_ADC

DAINOPT

to DAC_ADC

DAOUT

from DAC_ADC

123456

SPmorf

5V

5V

i713

3703

*

desuton

5073

R065

100R

5V1

7700-6

74HCU04D

12

5V

0073

R074

I712

V01

1072

0072

n01

14

1

13

7

3704

*

10K

1073

0u1

K001

2073

K001

*

3706

750R

5V1

7700-1

I702

7073

I715

2702

100n

desuton

R001

3708

470R

74HCU04D

I716

*

14

I717

1

1

3709

2K2

2

7

74HCU04D

7700-3

74HCU04D

5

7700-2

3

5V1

5V1

14