Philips CBTS3384 Technical data

查询CBTS3384供应商查询CBTS3384供应商

INTEGRATED CIRCUITS

CBTS3384

10-bit bus switch with 5-bit output enables

and Schottky undershoot protection

Product data

Supersedes data of 2001 Feb 13

Philips

Semiconductors

2002 Dec 13

Philips Semiconductors Product data

CBTS3384

10-bit bus switch with 5-bit output enables

and Schottky undershoot protection

2

2002 Dec 13

FEATURES

• 5 Ω switch connection between two ports

• TTL compatible control input and output levels

• Undershoot protection included to prevent shoot through level

changes

• Latch-up protection exceeds 500 mA per JESD78

• ESD protection exceeds 2000 V HBM per JESD22-A114,

200 V MM per JESD22-A115 and 1000 V CDM per JESD22-C101

DESCRIPTION

The CBTS3384 provides ten bits of high-speed TTL-compatible bus

switching. The low on-state resistance of the switch allows

connections to be made with minimal propagation delay.

The CBTS3384 device is organized as two 5-bit bus switches with

separate output-enable (OE

) inputs. When OE is LOW, the switch is

on and port A is connected to B. When OE

is HIGH, the switch is

open and high-impedance state exists between the two ports.

The CBTS3384 is characterized for operation from -40 to +85 °C.

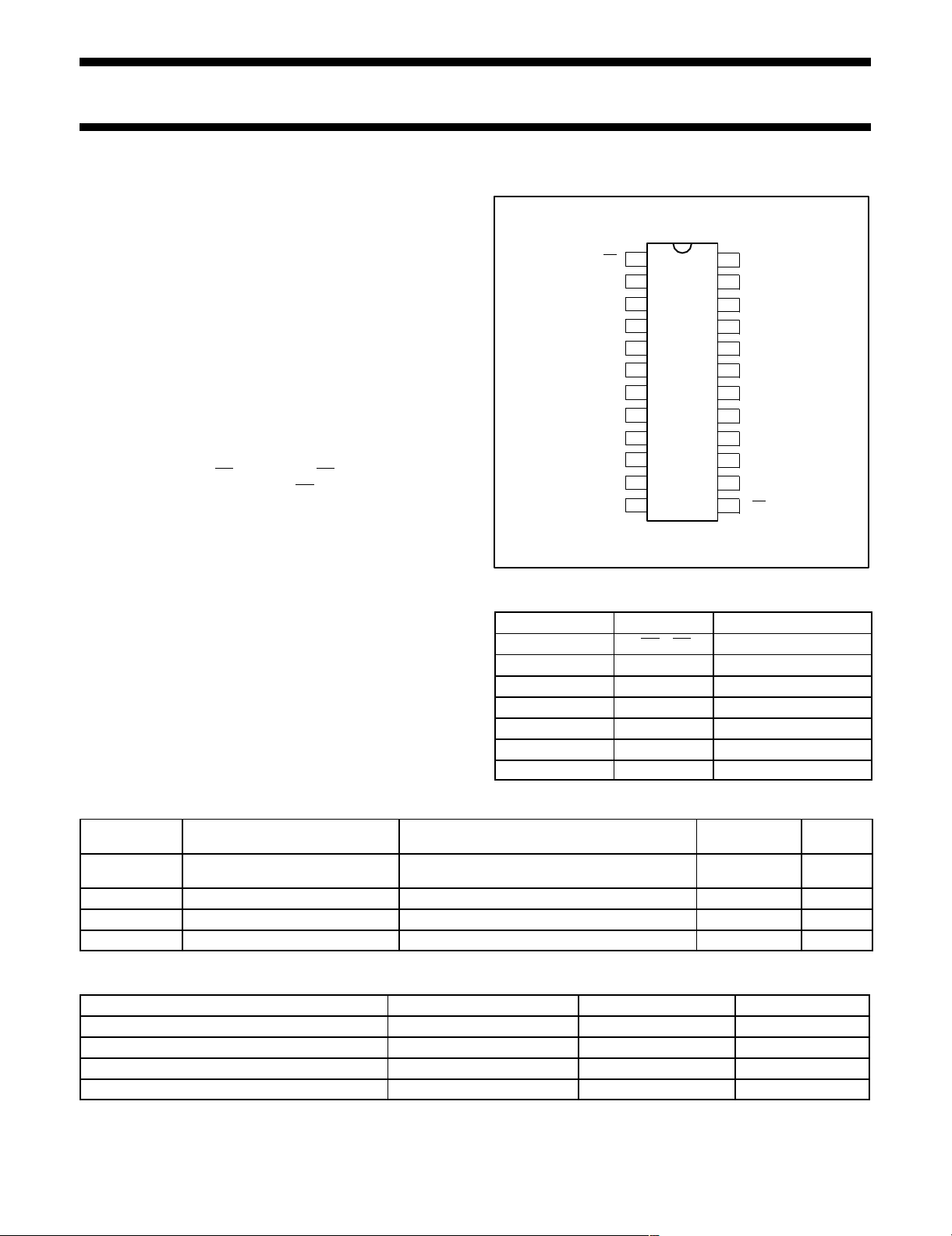

PIN CONFIGURATION

SA00502

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

1B1

1A1

1A2

1B2

1B3

1A3

1A4

1B4

1B5

1A5

GND

1OE

Vcc

2B5

2A5

2A4

2B4

2B3

2A3

2A2

2B2

2B1

2A1

2OE

PIN DESCRIPTION

PIN NUMBER SYMBOL NAME AND FUNCTION

1, 13 1OE, 2OE Output enables

3, 4, 7, 8, 11 1A1-1A5 Inputs

14, 17, 18, 21, 22 2A1-2A5 Inputs

2, 5, 6, 9, 10 1B1-1B5 Outputs

15, 16, 19, 20, 23 2B1-2B5 Outputs

12 GND Ground (0 V)

24 V

CC

Positive supply voltage

QUICK REFERENCE DATA

SYMBOL PARAMETER

CONDITIONS

T

amb

= 25 °C; GND = 0 V

TYPICAL UNIT

t

PLH

t

PHL

Propagation delay

An to Yn

CL = 50 pF; VCC = 5 V 250 ps

C

IN

Input capacitance VI = 0 V or V

CC

4 pF

C

OUT

Output capacitance Outputs disabled; VO = 0 V or V

CC

10 pF

I

CCZ

Total supply current Outputs disabled; VCC = 5.5 V 3 µA

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE ORDER CODE DWG NUMBER

24-Pin Plastic SO -40 to +85 °C CBTS3384D SOT137-1

24-Pin Plastic SSOP -40 to +85 °C CBTS3384DB SOT340-1

24-Pin Plastic SSOP (QSOP) -40 to +85 °C CBTS3384DK SOT556-1

24-Pin Plastic TSSOP -40 to +85 °C CBTS3384PW SOT355-1

Standard packing quantities and other packaging data is available at www.philipslogic.com/packaging.

Philips Semiconductors Product data

CBTS3384

10-bit bus switch with 5-bit output enables

and Schottky undershoot protection

2002 Dec 13

3

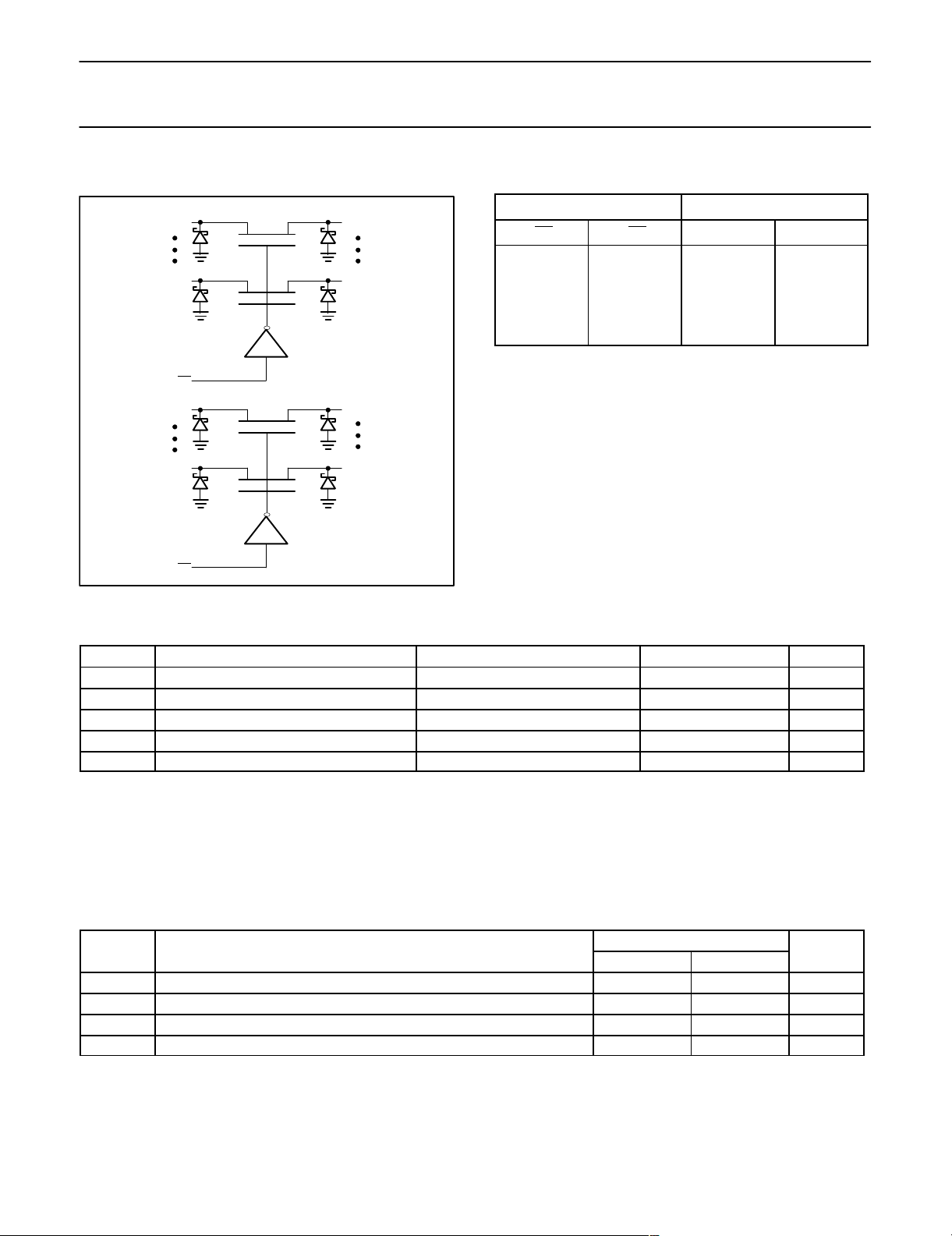

LOGIC SYMBOL

1A1

1A5

2A1

2A5

1B1

1B5

2B1

2B5

3

11

2

10

14

22

15

23

SA00504

13

1

2OE

1OE

FUNCTION TABLE

INPUTS OUTPUTS

1OE 2OE 1A, 1B 2A, 2B

L L 1A = 1B 2A= 2B

L H 1A = 1B Z

H L Z 2A = 2B

H H Z Z

H = High voltage level

L = Low voltage level

Z = High impedance “off” state

ABSOLUTE MAXIMUM RATINGS

1, 2

SYMBOL

PARAMETER CONDITIONS RATING UNIT

V

CC

DC supply voltage -0.5 to +7.0 V

I

IK

DC input diode current -50 mA

V

I

DC input voltage

3

-1.2 to +7.0 V

I

SW

DC output diode current VO < 0 ±128 mA

T

stg

Storage temperature range -65 to +150 °C

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction

temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

3. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

RECOMMENDED OPERATING CONDITIONS

LIMITS

SYMBOL PARAMETER

Min Max

UNIT

V

CC

DC supply voltage 4.5 5.5 V

V

IH

High-level input voltage 2.0 V

V

IL

Low-level Input voltage 0.8 V

T

amb

Operating free-air temperature range -40 +85 °C

Philips Semiconductors Product data

CBTS3384

10-bit bus switch with 5-bit output enables

and Schottky undershoot protection

2002 Dec 13

4

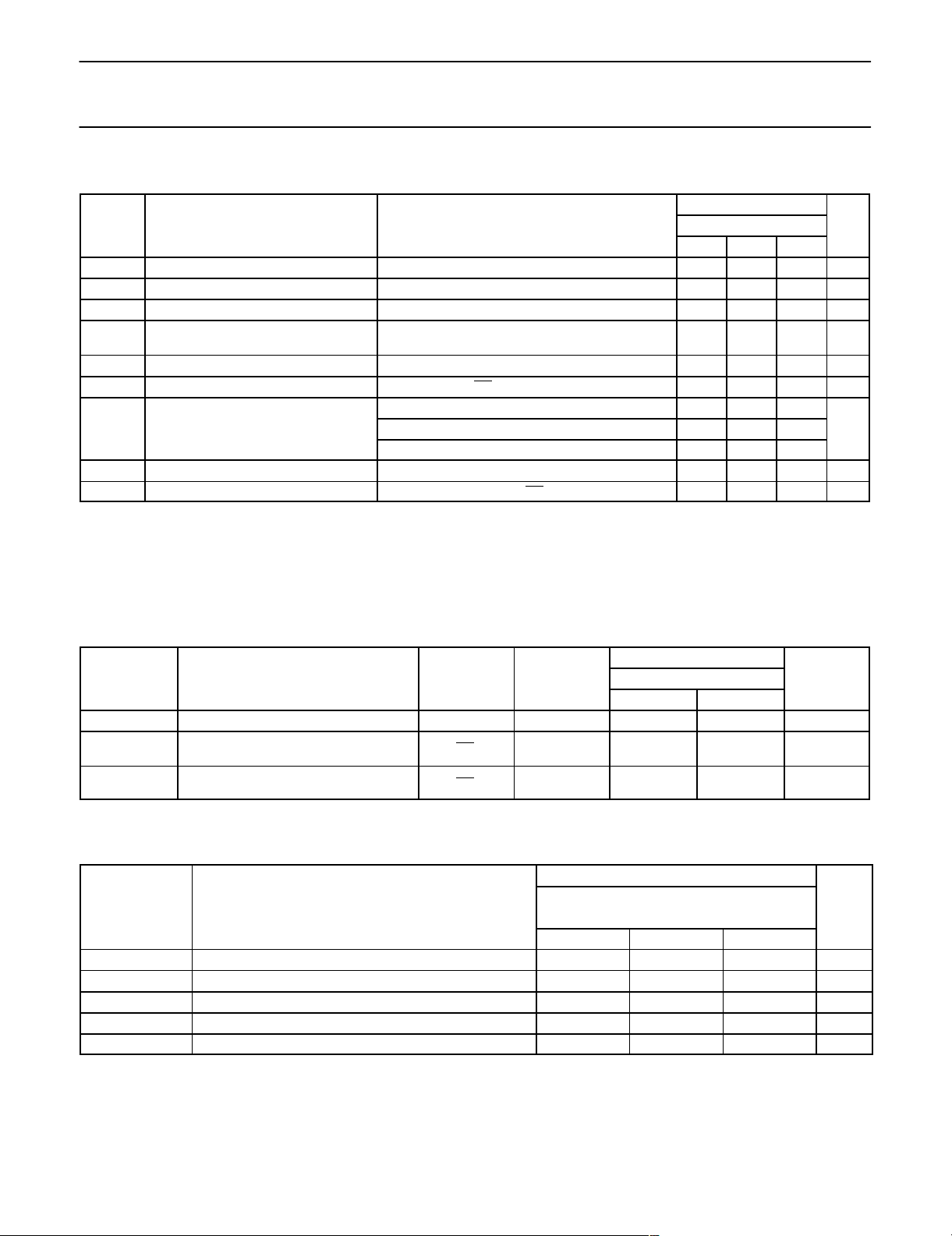

DC ELECTRICAL CHARACTERISTICS

LIMITS

SYMBOL PARAMETER TEST CONDITIONS

T

amb

= -40 to +85 °C

UNIT

Min Typ1Max

V

IK

Input clamp voltage VCC = 4.5 V; II = -18 mA — — -1.2 V

I

I

Input leakage current VCC = 5.5 V; VI = GND or 5.5 V — — ±1 µA

I

CC

Quiescent supply current

2

VCC = 5.5 V; IO = 0, VI = VCC or GND — — 3 µA

∆I

CC

Additional supply current per input pin

2

VCC = 5.5 V, one input at 3.4 V, other inputs at V

CC

or GND

— — 2.5 mA

C

I

Control pins VI= 3.0 V or 0 — 4 — pF

C

I(OFF)

Power-off leakage current VO = 3.0 V or 0, OE = V

CC

— 10 — pF

VCC = 4.5 V; VI = 0 V; II = 64 mA — 5 7

r

on

3

On-resistance

VCC = 4.5 V; VI = 0 V; II = 30 mA — 5 7

Ω

on

VCC = 4.5 V; VI = 2.4 V; II = -15 mA — 10 15

V

P

Pass voltage VI= VCC = 5.0 V; IO = -100 µA 3.4 3.6 3.9 V

I

UCP

Undershoot static current protection VCC = 5.0 V, IB = 400 µA; OE = 5.0 V; VB ≥ 3.0 V — 8 — mA

NOTES:

1. All typical values are at V

CC

= 5 V, T

amb

= 25 °C.

2. This is the increase in supply current for each input that is at the specified TTL voltage level rather than VCC or GND.

3. Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. On-state resistance is

determined by the lowest voltage of the two (A or B) terminals.

AC CHARACTERISTICS

GND = 0 V; tR; CL = 50 pF

LIMITS

SYMBOL PARAMETER

FROM TO

VCC = +5.0 V ±0.5 V

UNIT

(INPUT) (OUTPUT)

Min Max

t

pd

Propagation delay

1

A or B B or A — 0.25 ns

t

en

Output enable time

to High and Low level

OE A or B 1.0 5.7 ns

t

dis

Output disable time

from High and Low level

OE A or B 1.0 5.2 ns

NOTE:

1. This parameter is warranted but not production tested. The propagation delay is based on the RC time constant of the typical on-state

resistance of the switch and a load capacitance of 50 pF, when driven by an ideal voltage source (zero output impedance).

LIMITS

SYMBOL PARAMETER DESCRIPTION

-40 to +85° C

VCC = 5 V, ±0.5 V

UNIT

MIN. MEAN MAX.

t

PD

Propagation delay (see Note 1) — — 250 pS

t

PZH

Output enable time to High level 1.6 3.4 5.6 nS

t

PHZ

Output enable time from High level 1.7 3.3 5.5 nS

t

PZL

Output enable time to Low level 2.3 4 6 nS

t

PLZ

Output enable time from Low level 2.5 4.5 6.6 nS

NOTE:

1. This parameter is warranted but not production tested. The propagation delay is based on the RC time constant of the typical on-state

resistance of the switch and a load capacitance of 50 pF, when driven by an ideal voltage source (zero output impedance); at +25 °C.

Loading...

Loading...