Page 1

INTEGRATED CIRCUITS

CBTD3306

Dual bus switch with level shifting

Product data

File under Integrated Circuits — ICL03

2001 Nov 08

Page 2

Philips Semiconductors Product data

FUNCTION

CBTD3306Dual bus switch with level shifting

FEA TURES

•Designed to be used in 5 V to 3.3 V level shifting applications with

internal diode.

•5 Ω switch connection between two ports

•TTL-compatible input levels

•Package options include plastic small outline (SO) and

thin shrink small outline (TSSOP)

•Latch-up protection exceeds 100 mA per JESD78

•ESD protection exceeds 2000 V HBM per JESD22-A114 and

1000 V CDM per JESD22-C101

DESCRIPTION

The CBTD3306 Dual FET Bus Switch features independent line

switches. Each switch is disabled with the associated Output Enable

(OE

) input is high.

The CBTD3306 is characterized for operation from –40 to +85 °C.

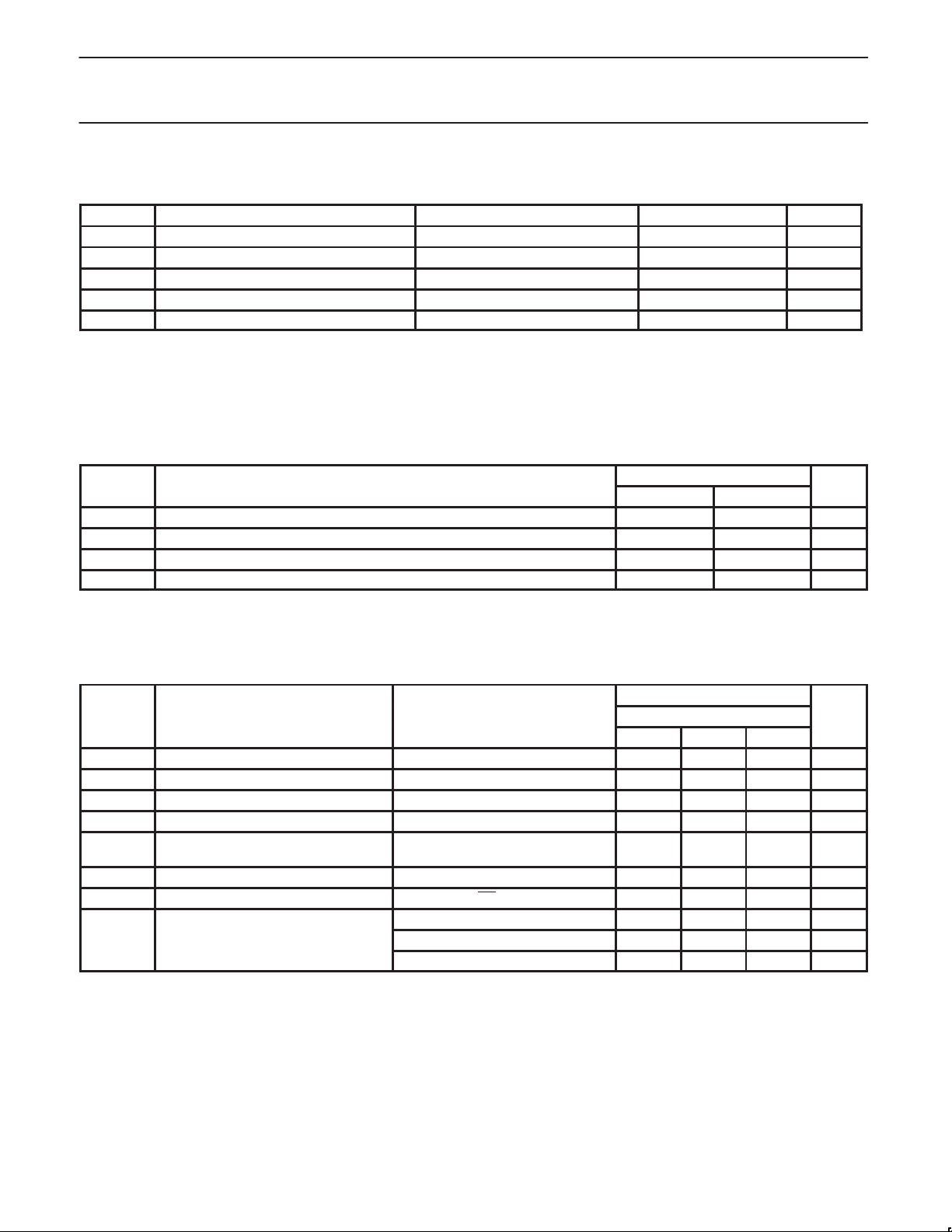

QUICK REFERENCE DATA

SYMBOL PARAMETER

t

PLH

t

PHL

C

IO(OFF)

I

CC

Propagation delay

A to B or B to A

Pin capacitance (OFF state) VO = 3 V or 0; OE = V

Quiescent supply current VCC = 5.5 V; IO = 0, VI = VCC or GND 3 µA

PIN CONFIGURATION

1

1OE

2

1A

3

1B

45

GND

8

7

6

SA00535

V

2OE

2B

2A

CC

PIN DESCRIPTION

PIN NUMBER SYMBOL NAME AND FUNCTION

1, 7 1OE, 2OE Output enable

2, 5 1A, 2A A port inputs

3, 6 1B, 2B B port outputs

4 GND Ground (0V)

8 V

CC

CONDITIONS

T

= 25 °C; GND = 0 V

amb

CL = 50 pF; VCC = +5.0 V ±0.5 V 0.25 (MAX) ns

CC

Positive supply voltage

TYPICAL UNIT

6.50 pF

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE ORDER CODE DWG NUMBER

8-pin plastic SO –40 to 85 °C CBTD3306D SOT96-1

8-pin plastic TSSOP –40 to 85 °C CBTD3306PW SOT530-1

Standard packing quantities and other packaging data is available at www.philipslogic.com/packaging.

LOGIC DIAGRAM (positive logic)

2

1A

1

1OE

5

2A

7

2OE

3

1B

6

2B

SA00534

FUNCTION TABLE

INPUT

OE

L A port = B port

H Disconnect

2001 Nov 08 853-2305 27313

2

Page 3

Philips Semiconductors Product data

SYMBOL

PARAMETER

UNIT

3

CBTD3306Dual bus switch with level shifting

ABSOLUTE MAXIMUM RATINGS

= –40 to +85 °C, unless otherwise specified.

T

amb

SYMBOL

V

CC

V

I

I

OUT

I

IK

T

stg

DC supply voltage –0.5 to +7.0 V

DC input voltage

DC output current 128 mA

Input diode current V

Storage temperature range –65 to +150 °C

PARAMETER CONDITIONS RATING UNIT

2

1

–0.5 to +7.0 V

< 0 –50 mA

I/O

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

3. The package thermal impedance is calculated in accordance with JESD 51.

RECOMMENDED OPERATING CONDITIONS

1

LIMITS

MIN MAX

V

T

CC

V

V

amb

DC supply voltage 4.5 5.5 V

High-level input voltage 2.0 — V

IH

Low-level Input voltage — 0.8 V

IL

Operating free-air temperature range –40 +85 °C

NOTE:

1. All unused control inputs of the device must be held at V

or GND to ensure proper device operation.

CC

DC ELECTRICAL CHARACTERISTICS

T

= –40 to +85 °C, unless otherwise specified.

amb

SYMBOL PARAMETER TEST CONDITIONS T

V

I

∆I

C

IO(OFF)

I

CC

V

C

Input clamp voltage VCC = 4.5 V; II = –18 mA — — –1.2 V

IK

Input leakage current VCC = 5.5 V; VI = GND or 5.5 V — — ±1 µA

I

Quiescent supply current VCC = 5.5 V; IO = 0, VI = VCC or GND — — 1.5 mA

Output high pass voltage See Figure 1 — — — V

P

VCC = 5.5 V, one input at 3.4 V,

Additional supply current per input pin

CC

Control pins capacitance VI= 3 V or 0 — 3.20 — pF

I

Port off capacitance VO = 3 V or 0; OE = V

2

other inputs at VCC or GND

CC

VCC = 4.5 V; VI = 0V; II = 64 mA — 3.6 5 Ω

r

on

On-resistance

VCC = 4.5 V; VI = 0 V; II = 30 mA — 3.6 5 Ω

VCC = 4.5 V; VI = 2.4 V; II = 15 mA — 17 35 Ω

NOTES:

1. All typical values are at V

2. This is the increase in supply current for each input that is at the specified TTL voltage level rather than V

= 5 V, T

CC

amb

= 25 °C.

3. Measured by the voltage drop between the A and the B terminals at the indicated current through the switch.

On-state resistance is determined by the lowest voltage of the two (A or B) terminals.

= –40 to +85 °C UNIT

amb

MIN TYP

— — 2.5 mA

— 6.50 — pF

CC

LIMITS

or GND

1

MAX

2001 Nov 08

3

Page 4

Philips Semiconductors Product data

(OUTPUT)

CBTD3306Dual bus switch with level shifting

AC CHARACTERISTICS

T

= –40 to +85 °C; CL = 50 pF

amb

SYMBOL PARAMETER FROM (INPUT)

t

pd

t

en

t

dis

Propagation delay

Output enable time

to High and Low level

Output disable time

from High and Low level

1

A or B B or A — 0.25 ns

OE A or B 1 5 ns

OE A or B 1 4.9 ns

TO

NOTE:

1. The propagation delay is the calculated RC time constant of the typical on-state resistance of the switch and the specified load capacitance,

when driven by an ideal voltage source (zero output impedance).

LIMITS

VCC = +5.0 V ±0.5 V

MIN MAX

UNIT

AC WAVEFORMS

VM = 1.5 V, VIN = GND to 3.0 V

INPUT

OUTPUT

1.5 V

t

PLH

1.5 V 1.5 V

Waveform 1. Input to Output Propagation Delays

Output Control

(Low-level

enabling )

Output

Waveform 1

S1 at 7 V

(see Note)

Output

Waveform 2

S1 at Open

(see Note)

Note:

Waveform 1 is for an output with internal conditions such that

the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that

the output is high except when disabled by the output control.

1.5 V 1.5 V

t

PZL

1.5 V

t

PZH

1.5 V

Waveform 2. 3-State Output Enable and Disable Times

NOTES:

1. t

2. t

3. t

PLZ

PZL

PLH

and t

and t

and t

are the same as t

PHZ

are the same as ten.

PZH

are the same as tpd.

PHL

dis

1.5 V

t

PHL

t

PLZ

V

t

PHZ

V

.

+ 0.3 V

OL

OH

– 0.3 V

SA00029

3 V

0 V

V

OH

V

OL

SA00028

3 V

0 V

3.5 V

V

OL

V

OH

0 V

TEST CIRCUIT AND WAVEFORMS

From Output

Under Test

C

= 50 pF

L

DEFINITIONS

= Load capacitance includes jig and probe capacitance;

C

L

see AC CHARACTERISTICS for value.

500 Ω

500 Ω

Load Circuit

TEST S1

t

pd

t

PLZ/tPZL

t

PHZ/tPZH

open

7 V

open

NOTES:

1. All input pulses are supplied by generators having the following

characteristics: PRR ≤ 10 MHz, Z

2. The outputs are measured one at a time with one transition per

= 50 Ω, tr ≤ 2.5 ns, tf ≤ 2.5 ns.

O

measurement.

7 V

S1

Open

GND

SA00012

2001 Nov 08

4

Page 5

Philips Semiconductors Product data

CBTD3306Dual bus switch with level shifting

Temp = 85 °C

3.8

3.6

3.4

V

P

3.2

3.0

2.8

2.6

2.4

2.2

4.4 4.6 4.8 5.0 5.2 5.4 5.6

V

– Supply Voltage

CC

3.6

3.4

3.2

V

P

3.0

2.8

100 µA

6 mA

12 mA

24 mA

3.8

3.6

3.4

V

P

3.2

3.0

2.8

2.6

2.4

2.2

4.4 4.6 4.8 5.0 5.2 5.4 5.6

Temp = 25 °C

Temp = 70 °C

– Supply Voltage

V

CC

100 µA

6 mA

12 mA

24 mA

100 µA

6 mA

12 mA

24 mA

2.6

2.4

2.2

4.4 4.6 4.8 5.0 5.2 5.4 5.6

3.6

3.4

3.2

3.0

V

P

2.8

2.6

2.4

2.2

2.0

4.4 4.6 4.8 5.0 5.2 5.4 5.6

Temp = 0 °C

– Supply Voltage

V

CC

Figure 1. Pass voltage values (Vin = VCC)

100 µA

6 mA

12 mA

24 mA

V

– Supply Voltage

CC

Temp = –40 °C

3.4

3.2

3.0

V

P

2.8

2.6

2.4

2.2

2.0

4.4 4.6 4.8 5.0 5.2 5.4 5.6

V

– Supply Voltage

CC

100 µA

6 mA

12 mA

24 mA

SW00895

2001 Nov 08

5

Page 6

Philips Semiconductors Product data

CBTD3306Dual bus switch with level shifting

TSSOP8: plastic thin shrink small outline; 8 leads; body width 4.4 mm SOT530-1

2001 Nov 08

6

Page 7

Philips Semiconductors Product data

CBTD3306Dual bus switch with level shifting

SO8: plastic small outline package; 8 leads; body width 3.9 mm SOT96-1

2001 Nov 08

7

Page 8

Philips Semiconductors Product data

CBTD3306Dual bus switch with level shifting

Data sheet status

Product

Data sheet status

Objective data

Preliminary data

Product data

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL

http://www.semiconductors.philips.com.

[1]

status

Development

Qualification

Production

[2]

Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or

at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended

periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips

Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or

modification.

Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can

reasonably be expected to result in personal injury . Philips Semiconductors customers using or selling these products for use in such applications

do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard

cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these

products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless

otherwise specified.

Contact information

For additional information please visit

http://www.semiconductors.philips.com . Fax: +31 40 27 24825

For sales offices addresses send e-mail to:

sales.addresses@www.semiconductors.philips.com.

Definitions

This data sheet contains data from the objective specification for product development.

Philips Semiconductors reserves the right to change the specification in any manner without notice.

This data sheet contains data from the preliminary specification. Supplementary data will be

published at a later date. Philips Semiconductors reserves the right to change the specification

without notice, in order to improve the design and supply the best possible product.

This data sheet contains data from the product specification. Philips Semiconductors reserves the

right to make changes at any time in order to improve the design, manufacturing and supply.

Changes will be communicated according to the Customer Product/Process Change Notification

(CPCN) procedure SNW-SQ-650A.

Koninklijke Philips Electronics N.V. 2001

All rights reserved. Printed in U.S.A.

Date of release: 11-01

Document order number: 9397 750 09116

2001 Nov 08

8

Loading...

Loading...