Philips BUK856-400IZ Datasheet

Philips Semiconductors Product specification

Insulated Gate Bipolar Transistor BUK856-400 IZ

Protected Logic-Level IGBT

GENERAL DESCRIPTION QUICK REFERENCE DATA

Protected N-channel logic-level SYMBOL PARAMETER MIN. TYP. MAX. UNIT

insulated gate bipolar power

transistor in a plastic envelope, V

intended for automotive ignition V

applications. The device has I

built-in zener diodes providing P

active collector voltage clamping E

(CL)CER

CEsat

C

tot

CERS

and ESD protection up to 2 kV.

PINNING - TO220AB PIN CONFIGURATION SYMBOL

Collector-emitter clamp voltage 350 400 500 V

Collector-emitter on-state voltage 2.2 V

Collector current (DC) 20 A

Total power dissipation 100 W

Clamped energy dissipation 300 mJ

PIN DESCRIPTION

tab

c

1 gate

2 collector

3 emitter

tab collector

123

g

e

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

V

±V

I

C

I

C

I

CM

I

CLM

E

E

E

P

T

T

CE

CE

GE

CERS

CERR

ECR

tot

stg

j

1

1

Collecter-emitter voltage tp ≤ 500 µs - 500 V

Collector-emitter voltage Continuous -20 50 V

Gate-emitter voltage - - 12 V

Collector current (DC) Tmb = 100 ˚C - 10 A

Collector current (DC) Tmb = 25 ˚C - 20 A

Collector current (pulsed peak value, Tmb = 25 ˚C; tp ≤ 10 ms; - 25 A

on-state) VCE ≤ 15 V

Collector current (clamped inductive 1 kΩ ≤ RG ≤ 10 kΩ -10A

load)

Clamped turn-off energy Tmb = 25 ˚C; IC = 10 A; RG = 1 kΩ; - 300 mJ

(non-repetitive) see Figs. 23,24

Clamped turn-off energy (repetitive) Tmb = 100 ˚C; IC = 8 A; RG = 1 kΩ; - 125 mJ

f = 50 Hz

Reverse avalanche energy IE = 1 A; f = 50 Hz - 5 mJ

(repetitive)

Total power dissipation Tmb = 25 ˚C - 125 W

Storage temperature - -55 150 ˚C

Operating Junction Temperature - -40 150 ˚C

ESD LIMITING VALUE

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

C

1 This applies to short-term operation in ignition circuits with open-secondary ignition coil.

December 1996 1 Rev. 1.200

Electrostatic discharge capacitor Human body model - 2 kV

voltage (100 pF, 1.5 kΩ)

Philips Semiconductors Product specification

Insulated Gate Bipolar Transistor BUK856-400 IZ

Protected Logic-Level IGBT

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS TYP. MAX. UNIT

R

R

th j-mb

th j-a

Junction to mounting base - 1.0 K/W

Junction to ambient In free air 60 - K/W

STATIC CHARACTERISTICS

Tmb = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

(BR)CG

V

(BR)EC

±V

V

GE(TO)

V

GE(TO)

I

CES

I

CES

I

EC

I

EC

I

GES

V

CEsat

(BR)GES

Collector-gate zener 2 mA ≤ -IG ≤ 5 mA; -40 ≤ Tj ≤150˚C 350 400 500 V

breakdown voltage

Reverse collector-emitter IE = 10 mA 20 30 50 V

breakdown voltage

Gate-emitter breakdown IG = ± 1 mA 12 16 20 V

voltage

Gate threshold voltage VCE = VGE; IC = 1 mA 1 1.5 2 V

Gate threshold voltage VCE = VGE; IC = 1 mA; 0.6 - 2.4 V

-40 ≤ Tj ≤150˚C

Zero gate voltage collector VCE = 50 V; VGE = 0 V; Tj = 25 ˚C - 0.01 10 µA

current

Zero gate voltage collector Tj = 125 ˚C - 0.01 1 mA

current

Reverse collector current VCE = -20 V - 0.2 5 mA

Reverse collector current VCE = -20 V; Tj = 125˚C - 2 20 mA

Gate emitter leakage current VGE = ±6 V - 0.1 1 µA

Tj = 150˚C - 5 100 µA

Collector-emitter on-state VGE = 4.5 V; IC = 8 A - 1.2 2.2 V

voltage VGE = 3.5 V; IC = 6 A; - 1.2 2.2 V

-40 ≤ Tj ≤150˚C

DYNAMIC CHARACTERISTICS

Tmb = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

(CL)CER

g

fe

C

ies

C

oes

C

res

t

d off

t

f

t

c

E

off

December 1996 2 Rev. 1.200

Collector-emitter clamp voltage RG = 1 kΩ; IC = 10 A; 350 400 500 V

(peak value) -40 ≤ Tj ≤150˚C; Inductive load; see

Figs. 23,24

Forward transconductance VCE = 15 V; IC = 4 A 5.5 15 20 S

Input capacitance VGE = 0 V; VCE = 25 V; f = 1 MHz - 940 1200 pF

Output capacitance - 95 130 pF

Feedback capacitance - 30 50 pF

Turn-off delay time IC = 8 A; VCL = 300 V; RG = 1 kΩ; - 13 18 µs

Fall time VGE = 5 V; Tj = 125˚C; - 6 10 µs

Crossover Time Inductive load; see Figs. 20,21 - 12 - µs

Turn-off Energy loss - 13 - mJ

Philips Semiconductors Product specification

Insulated Gate Bipolar Transistor BUK856-400 IZ

Protected Logic-Level IGBT

Zth(j-mb) / (K/W)

1E+01

1E+00

1E-01

1E-02

1E-03

D=

0.5

0.2

0.1

0.05

0.02

t

P

D

0

1E-07 1E-05 1E-03 1E-01 1E+01

t / s

D =

p

T

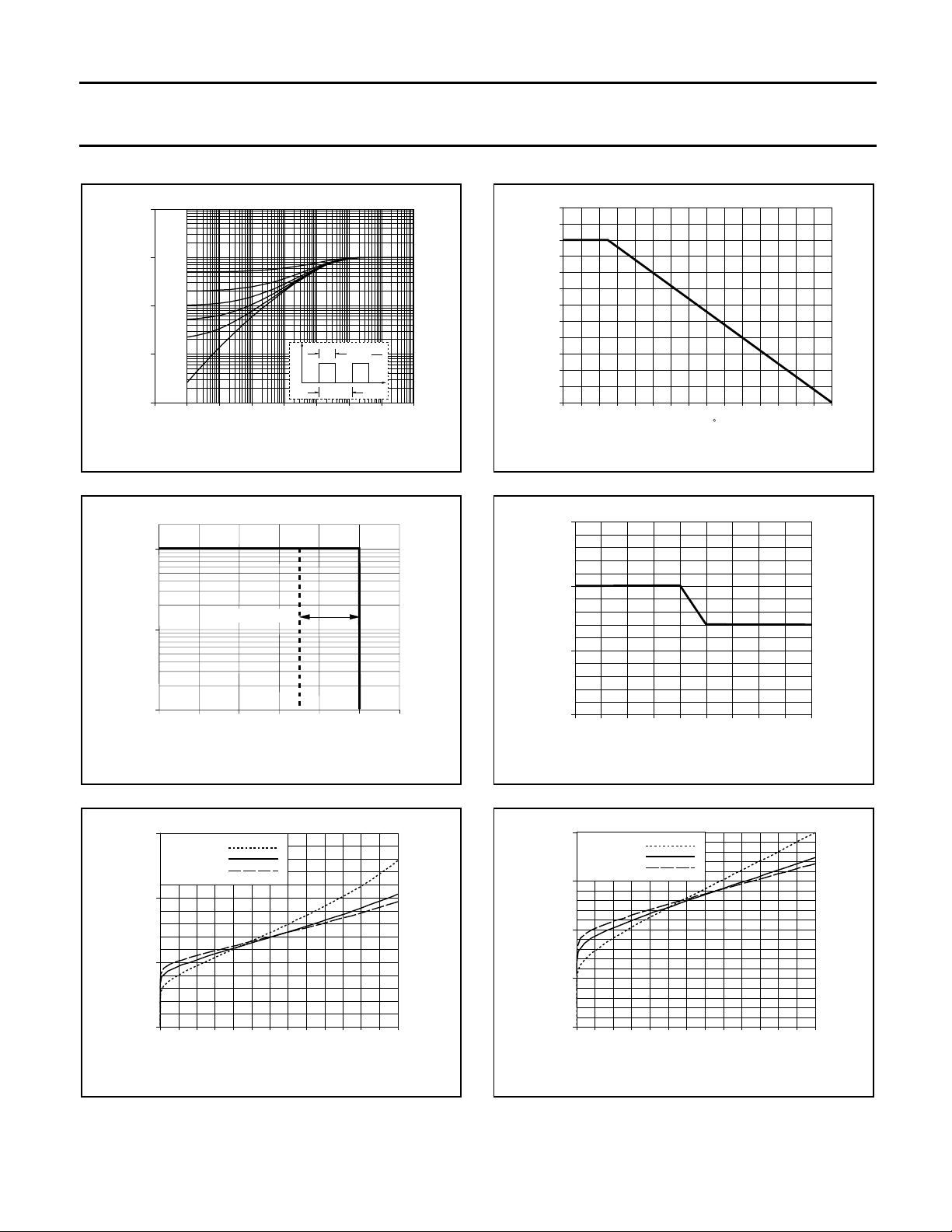

Fig.1. Transient thermal impedance

Z

= f(t) ; parameter D = tp/T

th j-mb

IC / A

10

Self-clamped

1

I

CLM

BUK8Y6-400IZ

PD%

120

110

100

90

80

70

60

50

t

p

T

t

40

30

20

10

0

0 20 40 60 80 100 120 140

Normalised Power Derating

Tmb / C

Fig.4. Normalised power dissipation.

PD% = 100.PD/P

ICLM / A BUK8Y6-400IZ

15

10

5

D 25˚C

= f(Tmb)

0.1

0 200 400 600

VCE / V

Fig.2. Turn-off Safe Operating Area

conditions: Tj ≤ T

VCE / V

3

2

1

0

0 4 8 12 16 20 24

Tj / C =

150

-40

25

jmax.

IC / A

; RG ≥ 1

PMG35A

Fig.3. Typical On-state Voltage

V

= f(IC); parameter Tj; conditions: VGE = 3.5 V

CEsat

kΩ

0

0 50 100 150 200

Fig.5. Derating of I

conditions: VCE ≤ 500 V; Tj ≤ T

VCE / V

2

Tj / C =

1.5

1

0.5

0

0 4 8 12 16 20 24

150

-40

25

dVCE/dt (V/us)

with turn-off dVCE/dt

CLM

IC / A

Fig.6. Typical On-state Voltage

V

= f(IC); parameter Tj; conditions: VGE = 5 V

CEsat

jmax.

PMG35A

December 1996 3 Rev. 1.200

Loading...

Loading...