Philips buk107 50dl hg DATASHEETS

DISCRETE SEMICONDUCTORS

DATA SH EET

BUK107-50DL

PowerMOS transistor

Logic level TOPFET

Product specification

Supersedes data of September 1994

File under Discrete Semiconductors, SC13a

March 1997

Philips Semiconductors Product specification

PowerMOS transistor

BUK107-50DL

Logic level TOPFET

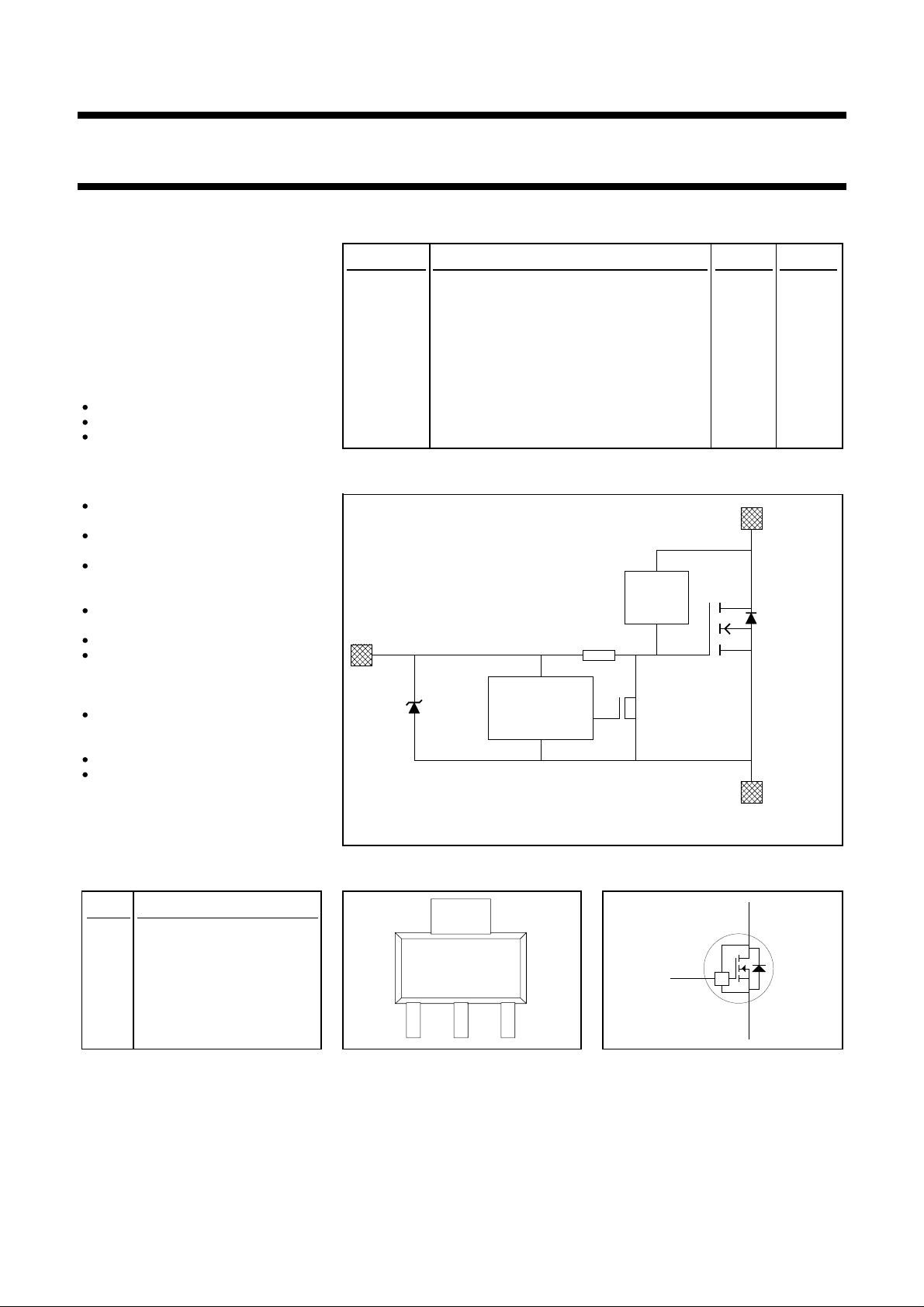

DESCRIPTION QUICK REFERENCE DATA

Monolithic overload protected logic SYMBOL PARAMETER MAX. UNIT level power MOSFET in a surface mount plastic envelope, intended as V a general purpose switch for automotive systems and other I applications.

DS

D

P

D

APPLICATIONS

T

General controller for driving

lamps R

small motors

j

DS(ON)

solenoids

FEATURES FUNCTIONAL BLOCK DIAGRAM

Vertical power DMOS output

stage

Overload protected up to

85˚C ambient

Overload protection by current

limiting and overtemperature

sensing

Latched overload protection

reset by input

5 V logic compatible input level

Control of power MOSFET

and supply of overload

protection circuits

derived from input

Low operating input current

permits direct drive by

micro-controller

ESD protection on all pins

Overvoltage clamping for turn

off of inductive loads

INPUT

Continuous drain source voltage 50 V

Continuous drain current 0.7 A

Total power dissipation 1.8 W

Continuous junction temperature 150 ˚C

Drain-source on-state resistance 200 mΩ

DRAIN

O/V

CLAMP

RIG

LOGIC AND

PROTECTION

POWER

MOSFET

SOURCE

Fig.1. Elements of the TOPFET.

PINNING - SOT223 PIN CONFIGURATION SYMBOL

PIN DESCRIPTION

1 input

2 drain

3 source

4 drain (tab)

March 1997 2 Rev 1.200

1

4

23

TOPFET

I

D

P

S

Philips Semiconductors Product specification

PowerMOS transistor

BUK107-50DL

Logic level TOPFET

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

I

I

I

P

T

T

DS

D

I

IRM

D

stg

j

Continuous drain source voltage

Continuous drain current

2

Continuous input current clamping - 3 mA

Non-repetitive peak input current tp ≤ 1 ms - 10 mA

Total power dissipation T

Storage temperature - -55 150 ˚C

Continuous junction temperature normal operation

ESD LIMITING VALUE

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

C

Electrostatic discharge capacitor Human body model; - 2 kV

voltage C = 250 pF; R = 1.5 kΩ

OVERVOLTAGE CLAMPING LIMITING VALUES

At a drain source voltage above 50 V the power MOSFET is actively turned on to clamp overvoltage transients.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

E

DSM

E

DRM

Non-repetitive clamping energy Tb ≤ 25 ˚C; IDM < I

Repetitive clamping energy Tb ≤ 75 ˚C; IDM = 50 mA; - 4 mJ

1

- - 50 V

- - self limiting A

= 25 ˚C - 1.8 W

amb

3

- 150 ˚C

; - 100 mJ

D(lim)

inductive load

f = 250 Hz

OVERLOAD PROTECTION LIMITING VALUES

With the protection supply provided via the input pin, TOPFET can protect itself from short circuit loads.

Overload protection operates by means of drain current limiting and activating the overtemperature protection.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

DDP

Protected drain source supply voltage VIS = 5 V - 35 V

V

= 4 V - 16 V

IS

OVERLOAD PROTECTION CHARACTERISTICS

TOPFET switches off to protect itself when there is an overload fault condition.

It remains latched off until reset by the input.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Overload protection

I

D(lim)

T

j(TO)

1 Prior to the onset of overvoltage clamping. For voltages above this value, safe operation is limited by the overvoltage clamping energy.

2 Refer to OVERLOAD PROTECTION CHARACTERISTICS.

3 Not in an overload condition with drain current limiting.

Drain current limiting VIS = 5 V 0.7 1.1 1.5 A

Overtemperature protection only in drain current limiting

Threshold junction temperature VIS = 5 V 100 130 160 ˚C

March 1997 3 Rev 1.200

Philips Semiconductors Product specification

PowerMOS transistor

BUK107-50DL

Logic level TOPFET

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Thermal resistance

R

th j-sp

R

th j-b

R

th j-a

STATIC CHARACTERISTICS

Tb = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

(CL)DSS

V

(CL)DSS

I

DSS

I

DSS

I

DSS

R

DS(ON)

Junction to solder point - 12 18 K/W

Junction to board

1

Mounted on any PCB - 40 - K/W

Junction to ambient Mounted on PCB of fig. 19 - - 70 K/W

Drain-source clamping voltage VIS = 0 V; ID = 10 mA 50 55 - V

Drain-source clamping voltage VIS = 0 V; IDM = 200 mA; - 56 70 V

≤ 300 µs; δ ≤ 0.01

t

p

Off-state drain current VDS = 45 V; VIS = 0 V - 0.5 2 µA

Off-state drain current VDS = 50 V; VIS = 0 V - 1 20 µA

Off-state drain current VDS = 40 V; VIS = 0 V; Tj = 100 ˚C - 10 100 µA

Drain-source on-state VIS = 5 V; IDM = 100 mA; - 150 200 mΩ

resistance

2

tp ≤ 300 µs; δ ≤ 0.01

INPUT CHARACTERISTICS

Tb = 25 ˚C unless otherwise specified. The supply for the logic and overload protection is taken from the input.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

I

IS

I

ISL

V

V

R

IS(TO)

ISR

(CL)IS

IG

Input threshold voltage VDS = 5 V; ID = 1 mA 1.7 2.2 2.7 V

Input supply current normal operation; VIS = 5 V - 330 450 µA

= 4 V - 170 270 µA

V

IS

Input supply current protection latched; VIS = 5 V - 500 650 µA

V

= 3.5 V - 250 400 µA

Protection latch reset voltage

3

IS

1 2.2 3.5 V

Input clamping voltage II = 1.5 mA 6 7.5 - V

Input series resistance to gate of power MOSFET - 33 - kΩ

SWITCHING CHARACTERISTICS

T

= 25 ˚C; resistive load RL = 50 Ω; adjust VDD to obtain ID = 250 mA; refer to test circuit and waveforms

amb

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

t

t

t

t

d on

r

d off

f

Turn-on delay time VIS = 0 V to VIS = 5 V - 8 - µs

Rise time - 30 - µs

Turn-off delay time VIS = 5 V to VIS = 0 V - 3 - µs

Fall time - 6 - µs

1 Temperature measured 1.3 mm from tab.

2 Continuous input voltage. The specified pulse width is for the drain current.

3 The input voltage below which the overload protection circuits will be reset.

March 1997 4 Rev 1.200

Loading...

Loading...