Philips BUK104-50S, BUK104-50LP Datasheet

Philips Semiconductors Product specification

PowerMOS transistor BUK104-50L/S

Logic level TOPFET BUK104-50LP/SP

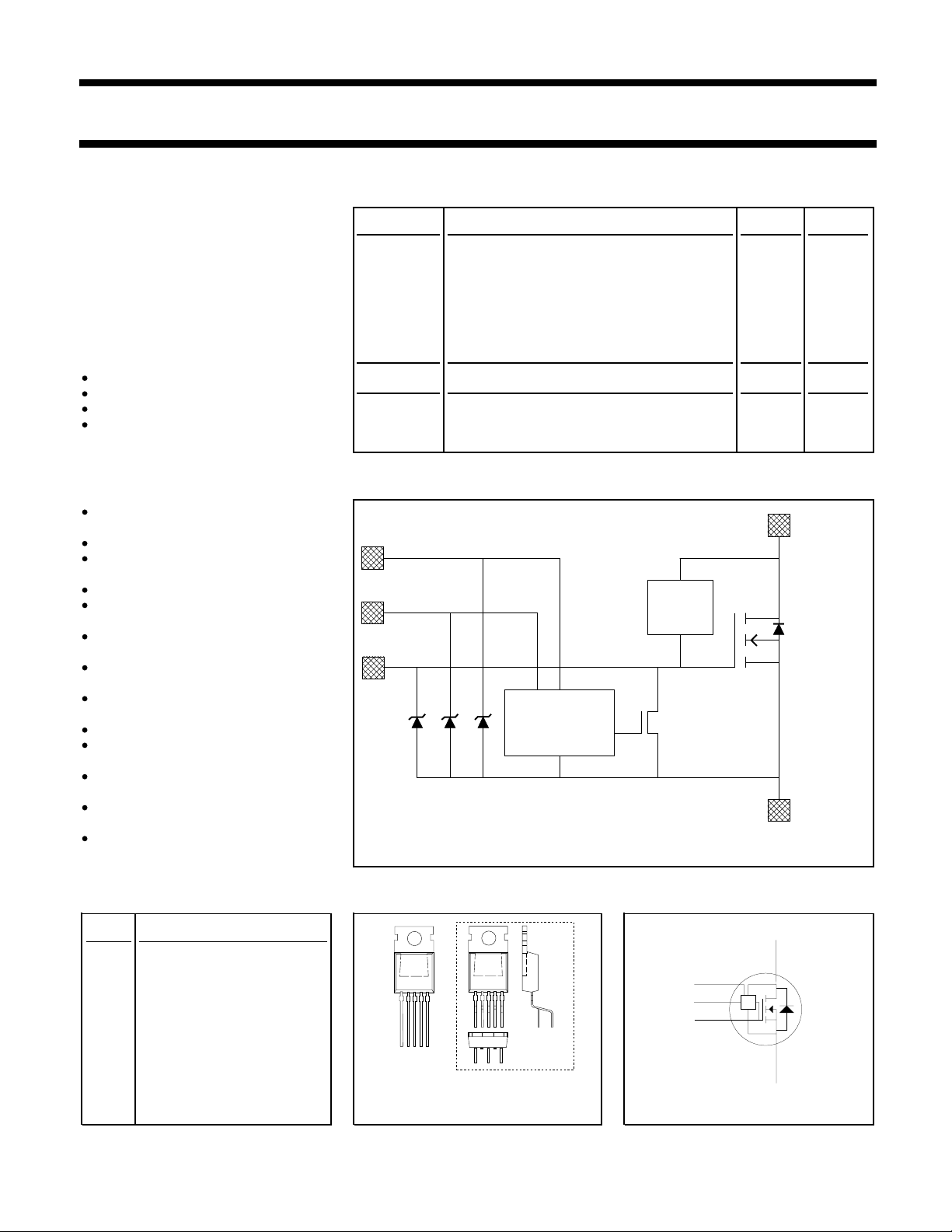

DESCRIPTION QUICK REFERENCE DATA

Monolithic temperature and SYMBOL PARAMETER MAX. UNIT

overload protected logic level power

MOSFET in a 5 pin plastic V

envelope, intended as a general I

purpose switch for automotive P

systems and other applications. T

D

R

DS

tot

j

DS(ON)

APPLICATIONS V

General controller for driving

lamps SYMBOL PARAMETER NOM. UNIT

motors

solenoids V

heaters BUK104-50L 5V

PSN

FEATURES FUNCTIONAL BLOCK DIAGRAM

Vertical power DMOS output

stage

Low on-state resistance

Logic and protection supply

from separate pin

Low operating supply current

Overload protection against

over temperature

Overload protection against

short circuit load

Latched overload protection

reset by protection supply

Protection circuit condition

indicated by flag pin

5 V logic compatible input level

Separate input pin

for higher frequency drive

ESD protection on input, flag

and protection supply pins

Over voltage clamping for turn

off of inductive loads

Both linear and switching

operation are possible Fig.1. Elements of the TOPFET.

PROTECTION SUPPLY

FLAG

INPUT

Continuous drain source voltage 50 V

Continuous drain current 15 A

Total power dissipation 40 W

Continuous junction temperature 150 ˚C

Drain-source on-state resistance

= 5 V 125 mΩ

IS

VIS = 7 V 100 mΩ

Protection supply voltage

BUK104-50S 10 V

DRAIN

O/V

CLAMP

LOGIC AND

PROTECTION

POWER

MOSFET

SOURCE

PINNING - SOT263 PIN CONFIGURATION SYMBOL

PIN DESCRIPTION

1 input

2 flag

3 drain

4 protection supply

5 source

tab drain

January 1993 1 Rev 1.200

tab

TOPFET

12345

P

F

leadform

263-01

P

I

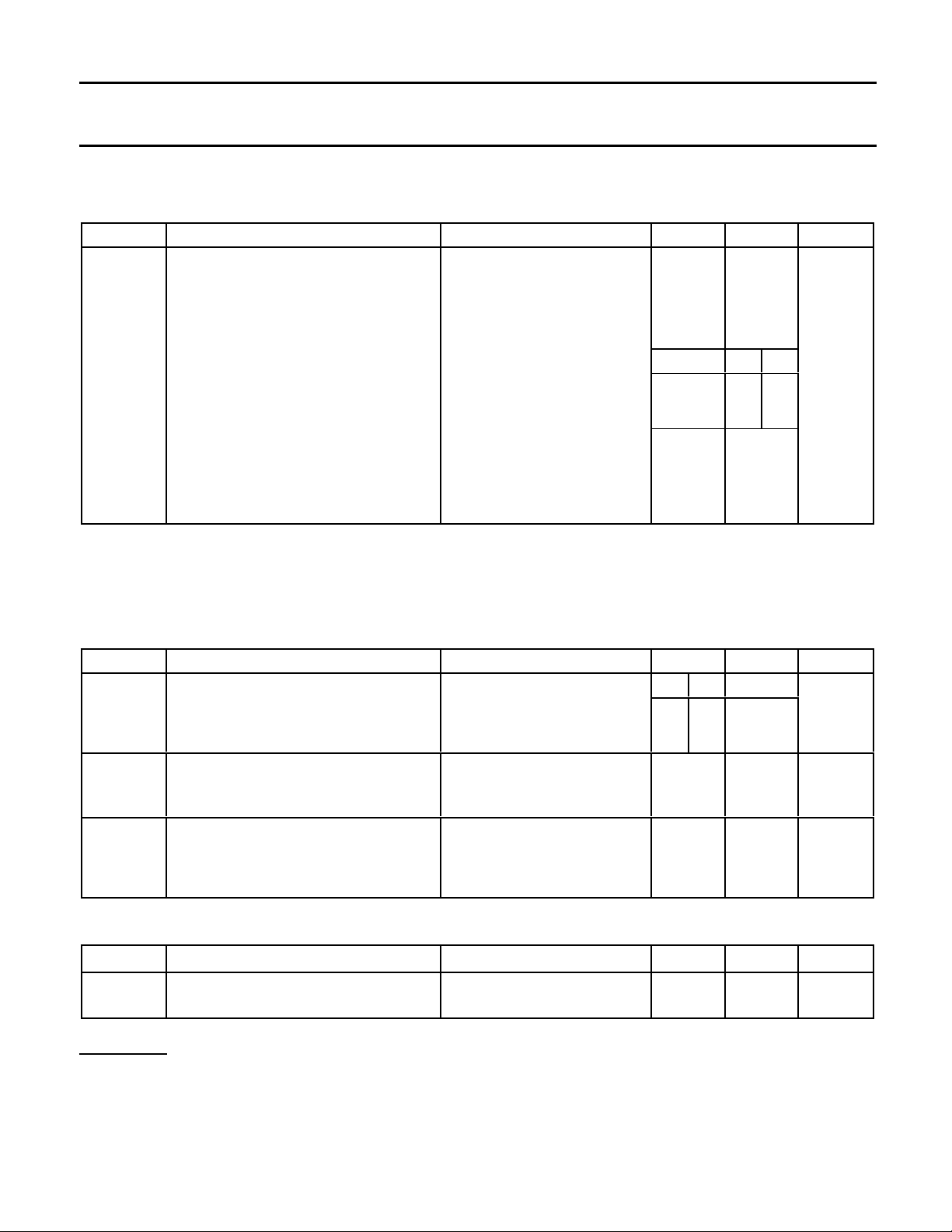

Fig. 2. Type numbers ending with

suffix P refer to leadform 263-01. Fig. 3.

D

S

Philips Semiconductors Product specification

PowerMOS transistor BUK104-50L/S

Logic level TOPFET BUK104-50LP/SP

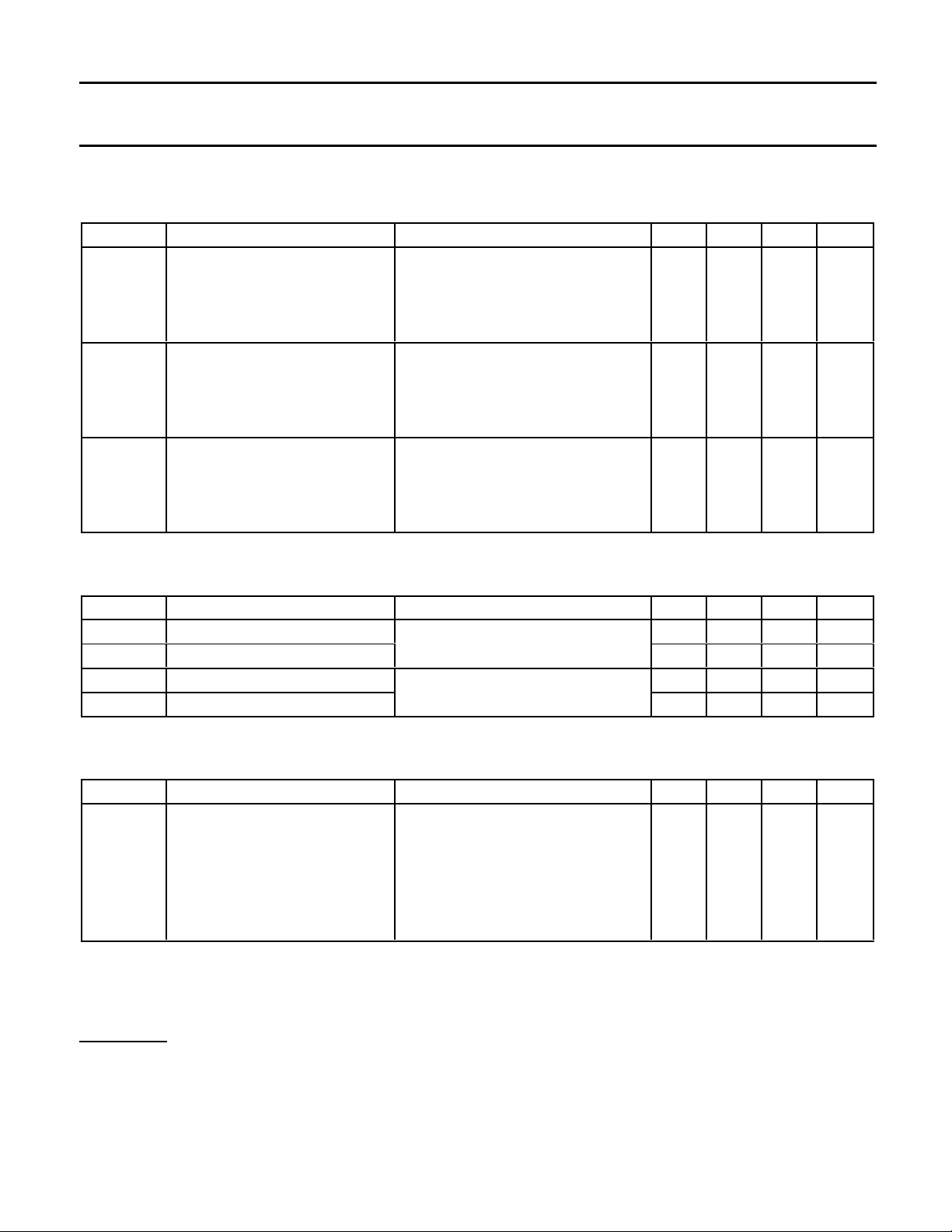

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum Rating System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

V

V

V

I

D

I

D

I

DRM

P

T

T

T

DSS

IS

FS

PS

tot

stg

j

sold

Voltages

Continuous off-state drain source VIS = 0 V - 50 V

voltage

1

Continuous input voltage - 0 11 V

Continuous flag voltage - 0 11 V

Continuous supply voltage - 0 11 V

Currents VIS = - 7 5 V

Continuous drain current T

Continuous drain current T

Repetitive peak on-state drain current Tmb ≤ 25 ˚C - 60 54 A

25 ˚C - 15 13 A

mb ≤

100 ˚C - 9.5 8.5 A

mb ≤

Thermal

Total power dissipation Tmb = 25 ˚C - 40 W

Storage temperature - -55 150 ˚C

Junction temperature

2

continuous - 150 ˚C

Lead temperature during soldering - 250 ˚C

OVERLOAD PROTECTION LIMITING VALUES

With the protection supply An n-MOS transistor turns on For internal overload protection to

connected, TOPFET can protect between the input and source to remain latched while the control

itself from two types of overload - quickly discharge the power circuit is high, external series input

over temperature and short circuit MOSFET gate capacitance. resistance must be provided. Refer

load. to INPUT CHARACTERISTICS.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VIS =75 - V

V

PSP

Protection supply voltage

3

for valid protection

BUK104-50L 4.4 4 - V

BUK104-50S 5.4 5 - V

V

DDP(T)

V

DDP(P)

P

DSM

Over temperature protection VPS = V

Protected drain source supply voltage VIS = 10 V; RI ≥ 2 kΩ -50V

V

Short circuit load protection VPS = V

Protected drain source supply voltage4VIS = 10 V; RI ≥ 2 kΩ -25V

V

Instantaneous overload dissipation - 0.8 kW

PSN

= 5 V; RI ≥ 1 kΩ -50V

IS

; L ≤ 10 µH

PSN

= 5 V; RI ≥ 1 kΩ -45V

IS

ESD LIMITING VALUE

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

C

Electrostatic discharge capacitor Human body model; - 2 kV

voltage C = 250 pF; R = 1.5 kΩ

1 Prior to the onset of overvoltage clamping. For voltages above this value, safe operation is limited by the overvoltage clamping energy.

2 A higher Tj is allowed as an overload condition but at the threshold T

3 The minimum supply voltage required for correct operation of the overload protection circuits.

4 The device is able to self-protect against a short circuit load providing the drain-source supply voltage does not exceed V

For further information, refer to OVERLOAD PROTECTION CHARACTERISTICS.

the over temperature trip operates to protect the switch.

j(TO)

DDP(P)

maximum.

January 1993 2 Rev 1.200

Philips Semiconductors Product specification

PowerMOS transistor BUK104-50L/S

Logic level TOPFET BUK104-50LP/SP

OVERVOLTAGE CLAMPING LIMITING VALUES

At a drain source voltage above 50 V the power MOSFET is actively turned on to clamp overvoltage transients.

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

I

DRRM

E

DSM

E

DRM

Repetitive peak clamping drain current RIS ≥ 100 Ω

Non-repetitive inductive turn-off IDM = 15 A; RIS ≥ 100 Ω - 200 mJ

energy

2

Repetitive inductive turn-off energy RIS ≥ 100 Ω; Tmb ≤ 95 ˚C; - 20 mJ

IDM = 4 A; VDD ≤ 20 V;

f = 250 Hz

I

DIRM

Repetitive peak drain to input current3RIS = 0 Ω; tp ≤ 1 ms - 50 mA

REVERSE DIODE LIMITING VALUE

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

I

S

Continuous forward current Tmb = 25 ˚C; - 15 A

VIS = VPS = VFS = 0 V

THERMAL CHARACTERISTICS

1

-15A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Thermal resistance

R

R

th j-mb

th j-a

Junction to mounting base - - 2.5 3.1 K/W

Junction to ambient in free air - 60 - K/W

STATIC CHARACTERISTICS

Tmb = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

(CL)DSR

V

(CL)DSR

I

DSS

I

DSR

I

DSR

R

DS(ON)

Drain-source clamping voltage RIS = 100 Ω; ID = 10 mA 50 - 65 V

Drain-source clamping voltage RIS = 100 Ω; IDM = 1 A; tp ≤ 300 µs; 50 - 70 V

δ ≤ 0.01

Zero input voltage drain current VDS = 12 V; VIS = 0 V - 0.5 10 µA

Drain source leakage current VDS = 50 V; RIS = 100 Ω;-120µA

Drain source leakage current VDS = 40 V; RIS = 100 Ω;

Tj = 125 ˚C - 10 100 µA

Drain-source on-state IDM = 7.5 A; VIS = 7 V - 75 100 mΩ

resistance tp ≤ 300 µs; δ ≤ 0.01 VIS = 5 V - 95 125 mΩ

1 The input pin must be connected to the source pin by a specified external resistance to allow the power MOSFET gate source voltage to

2 While the protection supply voltage is connected, during overvoltage clamping it is possible that the overload protection may operate at

3 Shorting the input to source with low resistance inhibits the internal overvoltage protection by preventing the power MOSFET gate source

become sufficiently positive for active clamping. Refer to INPUT CHARACTERISTICS.

energies close to the limiting value. Refer to OVERLOAD PROTECTION CHARACTERISTICS.

voltage becoming positive.

January 1993 3 Rev 1.200

Philips Semiconductors Product specification

PowerMOS transistor BUK104-50L/S

Logic level TOPFET BUK104-50LP/SP

OVERLOAD PROTECTION CHARACTERISTICS

With adequate protection supply Provided there is adequate input Refer also to OVERLOAD

voltage TOPFET detects when one series resistance it switches off PROTECTION LIMITING VALUES

of the overload thresholds is and remains latched off until reset and INPUT CHARACTERISTICS.

exceeded. by the protection supply pin.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Short circuit load protection1VPS = V

RI ≥ 2 kΩ

E

t

d sc

DS(TO)

Overload threshold energy VDD = 13 V; VIS = 10 V - 150 - mJ

Response time VDD = 13 V; VIS = 10 V - 375 - µs

Over temperature protection VPS = V

T

j(TO)

Threshold junction temperature from ID ≥ 0.65 A

TRANSFER CHARACTERISTICS

Tmb = 25 ˚C

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

g

fs

I

D

Forward transconductance VDS = 10 V; IDM = 7.5 A tp ≤ 300 µs; 5 9 - S

δ ≤ 0.01

Drain current

4

VDS = 13 V; VIS = 5 V - 25 - A

2

; Tmb = 25 ˚C; L ≤ 10 µH;

PSN

; RI ≥ 2 kΩ

PSN

3

VIS = 10 V 40 - A

150 - - ˚C

PROTECTION SUPPLY CHARACTERISTICS

Tmb = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Protection supply

IPS, Protection supply current normal operation or

I

PSL

protection latched

BUK104-50L VPS = 5 V - 0.2 0.35 mA

V

PSR

Protection reset voltage

5

BUK104-50S VPS = 10 V - 0.4 1.0 mA

1.5 2.5 3.5 V

Tj = 150 ˚C 1.0 - - V

V

(CL)PS

Protection clamp voltage IP = 1.35 mA 11 13 - V

REVERSE DIODE CHARACTERISTICS

Tmb = 25 ˚C

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

SDS

t

rr

1 The short circuit load protection is able to save the device providing the instantaneous on-state dissipation is less than the limiting value for

2 At the appropriate nominal protection supply voltage for each type. Refer to QUICK REFERENCE DATA.

3 The over temperature protection feature requires a minimum on-state drain source voltage for correct operation. The specified minimum I

4 During overload condition. Refer also to OVERLOAD PROTECTION LIMITING VALUES and CHARACTERISTICS.

5 The supply voltage below which the overload protection circuits will be reset.

6 The reverse diode of this type is not intended for applications requiring fast reverse recovery.

Forward voltage IS = 15 A; VIS = VPS = VFS = 0 V; - 1.0 1.5 V

tp = 300 µs

Reverse recovery time not applicable

P

, which is always the case when VDS is less than V

DSM

ensures this condition.

maximum.

DSP

6

----

D

January 1993 4 Rev 1.200

Philips Semiconductors Product specification

PowerMOS transistor BUK104-50L/S

Logic level TOPFET BUK104-50LP/SP

INPUT CHARACTERISTICS

Tmb = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Normal operation

V

I

IS

V

R

R

R

IS(TO)

(CL)IS

ISL

IS

I

Input threshold voltage VDS = 5 V; ID = 1 mA 1.0 1.5 2.0 V

Tmb = 150 ˚C 0.5 - - V

Input current VIS = 10 V - 10 100 nA

Input clamp voltage II = 1 mA 11 13 - V

Overload protection latched

Input resistance

1

VPS = 5 V II = 5 mA; - 55 - Ω

Tmb = 150 ˚C - 95 - Ω

VPS = 10 V II = 5 mA; - 35 - Ω

Tmb = 150 ˚C - 60 - Ω

Application information

External input resistances for (see figure 29)

internal overvoltage clamping2RI = ∞ Ω;V

internal overload protection

3

RIS = ∞ Ω;V

> 30 V 100 - - Ω

DS

= 5 V 1 - - kΩ

II

VII = 10 V 2 - - kΩ

SWITCHING CHARACTERISTICS

Tmb = 25 ˚C; RI = 50 Ω; RIS = 50 Ω (see figure 29); resistive load RL = 10 Ω. For waveforms see figure 28.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

t

t

t

t

d on

r

d off

f

Turn-on delay time VDD = 15 V; VIS: 0 V ⇒ 10 V - 8 - ns

Rise time - 13 - ns

Turn-off delay time VDD = 15 V; VIS: 10 V ⇒ 0 V - 100 - ns

Fall time - 45 - ns

CAPACITANCES

Tmb = 25 ˚C; f = 1 MHz

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

C

iss

C

oss

C

rss

C

pso

C

fso

Input capacitance VDS = 25 V; VIS = 0 V - 415 600 pF

Output capacitance VDS = 25 V; VIS = 0 V - 275 400 pF

Reverse transfer capacitance VDS = 25 V; VIS = 0 V - 55 80 pF

Protection supply pin VPS = 10 V - 30 - pF

capacitance

Flag pin capacitance VFS = 10 V; VPS = 0 V - 20 - pF

1 The resistance of the internal transistor which discharges the power MOSFET gate capacitance when overload protection operates.

The external drive circuit should be such that the input voltage does not exceed V

operated. Refer also to figure for latched input characteristics.

2 Applications using a lower value for RIS would require external overvoltage protection.

3 For applications requiring a lower value for RI, an external overload protection strategy is possible using the flag pin to ‘tell’ the control circuit to

switch off the input.

minimum when the overload protection has

IS(TO)

January 1993 5 Rev 1.200

Loading...

Loading...