Philips BSP92 Datasheet

DISCRETE SEMICONDUCTORS

DATA SH EET

BSP92

P-channel enhancement mode

vertical D-MOS transistor

Product specification

File under Discrete Semiconductors, SC13b

April 1995

Philips Semiconductors Product specification

P-channel enhancement mode vertical

D-MOS transistor

FEATURES

• Low threshold voltage V

GS(th)

• Direct interface to C-MOS, TTL,

etc.

• High-speed switching

• No secondary breakdown.

DESCRIPTION

P-channel enhancement mode

vertical D-MOS transistor in a

SOT223 envelope, intended for use

as a surface-mounted device in line

current interruptor in telephone sets

and for application in relay, high

speed and line transformer drivers.

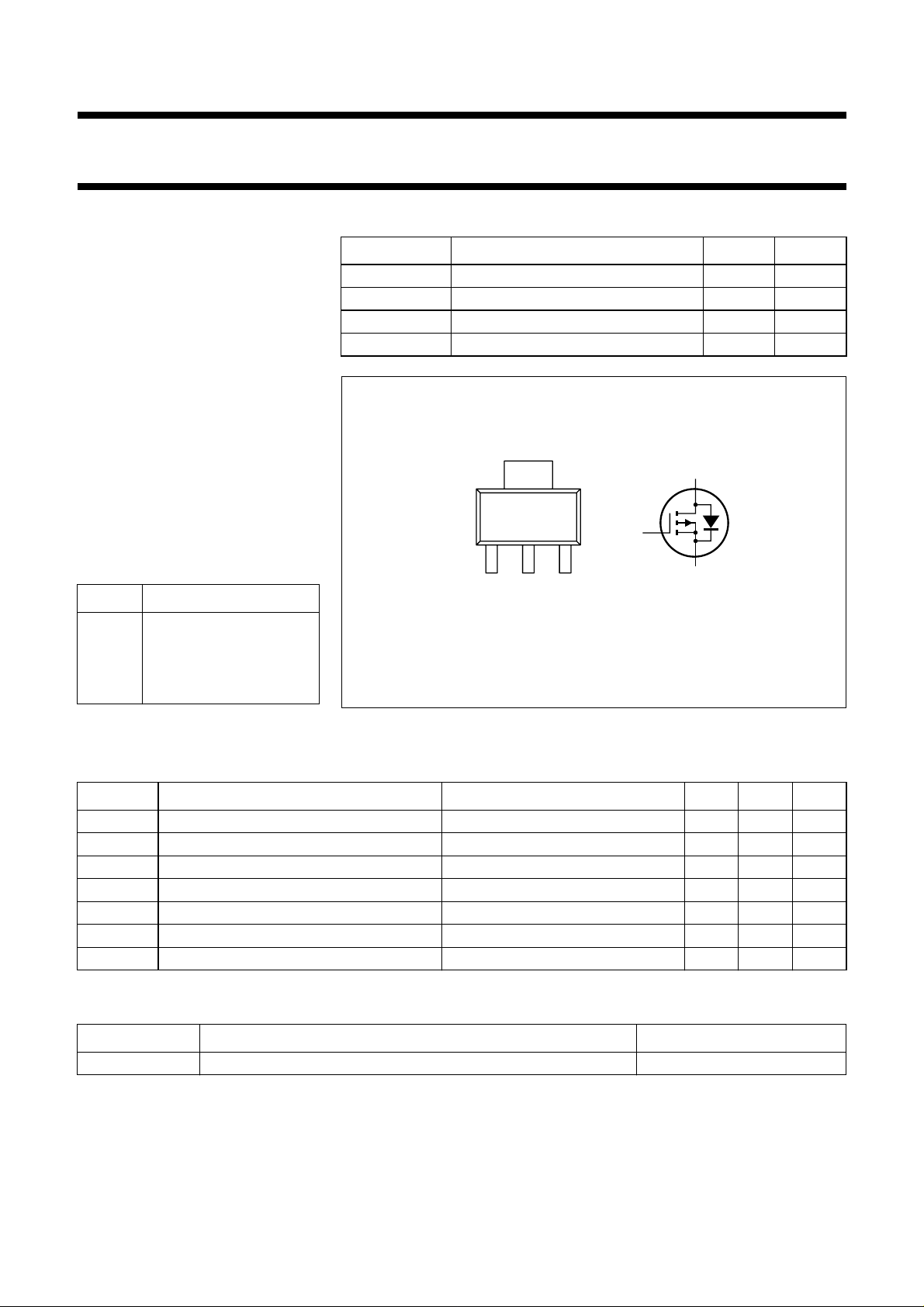

PINNING - SOT223

PIN DESCRIPTION

1 gate

2 drain

3 source

4 drain

QUICK REFERENCE DATA

SYMBOL PARAMETER MAX. UNIT

−V

DS

−I

D

R

DS(on)

−V

GS(th)

handbook, halfpage

Fig.1 Simplified outline (SOT223) and symbol.

BSP92

drain-source voltage 240 V

DC drain current 180 mA

drain-source on-resistance 20 Ω

gate-source threshold voltage 1.8 V

123

Top view

4

g

MAM121

d

s

LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

−V

±V

−I

−I

P

T

T

DS

GSO

D

DM

tot

stg

j

drain-source voltage − 240 V

gate-source voltage open drain − 20 V

DC drain current − 180 mA

peak drain current − 720 mA

total power dissipation up to T

= 25 °C (note 1) − 1.5 W

amb

storage temperature range −65 150 °C

junction temperature − 150 °C

THERMAL RESISTANCE

SYMBOL PARAMETER THERMAL RESISTANCE

R

th j-a

from junction to ambient (note 1) 83.3 K/W

Note

1. Transistor mounted on an epoxy printed circuit board, 40 x 40 x 1.5 mm, mounting pad for the drain tab minimum

2

.

6cm

April 1995 2

Philips Semiconductors Product specification

P-channel enhancement mode vertical

BSP92

D-MOS transistor

CHARACTERISTICS

T

= 25 °C unless otherwise specified.

j

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

−V

(BR)DSS

−I

DSS

±I

GSS

−V

GS(th)

−V

GS

R

DS(on)

Y

transfer admittance −ID = 180 mA; −VDS = 25 V 100 200 − mS

fs

C

iss

C

oss

C

rss

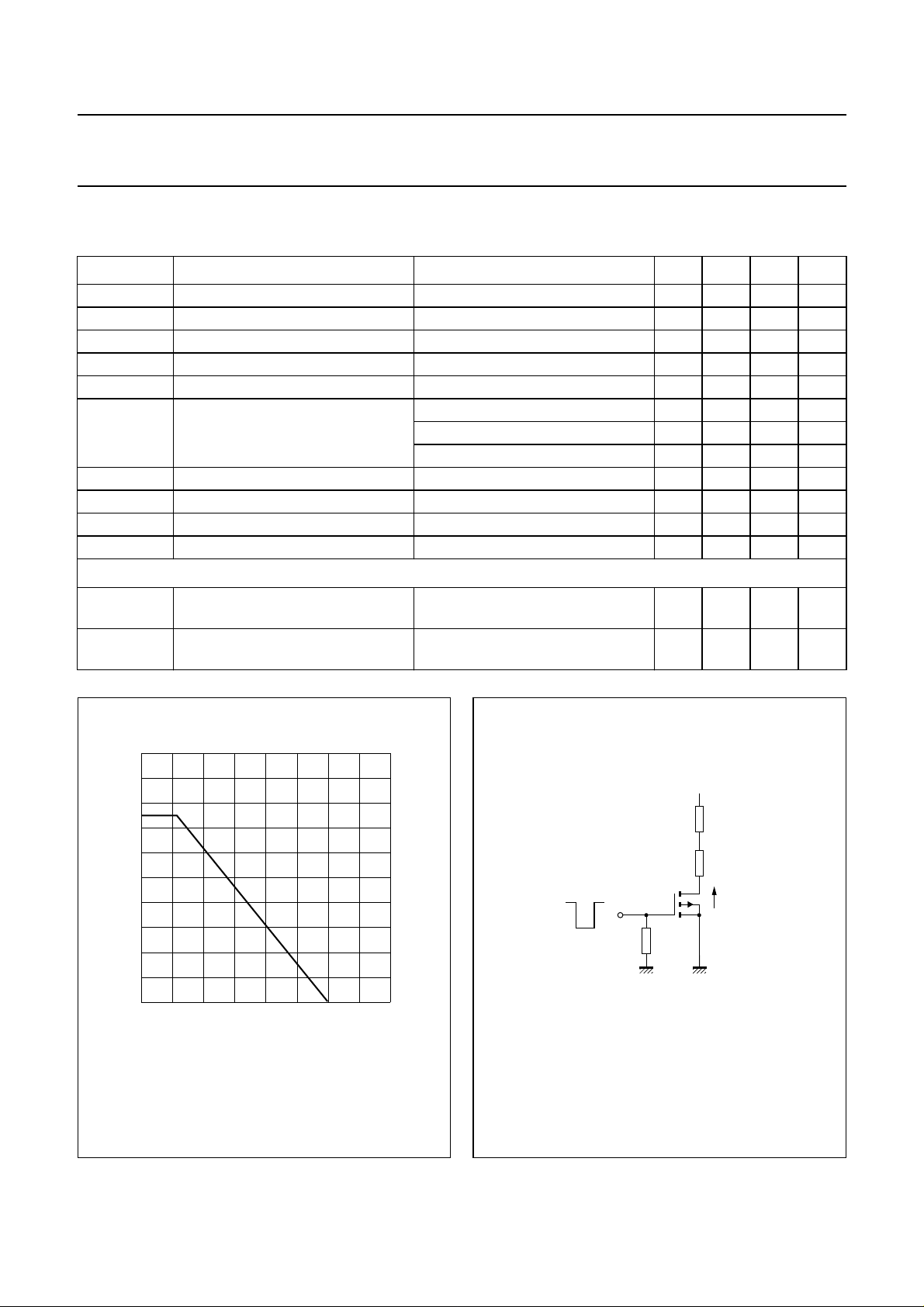

Switching times (see Figs 3 and 4)

t

on

t

off

drain-source breakdown voltage −ID = 10 µA; VGS = 0 240 −−V

drain-source leakage current −VDS = 200 V; VGS = 0 −−1µA

gate-source leakage current ±VGS = 20 V; VDS = 0 −−100 nA

gate-source threshold voltage −ID = 1 mA; VGS = V

DS

0.8 − 2V

gate-source voltage −ID = 50 mA; −VDS = 5 V 0.8 − 2.8 V

drain-source on-resistance −ID = 180 mA; −VGS = 10 V − 10 20 Ω

= 100 mA; −VGS = 5 V −−18 Ω

−I

D

−I

= 25 mA; −VGS = 2.8 V −−20 Ω

D

input capacitance −VDS = 25 V; VGS = 0; f = 1 MHz − 65 90 pF

output capacitance −VDS = 25 V; VGS = 0; f = 1 MHz − 20 30 pF

feedback capacitance −VDS = 25 V; VGS = 0; f = 1 MHz − 615pF

turn-on time −ID = 250 mA; −VDD = 50 V;

− 510ns

−VGS= 0 to 10 V

turn-off time −ID = 250 mA; −VDD = 50 V;

− 20 30 ns

−VGS= 0 to 10 V

handbook,

P

(W)

2

tot

1.6

1.2

0.8

0.4

0

0 50 100 200

150

T

amb

Fig.2 Power derating curve.

MBB693

(°C)

handbook, halfpage

0 V

−10 V

VDD = −50 V

I

D

50 Ω

MBB689

Fig.3 Switching times test circuit.

April 1995 3

Loading...

Loading...