Philips am6012 DATASHEETS

Philips Semiconductors Linear Products Product specification

AM601212-Bit multiplying D/A converter

776

August 31, 1994 853-0904 13721

DESCRIPTION

The AM6012 12-bit multiplying Digital-to-Analog converter provides

high-speed and 0.025% differential nonlinearity over its full

commercial temperature range.

The D/A converter uses a 3-bit segment generator for the MSBs in

conjunction with a 9-bit R-2R diffused resistor ladder to provide

12-bit resolution without costly trimming processes. This technique

guarantees a very uniform step size (up to ± LSB from the ideal),

monotonicity to 12 bits and integral nonlinearity to 0.05% at its

differential current outputs.

The dual complementary outputs of the AM6012 increase its

versatility, and effectively double the peak-to-peak output swing.

Digital inputs, in addition, can be configured to accept all popular

logic families.

While the device requires a reference input of 1mA for a 4mA

full-scale current, operation is nearly independent of power supply

voltage shifts. The power supply rejection ratio is ±0.001% FS/% ∆V.

The devices will work from +5, -12V to ±18V rails, with as low as

230mW power consumption typical.

FEATURES

•12-bit resolution

•Accurate to within ±0.05%

•Monotonic over temperature

•Fast settling time, 250ns typical

•Trimless design for low cost

•Differential current outputs

•High-speed multiplying capability

•Full-scale current, 4mA (with 1mA reference)

•High output compliance voltage, -5 to +10V

•Low power consumption, 230mW

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

20

19

18

17

16

15

D1 and F Packages

NOTE:

1. Available in large SO (SOL) package only.

TOP VIEW

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

8

D

9

D

10

V+

I

O

I

O

V–

COMP

V

REF(–)

V

REF(+)

GND/V

LC

D12 LSB

D

11

APPLICATIONS

•CRT displays, computer graphics

•Robotics and machine tools

•Automatic test equipment

•Programmable power supplies

•CAD/CAM systems

•Data acquisition and control systems

•Analog-to-digital converter systems

ORDERING INFORMATION

DESCRIPTION TEMPERATURE RANGE ORDER CODE DWG #

20-Pin Ceramic Dual In-Line Package (CERDIP) 0 to +70°C AM6012F 0584B

20-Pin Plastic Small Outline Large (SOL) Package 0 to +70°C AM6012D 0172D

Philips Semiconductors Linear Products Product specification

AM601212-Bit multiplying D/A converter

August 31, 1994

777

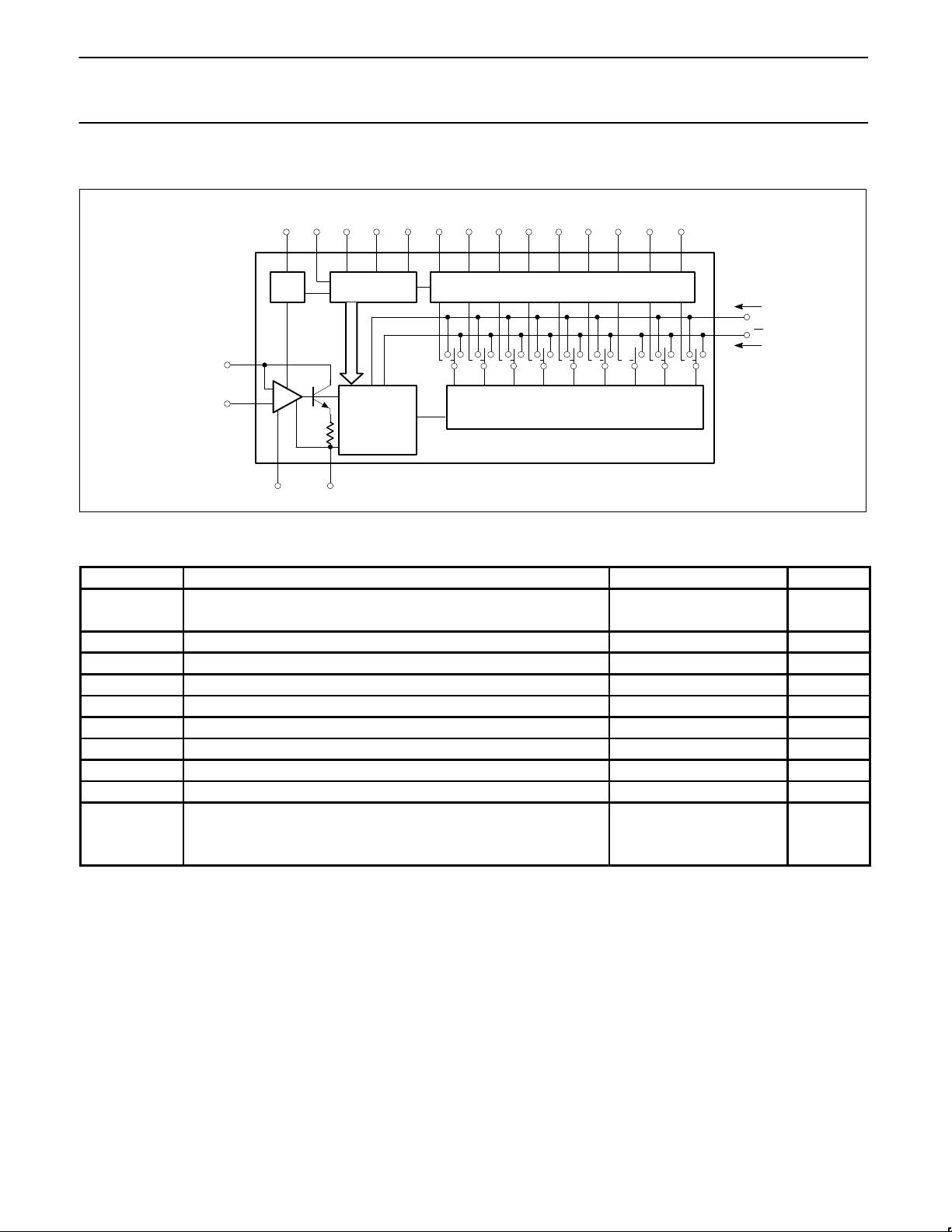

BLOCK DIAGRAM

COMP V(–)

16 17

V

REF

(+)

V

REF

(–)

14

15

BIAS

NETWORK

REFERENCE

AMPLIFIER

9-SEGMENT

GENERATOR

DECODER

CURRENT

SWITCHES

I

SEG

9-BIT R-2R

D/A CONVERTER

LOGIC SWITCHES

18

19

I

O

I

O

12111098765432113

LSBGND/MSB

20

V(+)

V

LC

B12B11B10B9b8B7B6B5B4B3B2B1

ABSOLUTE MAXIMUM RATINGS

SYMBOL PARAMETER RATING UNIT

T

A

Operating temperature

AM6012F 0 to +70 °C

T

STG

Storage temperature range -65 to +150 °C

T

SOLD

Lead soldering temperature 10sec max 300 °C

V

S

Power supply voltage ±18 V

Logic inputs -5V to +18 V

Voltage across current outputs -8V to +12 V

V

REF

Reference inputs V14, V

15

V- to V+

V

REF

Reference input differential voltage (V14 to V15) ±18 V

I

REF

Reference input current (I14) 1.25 mA

P

D

Maximum power dissipation, TA=25°C, (still-air)

1

F package 1560 mW

D package 1390 mW

NOTES:

1. Derate above 25°C, at the following rate:

F package at 12.5mW/°C

D package at 11.1mW/°C

Philips Semiconductors Linear Products Product specification

AM601212-Bit multiplying D/A converter

August 31, 1994

778

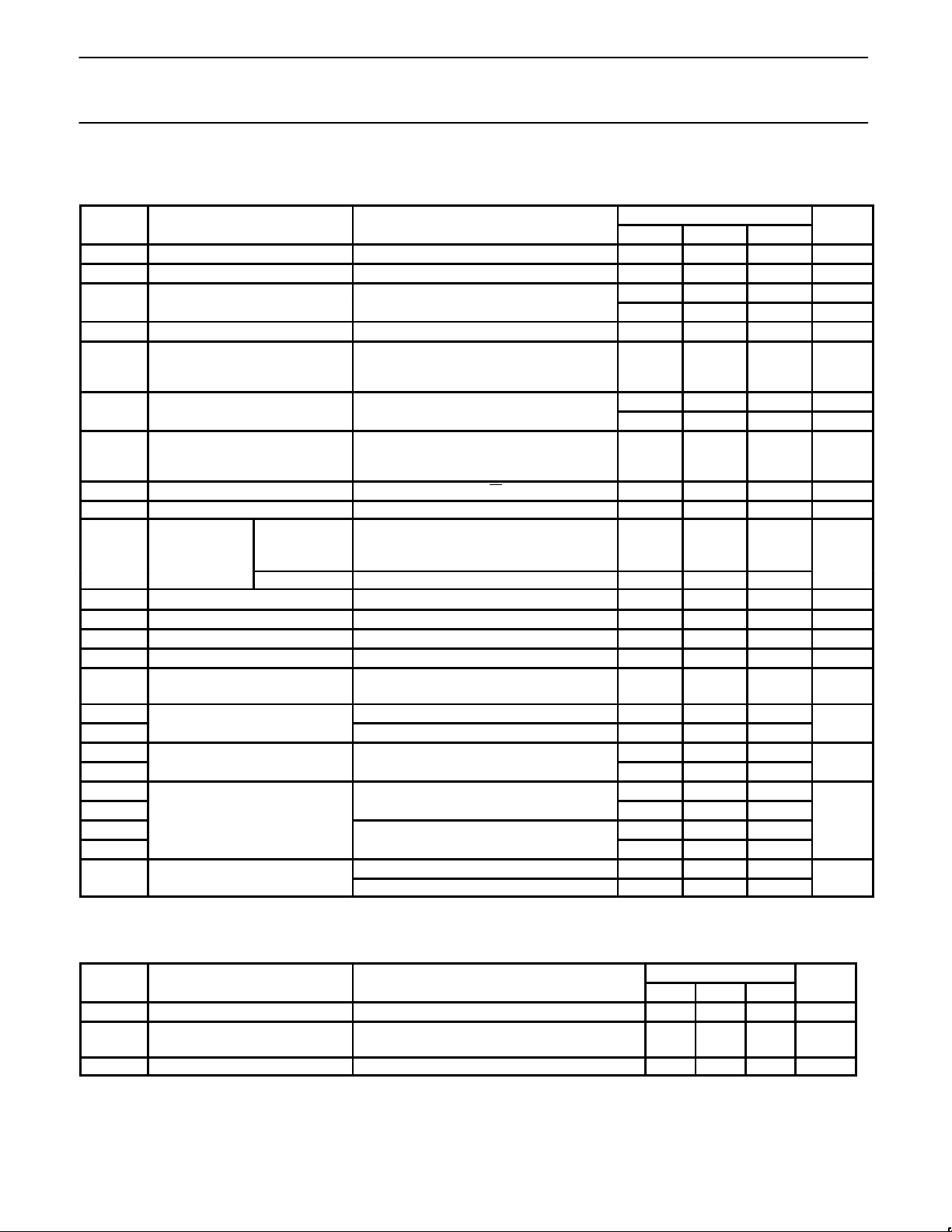

DC ELECTRICAL CHARACTERISTICS

V+=+15V, V-=-15V, I

REF

=1.0mA, 0°C ≤ T

A

≤ 70°C

LIMITS

SYMBOL

PARAMETER

TEST CONDITIONS

Min Typ Max

UNIT

Resolution 12 Bits

Monotonicity 12 Bits

DNL Differential nonlinearity Deviation from ideal step size ±0.025 %FS

12 Bits

NL Nonlinearity Deviation from ideal straight line ±.05 %FS

I

FS

Full-scale current

V

REF

=10.000V

R

14-R15

=10.000kΩ

T

A

=25°C

3.935 3.999 4.063 mA

TCI

FS

Full-scale tempco ±10 ±40 ppm/°C

±0.001 ±0.004 %FS/°C

V

OC

Output voltage compliance

DNL Specification guaranteed over

compliance range

R

OUT

>10MΩ typ.

-5 +10 V

I

FSS

Symmetry IFS-I

FS

±0.4 ±2.0 µA

I

ZS

Zero-scale current 0.10 µA

V

IL

V

IH

Logic

input

levels

Logic “0” 0.8 V

Logic “1” 2.0

I

IN

Logic input current VIN=-5 to +18V 40 µA

V

IS

Logic input swing V-=-15V -5 +18 V

I

REF

Reference current range 0.2 1.0 1.1 mA

I

15

Reference bias current 0 -0.5 -2.0 µA

dl/dt Reference input slew rate

R

14(eq)

=800Ω

C

C

=0pF

4.0 8.0 mA/µs

PSSI

FS+

Power supply sensitivity V+=+13.5V to +16.5V, V-=-15V ±0.0005 ±0.001 %FS/%

PSSI

FS-

V-=-13.5V to -16.5V, V+=+15V ±0.00025 ±0.001

V+ Power supply range V

OUT

=0V 4.5 18 V

V- -18 -10.8

I+ V+=+5V, V-=-15V 5.7 8.5

I- Power supply current -13.7 -18.0 mA

I+ V+=+15V, V-=-15V 5.7 8.5

I- -13.7 -18.0

P

D

Power dissipation V+=+5V, V-=-15V 234 312 mW

V+=+15V, V-=-15V 291 397

AC ELECTRICAL CHARACTERISTICS

V+=+15V, V-=-15V, I

REF

=1.0mA, 0°C ≤ T

A

≤ 70°C

LIMITS

SYMBOL

PARAMETER

TEST CONDITIONS

Min Typ Max

UNIT

t

S

Settling time To ± 1/2LSB, all bits ON or OFF, TA=25°C 250 500 ns

t

PLH

t

PHL

Propagation

delay—all bits

50% to 50% 25 50 ns

C

OUT

Output capacitance 20 pF

Philips Semiconductors Linear Products Product specification

AM601212-Bit multiplying D/A converter

August 31, 1994

779

CIRCUIT DESCRIPTION

The AM6012 is a 12-bit DAC which uses diffused resistors and

requires no trimming to guarantee monotonicity over the

temperature range. A segmented DAC design guarantees a more

uniform step size over the temperature range than is normally

available with trimmed 12-bit converters. The converter features

differential high compliance current outputs, wide supply range, and

a multiplying reference input.

In many converter applications, uniform step size is more important

than conformance to an ideal straight line. Many 12-bit converters

are used for high resolution rather than high linearity, since few

transducers are more linear than ±0.1%. All classic binarily weighted

converters require ±1/2LSB (±0.012%) linearity in order to guarantee

monotonicity, which requires very tight resistor matching and

tracking. The AM6012 uses conventional bipolar processing to

achieve high differential linearity and monotonicity without requiring

correspondingly high linearity, or conformance to an ideal straight

line.

One design approach which provides monotonicity without requiring

high linearity is the MOS switch-resistor string. This circuit is actually

a full complement to a current-switched R-2R DAC since it is slower,

has a voltage output, and, if implemented at the 12-bit level, would

use 4096 low tolerance resistors rather than a minimum number of

high tolerance resistors as in the R-2R network. Its lack of speed

and density for 12 bits are its drawbacks.

With the segmented DAC approach, the 4096 required output levels

are composed of 8 groups of 512 steps each. Each step group is

generated by a 9-bit DAC, and each of the segment slopes is

determined by one of 8 equal current sources. The resistors which

determine monotonicity are in the 9-bit DAC. The major carry of the

9-bit DAC is repeated in each of the 8 segments, and requires eight

times lower initial resistor accuracy and tracking to maintain a given

differential nonlinearity over temperature.

The operation of the segmented DAC may be visualized by

assuming an input code of all zeroes. The first segment current I

O

is

divided into 512 levels by the 9-bit multiplying DAC and fed to the

output, I

OUT

. As the input code increases, a new segment current is

selected for each 512 counts. The previous segment is fed to output

I

OUT

where the new step group is added to it, thus ensuring

monotonicity independent of segment resistor values. All higher

order segments feed I

OUT

.

With the segmented DAC approach, the precision of the 8 main

resistors determines linearity only. The influence of each of these

resistors on linearity is four times lower than that of the MSB resistor

in an R-2R DAC. Hence, assuming the same resistor tolerances for

both, the linearity of the segmented approach would actually be

higher than that of an R-2R design.

The step generator or 9-bit DAC is composed of a master and a

slave ladder. The slave ladder generates the four least significant

bits from the remainder of the master ladder by active current

splitting utilizing scaled emitters. This saves ladder resistors and

greatly reduces the range of emitter scaling required in the 9-bit

DAC. All current switches in the step generator are high-speed

fully-differential switches which are capable of switching low currents

at high speed. This allows the use of a binary scaled network all the

way to the least significant bit which saves power and simplifies the

circuitry.

Diffused resistors have advantages over thin film resistors beyond

simple economy and bipolar process compatibility. The resistors are

fabricated in single crystal rather than amorphous material which

gives them better long term stability and tracking and much higher

moisture resistance. They are diffused at 1000°C and so are

resistant to changes in value due to thermal and chemical causes.

Also, no burn-in is required for stability. The contact resistance

between aluminum and silicon is more predictable than between

aluminum and an amorphous thin film, and no sandwich metals are

required to enhance or protect the contact or limit alloying. The initial

match between two diffused resistors is similar to that of thin film

since both are defined by photomasks and chemical etching. Since

the resistors are not trimmed or altered after fabrication, their

tracking and long-term characteristics are not degraded.

DIFFERENTIAL VS INTEGRAL NONLINEARITY

Integral nonlinearity, for the purposes of the discussion, refers to the

“straightness” of the line drawn through the individual response

points of a data converter. Differential nonlinearity, on the other

hand, refers to the deviation of the spacing of the adjacent points

from a 1 LSB ideal spacing. Both may be expressed as either a

percentage of full-scale output or as fractional LSBs or both. The

graphs in Figure 1 define the manner in which these parameters are

specified. The left graph shows a portion of the transfer curve of a

DAC with 1/2LSB INL and the (implied) DNL spec of 1 LSB. Below

this is a graphic representation of the way this would appear on a

CRT screen where the AM6012 is used as a display driver. On the

right is a portion of the transfer curve of a DAC specified for 1/2LSB

INL with LSB DNL specified and the graphic display below it.

One of the characteristics of an R-2R DAC in standard form is that

any transition which causes a zero LSB change (i.e., the same

output for two different codes) will exhibit the same output each time

that transition occurs. The same holds true for transitions causing a

2 LSB change. These two problem transitions are allowable for the

standard definition of monotonicity and also allow the device to be

specified very tightly for INL. The major problem arising from this

error type is in A/D converter implementations. Inputs producing the

same output are now represented by ambiguous output codes for an

identical input. Also, two LSB gaps can cause large errors at those

input levels (assuming 1/2LSB quantizing levels). It can be seen

from the two figures that the DNL-specified D/A converter will yield

much finer grained data than the INL-specified part, thus improving

the ability of the A/D to resolve changes in the analog input.

Loading...

Loading...