Philips 75003407 DATASHEETS

The TriMedia™ TM-1000 is a general-purpose microprocessor for

real-time processing of audio, video, graphics, and communications

datastreams. In a single chip, TM-1000 combines an ultra-high

performance, low cost CPU with a full complement of I/O and

coprocessing peripheral units.

In consumer electronics appliances and personal computing products, the TM-1000 media processor performs multimedia functions

with the advantages of special-purpose, embedded DSP solutions —

low cost and single-chip packaging — and the programmability of

general-purpose CPUs. It improves time-to-market through highlevel C/C++ language programmability and delivers throughput of

up to four billion operations per second.

MUL TIMEDIA APPLICATIONS

TM-1000 is an ideal building block for any multimedia application

that requires processing of video, audio, graphics, and communications datastreams. It is well suited for applications ranging from

single-purpose systems such as videophones, to reprogrammable,

multipurpose devices such as set-top boxes or web browsers.

TM-1000 easily implements popular multimedia standards such as

MPEG-1 and MPEG-2, but its orientation around a powerful, programmable general-purpose CPU makes it capable of a variety of

multimedia algorithms, whether open or proprietary.

HARNESSING THE POWER OF VLIW

TM-1000 delivers top performance through its elegant implementation of a fine-grain parallel architecture known as very-long instruction word, or VLIW. Unique to the TriMedia processor’s VLIW

implementation, parallelism is optimized at compile time by the

TriMedia compilation system. No specialized scheduling hardware is

required to parallelize code during execution. Hardware saved by

eliminating complex scheduling logic reduces cost and allows the

integration of multimedia-specific features.

With the capacity to pack multiple operations into one VLIW

instruction and 27 functional units in which to process them,

TM-1000 can execute up to five operations in parallel with each

clock cycle. Such parallel processing is an ideal complement to the

inherently parallel nature of multimedia applications.

Another key contributor to TM-1000’s top performance is its use of

conditional execution. During program creation, an instruction

scheduler adds conditional code to each operation to enable guarded

execution — a technique that increases fine-grain parallelism and

significantly decreases code branching and execution time.

FEATURES

+ Processes audio,video,graphics, and communications

datastreams on a single chip

+ Powerful,fine-grain parallel,100 MHz VLIW CPU with

separate instruction and data caches

+ Independent,DMA-driven multimedia I/O units to

format data and multimedia coprocessors to offload

the TriMedia CPU of specific multimedia algorithms

+ High-performance bus and memory system to manage

communication between TriMedia processing units

+ Instruction set includes RISC, multimedia,SIMD-type

DSP,and IEEE-compliant floating point operations

+ Robust software development tools and libraries that

enable multimedia application development entirely in

C/C++ programming languages

+ Configurable for standalone and plug-in card applica-

tions in consumer electronics and PC products

Programmable Media Processor

T riMedia TM-1000

PROGRAMMABLE VLIW CPU

At the heart of the TM-1000 is a powerful DSP-like, 32-bit CPU

core. Its VLIW architecture utilizes a five-issue-slot engine. Parallelism

is achieved by simultaneously targeting up to five of the 27 pipelined

functional units in the TM-1000 processor within one clock cycle.

The most common operations have their results available in one clock

cycle; more complex operations have multi-cycle latencies.

Functional units include integer and floating-point arithmetic units

and data-parallel DSP-like units. They can access 128 fully generalpurpose, 32-bit registers during execution. The registers are not separated into banks; any operation can use any register for any operand.

TM-1000’s instruction set includes common RISC operations, special

DSP operations that perform powerful SIMD functions, custom multimedia functions, and a full complement of 32-bit, IEEE-compliant,

floating point operations. Both big and little endian byte ordering are

supported.

The TriMedia CPU provides special support for instruction and data

breakpoints, useful in debugging and program development.

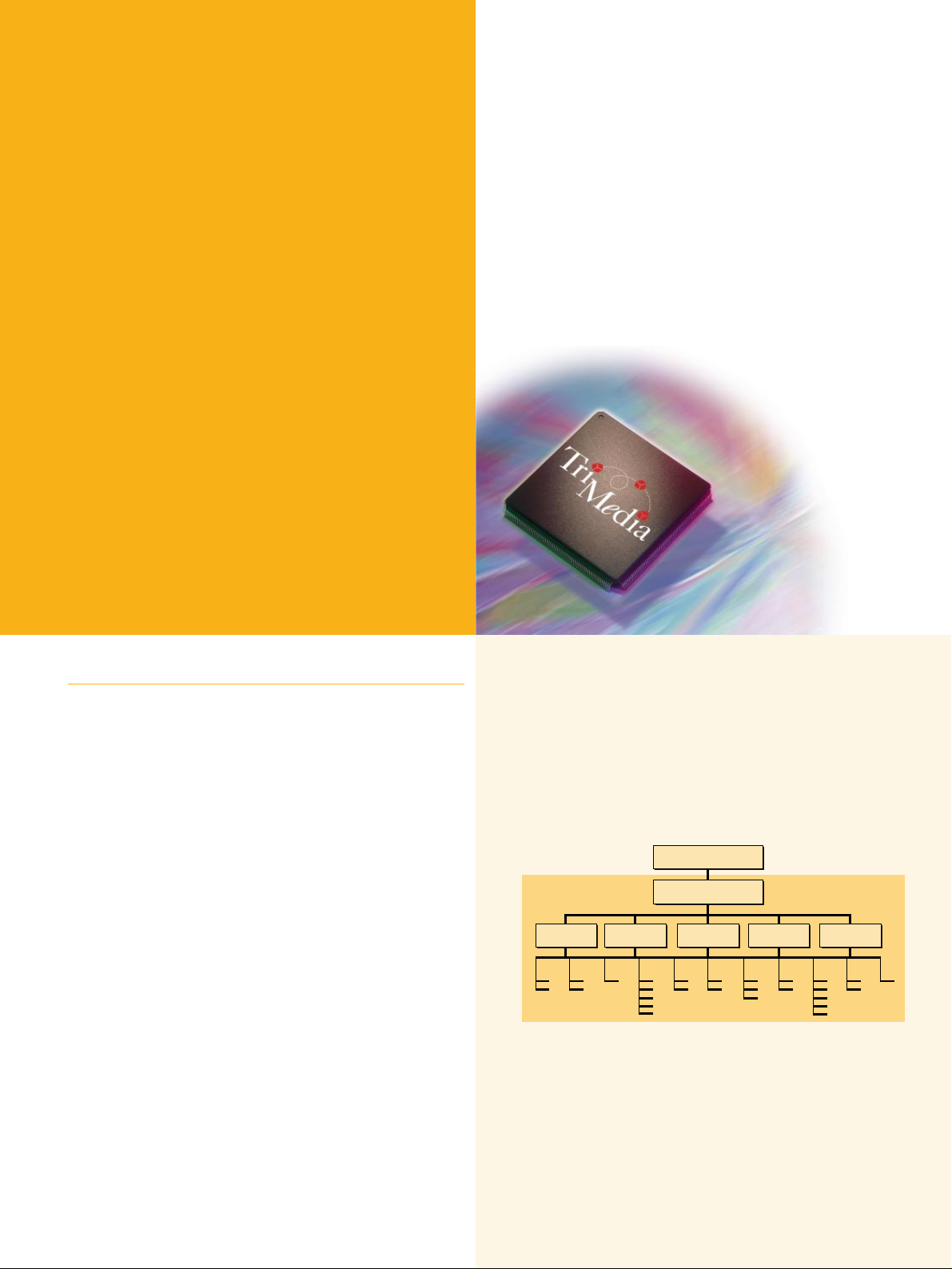

TRIMEDIA INSTRUCTION EXECUTION

TM-1000’s unique VLIW CPU utilizes separate instruction and data caches ,

five issue slots, 27 pipelined functional units, and 128 general-purpose,

32-bit registers to process up to five operations in one clock c ycle.

TM-1000

a single-chip

multimedia

workhorse

First in the family of TriMedia

processors,the TM-1000 is more

than just an integrated micro-

processor with unusual peripherals.

It is a fluid single-chip computer

system controlled by a small

real-time operating system kernel

running on a VLIW CPU.

INSTRUCTION CACHE

SDRAM

INSTRUCTION CACHE

ISSUE SLOT 1 ISSUE SLOT 2 ISSUE SLOT 3 ISSUE SLOT 4 ISSUE SLOT 5

FUNCTIONAL UNITS

DEDICATED INSTRUCTION AND DATA CACHE

TM-1000’s CPU is supported by separate, dedicated on-chip data and

instruction caches. To improve cache behavior and performance, both

caches have a locking mechanism. Cache coherency is maintained by

software.

Data cache is dual-ported to allow two simultaneous accesses. It is

non-blocking, thus handling cache misses and CPU cache accesses can

proceed simultaneously. Early restart techniques reduce read-miss

latency. Background copyback reduces CPU stalls. Partial word (8-bit

and 16-bit) memory operations are supported.

To reduce internal bus bandwidth requirements, instructions in main

memory and cache use a compressed format. Instructions are decompressed in the instruction cache decompression unit before being

processed by the CPU.

No external second-level cache is required to deliver media performance an order of magnitude more than x86 processors.

GLUELESS MEMORY SYSTEM INTERFACE

The TM-1000 memory system balances cost and performance by coupling substantial on-chip caches with a glueless interface to synchronous

DRAM (SDRAM). Higher bandwidth SDRAM permits the TM-1000

to use a narrower and simpler interface than would be required to

achieve similar performance with standard DRAM.

TM-1000’s memory interface provides sufficient drive capacity for an

up to 100-MHz, 8-MB memory system (four 2Mx8 SDRAMS).

Larger memories can be implemented by using lower memory system

clock frequencies or external buffers. Programmable speed ratios allow

SDRAM to have a different clock speed than the TM-1000 CPU.

Support for a variety of memory types, speeds, bus widths, and offchip bank sizes allow a range of TM-1000-based systems to be

configured.

HIGH-SPEED INTERNAL BUS (DATA HIGHWAY)

TM-1000’s internal bus, or data highway, connects all internal function units together and provides access to control registers in each

function unit, to external SDRAM, and to the external PCI bus. It

consists of separate 32-bit data and address buses; bus transactions use

a block transfer protocol. On-chip peripheral units and coprocessors

can be masters or slaves on the bus. Programmable bandwidth allocation enables the data highway to maintain real-time responsiveness in

a variety of applications.

TM-1000 ARCHITECTURE

On a single chip, the TM-1000 incorporates a powerful VLIW CPU

and peripherals to accelerate processing of audio, video, graphics,

and communications data.

Unique to the TriMedia

processor’s VLIW

implementation,

parallelism is

optimized at compile

time by the TriMedia

compilation system.

SDRAM

MAIN MEMORY

INTERFACE

I2C INTERFACE

AUDIO OUT

AUDIO IN

SYNCHRONOUS

SERIAL INTERFACE

TIMERS

VIDEO OUT

VLIW CPU

INSTR.

CACHE

DATA

CACHE

IMAGE

COPROCESSOR

PCI INTERFACE

VIDEO IN

VLD COPROCESSOR

TO

PCI BUS

Loading...

Loading...