Philips 74LVT74PW, 74LVT74DB, 74LVT74D Datasheet

INTEGRATED CIRCUITS

74LVT74

3.3V Dual D-type flip-flop

Product specification 1996 Aug 28

IC24 Data Handbook

Philips Semiconductors Product specification

74L VT743.3V Dual D-type flip-flop

QUICK REFERENCE DATA

CONDITIONS

SYMBOL PARAMETER

IN

CC

Propagation

delay

CPn to Qn

Input

capacitance

Total supply

current

t

PLH

t

PHL

C

I

T

CL = 50pF;

V

CC

VI = 0V or 3.0V 3 pF

VCC = 3.6V 0.5 mA

PIN CONFIGURATION

1

D0

R

2

D0

3

CP0

4

S

D0

5

Q0

6

Q

0

GND

LOGIC SYMBOL

D0 D1

CP0

S

D0

D0

R

CP1

D1

S

RD1

Q0 Q0Q1Q1

56 98

VCC = Pin 14

GND = Pin 7

3

4

1

11

10

13

= 25°C;

amb

GND = 0V

= 3.3V

212

DESCRIPTION

The 74LVT74 is a dual positive edge-triggered D-type flip-flop

TYPICAL UNIT

featuring individual data, clock, set, and reset inputs; also true and

complementary outputs. Set (S

D) and reset (RD) are asynchronous

active low inputs and operate independently of the clock input.

3.1

3.6

ns

When set and reset are inactive (high), data at the D input is

transferred to the Q and Q

outputs on the low-to-high transition of

the clock. Data must be stable just one setup time prior to the

low-to-high transition of the clock for predictable operation. Clock

triggering occurs at a voltage level and is not directly related to the

transition time of the positive-going pulse. Following the hold time

interval, data at the D input may be changed without affecting the

levels of the output.

PIN DESCRIPTION

14

V

CC

13

D1

R

12

D1

11

CP1

10

SD1

9

Q1

87

Q1

SF00045

SA00359

PIN NUMBER SYMBOL NAME AND FUNCTION

2, 12 D0, D1 Data inputs

3, 11 CP0, CP1 Clock inputs (active rising edge)

4, 10 SD0, SD1 Set inputs (active LOW)

1, 13 RD0, RD1 Reset inputs (active LOW)

5, 6, 8, 9 Qn, Qn Data outputs

LOGIC SYMBOL (IEEE/IEC)

4

3

2

1

10

11

12

13

&

S

C1

1D

R

S

C2

2D

R

5

6

9

8

SF00047

ORDERING INFORMA TION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

14-Pin Plastic SO –40°C to +85°C 74LVT74 D 74LVT74 D SOT108-1

14-Pin Plastic SSOP –40°C to +85°C 74LVT74 DB 74LVT74 DB SOT337-1

14-Pin Plastic TSSOP –40°C to +85°C 74LVT74 PW 74LVT74PW DH SOT402-1

1996 Aug 28 853-1872 17244

2

Philips Semiconductors Product specification

I

DC out ut current

mA

SYMBOL

PARAMETER

UNIT

74LVT743.3V Dual D-type flip-flop

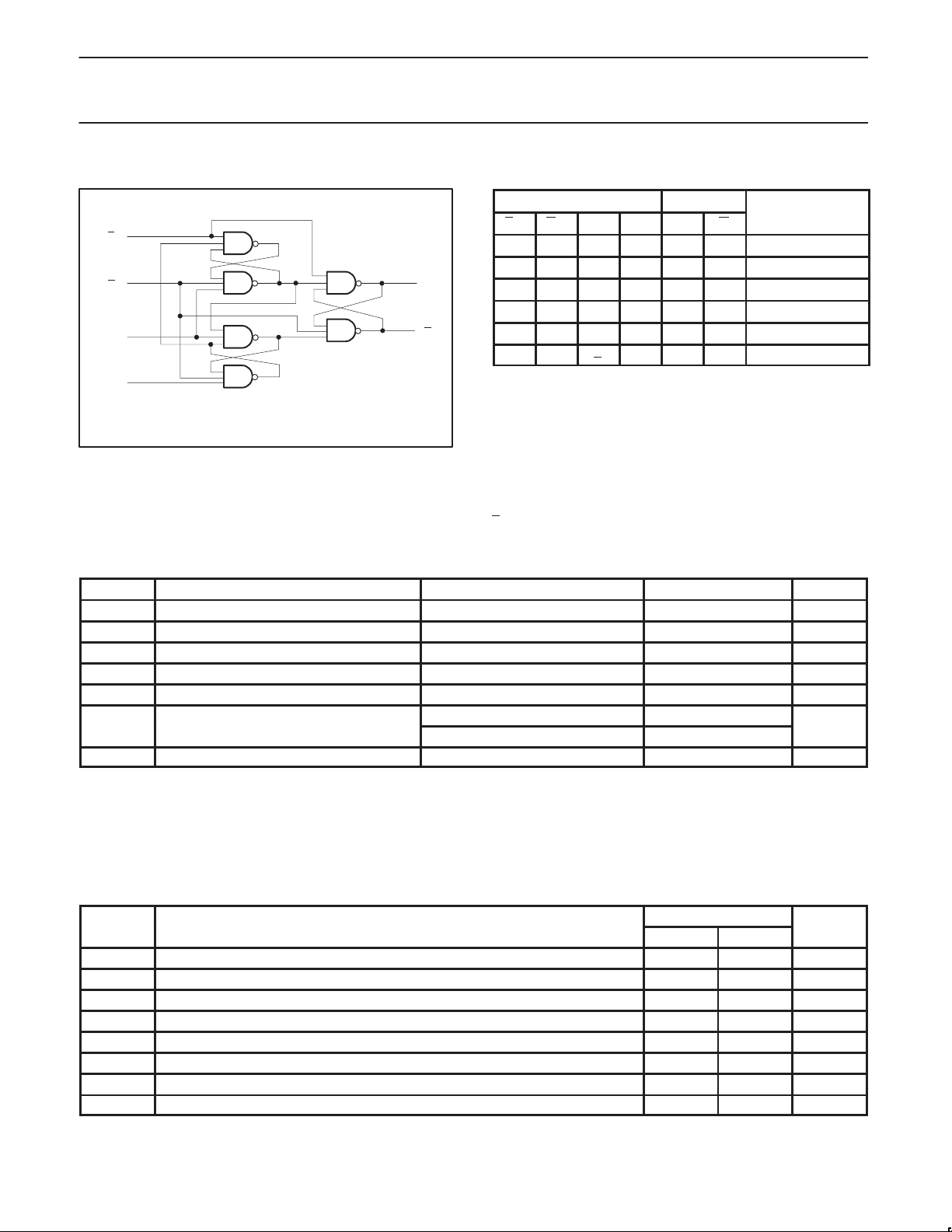

LOGIC DIAGRAM

4, 10

S

D

1, 13

D

R

3, 11

CP

5, 9

6, 8

Q

Q

FUNCTION TABLE

INPUTS OUTPUTS

SD RD CP D Q Q

L H X X H L Asynchronous set

H L X X L H Asynchronous reset

L L X X H H Undetermined*

H H ↑ h H L Load “1”

H H ↑ l L H Load “0”

OPERATING

MODE

H H ↑ X NC NC Hold

D

VCC = Pin 14

GND = Pin 7

2, 12

SF00048

NOTES:

H = High voltage level

h = High voltage level one setup time prior to low-to-high

clock transition

L = Low voltage level

l = Low voltage level one setup time prior to low-to-high

clock transition

NC= No change from the previous setup

X = Don’t care

↑ = Low-to-high clock transition

= Not low-to-high clock transition

↑

* = This setup is unstable and will change when either set

or reset return to the high level.

ABSOLUTE MAXIMUM RATINGS

SYMBOL

V

CC

I

IK

V

I

I

OK

V

OUT

OUT

T

stg

DC supply voltage –0.5 to +4.6 V

DC input diode current VI < 0 –50 mA

DC input voltage

DC output diode current VO < 0 –50 mA

DC output voltage

p

Storage temperature range –65 to 150 °C

PARAMETER CONDITIONS RATING UNIT

3

3

1, 2

–0.5 to +7.0 V

Output in Off or High state –0.5 to +7.0 V

Output in High state –32

Output in Low state 64

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction

temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

3. The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

RECOMMENDED OPERATING CONDITIONS

1996 Aug 28

LIMITS

MIN MAX

V

CC

V

V

V

I

OH

I

OL

DC supply voltage 2.7 3.6 V

Input voltage 0 5.5 V

I

High-level input voltage 2.0 V

IH

Low-level Input voltage 0.8 V

IL

High-level output current –20 mA

Low-level output current 32 mA

∆t/∆v Input transition rise or fall rate; Outputs enabled 10 ns/V

T

amb

Operating free-air temperature range –40 +85 °C

3

Loading...

Loading...