Philips 74LVT125PW, 74LVT125DB, 74LVT125D Datasheet

INTEGRATED CIRCUITS

74LVT125

3.3V Quad buffer (3-State)

Product specification

Supersedes data of 1995 Nov 14

IC23 Data Handbook

1998 Feb 19

Philips Semiconductors Product specification

74L VT1253.3V Quad buffer (3-State)

FEA TURES

•Quad bus interface

•3-State buffers

•Output capability: +64mA/-32mA

•TTL input and output switching levels

•Input and output interface capability to systems at 5V supply

•Bus-hold data inputs eliminate the need for external pull-up

resistors to hold unused inputs

•Live insertion/extraction permitted

•No bus current loading when output is tied to 5V bus

•Power-up 3-State

•Latch-up protection exceeds 500mA per JEDEC Std 17

•ESD protection exceeds 2000V per MIL STD 883 Method 3015

and 200V per Machine Model

QUICK REFERENCE DATA

SYMBOL PARAMETER

C

t

PLH

t

PHL

C

OUT

I

CCZ

IN

Propagation delay

An to Yn

Input capacitance VI = 0V or 3.0V 4 pF

Output capacitance Outputs disabled; VO = 0V or 3.0V 8 pF

Total supply current

DESCRIPTION

The LVT125 is a high-performance BiCMOS product designed for

V

operation at 3.3V .

CC

This device combines low static and dynamic power dissipation with

high speed and high output drive.

The 74LVT125 device is a quad buffer that is ideal for driving bus

lines. The device features four Output Enables (OE

OE

3), each controlling one of the 3-State outputs.

CONDITIONS

T

= 25°C; GND = 0V

amb

CL = 50pF; VCC = 3.3V

Outputs disabled;

V

= 3.6V

CC

0, OE1, OE2,

TYPICAL UNIT

2.7

2.9

ns

0.13 mA

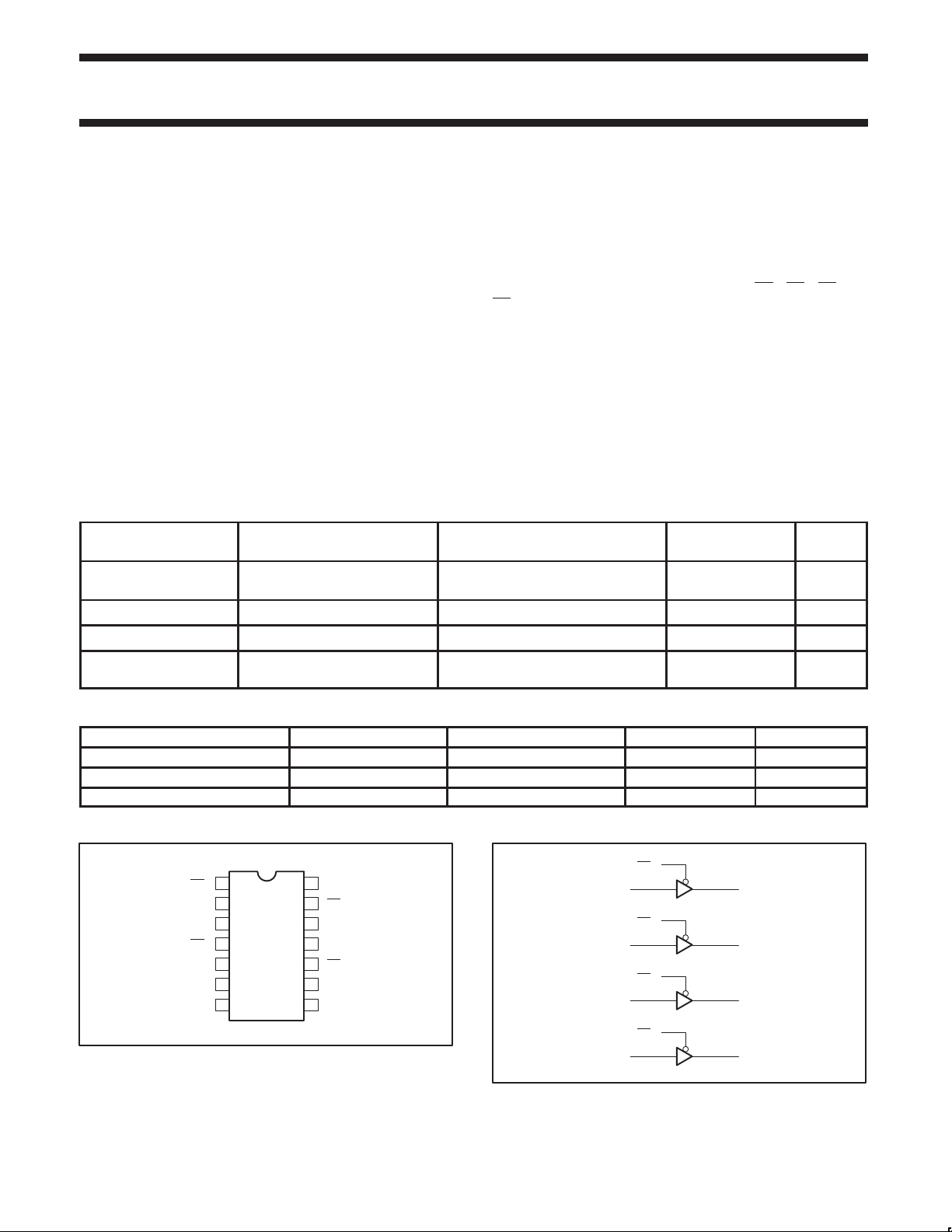

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

14-Pin Plastic SO –40°C to +85°C 74LVT125 D 74LVT125 D SOT108-1

14-Pin Plastic SSOP –40°C to +85°C 74LVT125 DB 74LVT125 DB SOT337-1

14-Pin Plastic TSSOP –40°C to +85°C 74LVT125 PW 74LVT125PW DH SOT402-1

PIN CONFIGURATION

1

OE0

2

A0

3

Y0

4

OE1

5

A1

6

Y1

7

GND Y2

14

13

12

11

10

9

8

SV00001

V

OE

A3

Y3

OE

A2

CC

3

2

LOGIC SYMBOL

1

0

OE

2

A0

4

OE1

5

A1

10

OE

2

9

A2

13

OE3

12

A3

3

Y0

6

Y1

8

Y2

11

Y3

SV00002

1998 Feb 19 853–1743 18991

2

Philips Semiconductors Product specification

I

DC output current

74LVT1253.3V Quad buffer (3-State)

LOGIC SYMBOL (IEEE/IEC)

1

EN

2

4

5

10

9

13

12

PIN DESCRIPTION

PIN NUMBER SYMBOL NAME AND FUNCTION

2, 5, 9, 12 A0 – A3 Data inputs

3, 6, 8, 11 Y0 – Y3 Data outputs

1, 4, 10, 13 OE0 – OE3 Output enables

7 GND Ground (0V)

14 V

FUNCTION T ABLE (EACH BUFFER)

INPUTS OUTPUTS

1

3

6

H = High voltage level

8

L = Low voltage level

X = Don’t care

Z = High impedance “Off” state

11

SV00003

CC

OEn An Yn

L L L

L H H

H X Z

Positive supply voltage

ABSOLUTE MAXIMUM RATINGS

SYMBOL

V

CC

V

I

V

OUT

OUT

I

IK

I

OK

T

stg

DC supply voltage –0.5 to +4.6 V

DC input voltage

DC output voltage

p

DC input diode current VI < 0 –50 mA

DC output diode current VO < 0 –50 mA

Storage temperature range –65 to 150 °C

PARAMETER CONDITIONS RATING UNIT

3

3

1, 2

–0.5 to +7.0 V

Output in Off or High state –0.5 to +7.0 V

Output in Low state 128 mA

Out in High State –64 mA

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction

temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

3. The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

1998 Feb 19

3

Loading...

Loading...