Philips 74LVCH16373ADL, 74LVCH16373ADGG, 74LVC16373ADL, 74LVC16373ADGG Datasheet

INTEGRATED CIRCUITS

74LVC16373A/74LVCH16373A

16-bit D-type transparent latch with 5 Volt

tolerant inputs/outputs (3-State)

Product specification

Supersedes data of 1997 Aug 22

IC24 Data Handbook

1998 Mar 17

Philips Semiconductors Product specification

16-bit D-type transparent latch with 5 Volt tolerant

inputs/outputs (3-State)

FEA TURES

•5 volt tolerant inputs/outputs for interfacing with 5V logic

•Wide supply voltage range of 1.2V to 3.6V

•Complies with JEDEC standard no. 8-1A

•CMOS low power consumption

•MULTIBYTE

TM

flow-through standard pin-out architecture

•Low inductance multiple power and ground pins for minimum

noise and ground bounce

•Direct interface with TTL levels

•All data inputs have bus hold (74LVCH167373A only)

•High impedance when V

DESCRIPTION

The 74LVC(H)16373A is a 16-bit D-type transparent latch featuring

separate D-type inputs for each latch and 3-State outputs for bus

oriented applications. One latch enable (LE) input and one output

enable (OE

either 3.3V or 5V devices. In 3-State operation, outputs can handle

5V. These features allow the use of these devices in a mixed

3.3V/5V environment.

The 74LVC(H)16373A consists of 2 sections of eight D-type

transparent latches with 3-State true outputs. When LE is HIGH,

data at the Dn inputs enter the latches. In this condition the latches

are transparent, i.e., a latch output will change each time its

corresponding D-input changes.

When LE is LOW the latches store the information that was present

at the D-inputs a set-up time preceding the HIGH-to-LOW transition

of LE. When OE

available at the outputs. When OE

high impedance OFF-state. Operation of the OE

affect the state of the latches.

The 74LVCH16373A bus hold data inputs eliminates the need for

external pull up resistors to hold unused inputs.

) are provided for each octal. Inputs can be driven from

is LOW, the contents of the eight latches are

= 0

CC

is HIGH, the outputs go to the

input does not

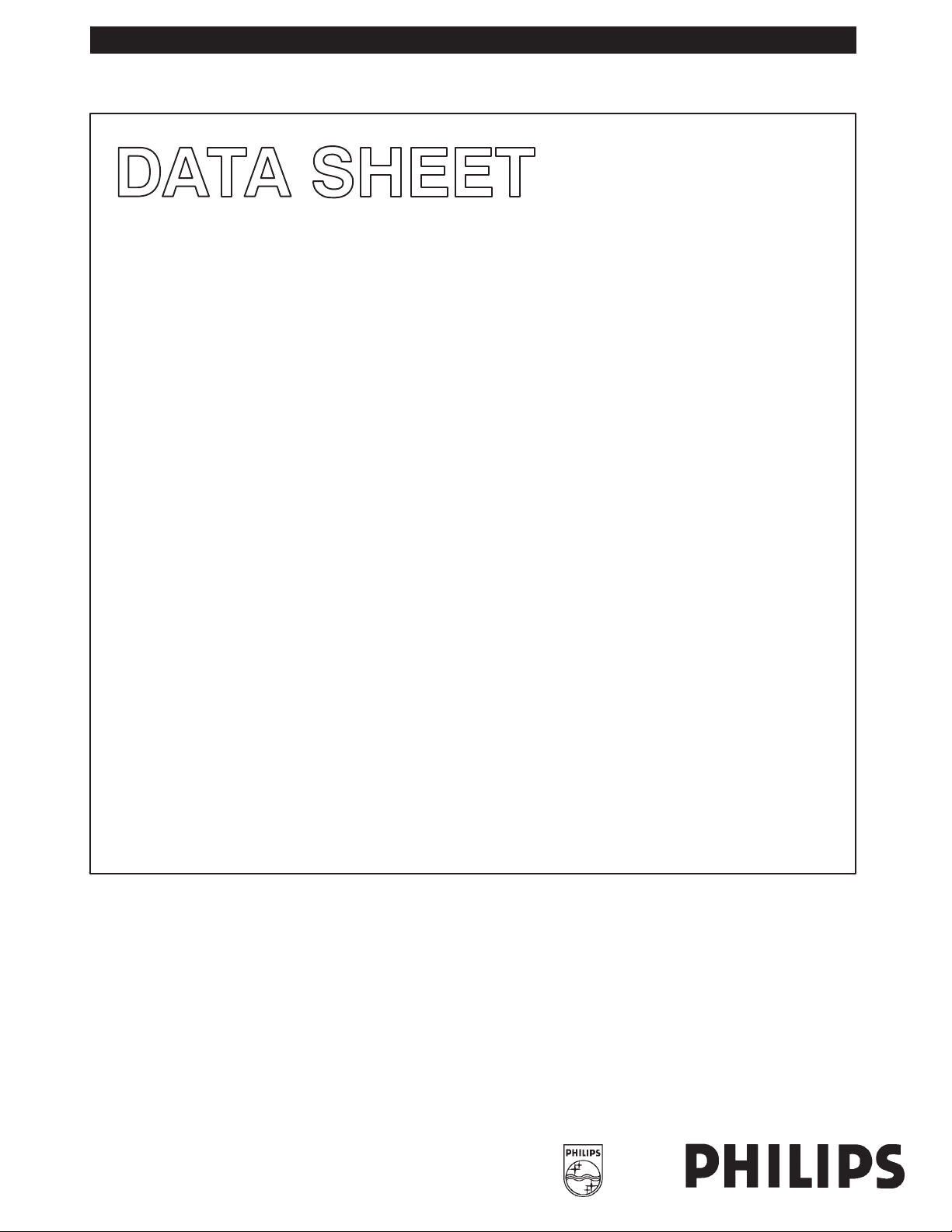

PIN CONFIGURATION

1OE

1Q0

1Q1

GND

1Q2

1Q3

V

1Q4

1Q5

GND

1Q6

1Q7

2Q0

2Q1

GND

2Q2

2Q3

V

2Q4

2Q5

GND

2Q6

2Q7

2OE

74L VC16373A/

74L VCH16373A

1LE

1

2

3

4

5

6

7

CC

8

9

10

11

12

13

14

15

16

17

18

CC

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SW00066

1D0

1D1

GND

1D2

1D3

V

CC

1D4

1D5

GND

1D6

1D7

2D0

2D1

GND

2D2

2D3

V

CC

2D4

2D5

GND

2D6

2D7

2LE

QUICK REFERENCE DA TA

GND = 0V; T

SYMBOL

t

PHL/tPLH

C

I

C

PD

NOTES:

is used to determine the dynamic power dissipation (PD in µW):

1. C

PD

= CPD × V

P

D

= input frequency in MHz; CL = output load capacity in pF;

f

i

f

= output frequency in MHz; VCC = supply voltage in V;

o

(C

= 25°C; tr = tf ≤ 2.5ns

amb

Propagation delay

Dn to Qn

LE to Qn

Input capacitance 5.0 pF

Power dissipation capacitance per latch VCC = 3.3V 26 pF

CC

2

× V

L

× fo) = sum of outputs.

CC

2

× fi + (CL × V

PARAMETER CONDITIONS TYPICAL UNIT

2

× fo) where:

CC

CL = 50pF

VCC = 3.3V

3.0

3.4

ns

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

48-Pin Plastic SSOP Type III –40°C to +85°C 74LVC16373A DL VC16373A DL SOT370-1

48-Pin Plastic TSSOP Type II –40°C to +85°C 74LVC16373A DGG VC16373A DGG SOT362-1

48-Pin Plastic SSOP Type III –40°C to +85°C 74LVCH16373A DL VCH16373A DL SOT370-1

48-Pin Plastic TSSOP Type II –40°C to +85°C 74LVCH16373A DGG VCH16373A DGG SOT362-1

1998 Mar 17 853-2027 19112

2

Philips Semiconductors Product specification

OPERATING MODES

16-bit D-type transparent latch with 5 Volt tolerant

inputs/outputs (3-State)

PIN DESCRIPTION

PIN NUMBER SYMBOL NAME AND FUNCTION

1 1OE

2, 3, 5, 6, 8, 9,

11, 12

1Q0 to 1Q7 Data inputs/outputs

4, 10, 15, 21,

28, 34, 39, 45

7, 18, 31, 42 V

13, 14, 16, 17,

19, 20, 22, 23

2Q0 to 2Q7 Data inputs/outputs

24 2OE

25 2LE

36, 35, 33, 32,

30, 29, 27, 26

47, 46, 44, 43,

41, 40, 38, 37

2D0 to 2D7 Data inputs

1D0 to 1D7 Data inputs

48 1LE

GND Ground (0V)

CC

Output enable input

(active LOW)

Positive supply voltage

Output enable input

(active LOW)

Latch enable input (active

HIGH)

Latch enable input (active

HIGH)

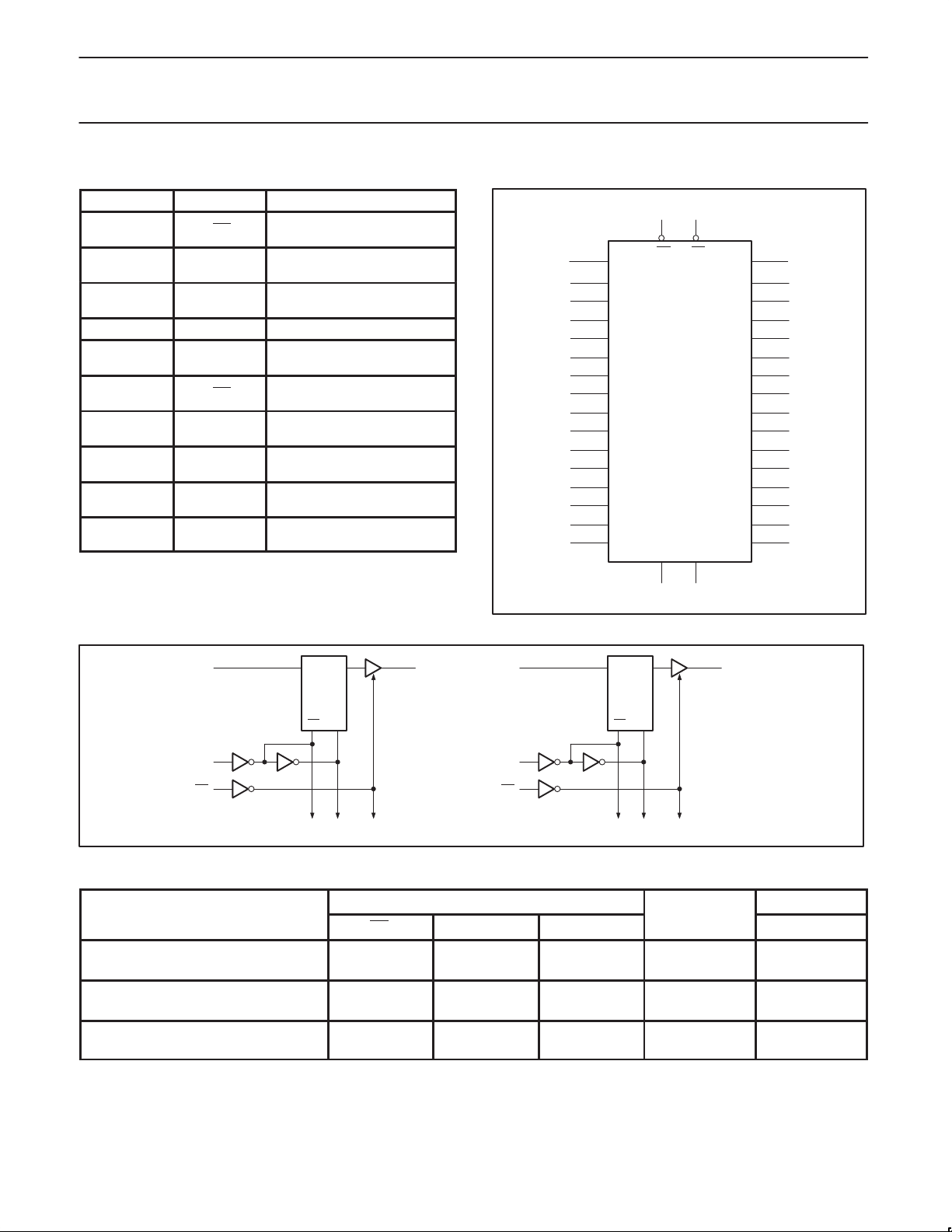

LOGIC SYMBOL

74LVC16373A/

74LVCH16373A

241

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1D0

1D1

1D2

1D3

1D4

1D5

1D6

1D7

2D0

2D1

2D2

2D3

2D4

2D5

2D6

2D7

1OE 2OE

1LE 2LE

1Q0

1Q1

1Q2

1Q3

1Q4

1Q5

1Q6

1Q7

2Q0

2Q1

2Q2

2Q3

2Q4

2Q5

2Q6

2Q7

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

LOGIC DIAGRAM

1D0

1LE

1OE

DQ

LATCH

1

LE

LE

TO 7 OTHER CHANNELS

1Q0

2D0

2LE

2OE

FUNCTION TABLE (per section of eight bits)

INPUTS

OE LE Dn

enable and read register

(transparent mode)

latch and read register

latch register and disable outputs

H = HIGH voltage level

h = HIGH voltage level one set-up time prior to the HIGH-to-LOW LE transition

L = LOW voltage level

l = LOW voltage level one set-up time prior to the HIGH-to-LOW LE transition

X = don’t care

Z = high impedance OFF-state

L

L

L

L

H

H

H

H

L

L

L

L

48 25

DQ

LATCH

9

LE

LE

TO 7 OTHER CHANNELS

INTERNAL

LATCHES

L

H

l

h

l

h

SW00067

2Q0

SW00068

OUTPUTS

Q0 to Q7

L

H

L

H

L

H

L

H

L

H

Z

Z

1998 Mar 17

3

Loading...

Loading...