Philips 74lvc4245a DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

74LVC4245A

Octal dual supply translating

transceiver; 3-state

Product specification

Supersedes data of 1998 Jul 29

File under Integrated Circuits, IC24

1999 Jun 15

Philips Semiconductors Product specification

Octal dual supply translating transceiver; 3-state 74LVC4245A

FEATURES

• In accordance with JEDEC

standard no. 8-1A

• Wide supply voltage range:

3 V port: 1.5 to 3.6 V

5 V port: 1.5 to 5.5 V

DESCRIPTION

The 74LVC4245A is a high-performance, low-power, low-voltage, Si-gate

CMOS device, superior to most advanced CMOS compatible TTL families.

The 74LVC4245A is an octal dual supply translating transceiver featuring

non-inverting 3-state bus compatible outputs in both send and receive

directions. It is designed to interface between a 3 and 5 V bus in a mixed 3/5 V

supply environment.

• CMOS low power consumption

• Direct interface with TTL levels

• Control inputs accept voltages up

The 74LVC4245A features an output enable (OE) input for easy cascading and

a send/receive (DIR) input for direction control. (OE) controls the outputs so

that the buses are effectively isolated.

to 5.5 V.

In suspend mode, when V

is zero, there will be no current flow from one

CCA

supply to the other supply. The A-outputs must be set 3-state and the voltage

on the A-bus must be smaller than V

(typ. 0.7 V). V

diode

CCA

≥ V

CCB

suspend mode).

QUICK REFERENCE DATA

GND = 0 V; T

=25°C; tr=tf≤2.5 ns.

amb

SYMBOL PARAMETER CONDITIONS TYPICAL UNIT

t

PHL/tPLH

C

I/O

C

PDA

C

PDB

propagation delay CL=50pF

A

to B

n

n

B

to A

n

n

V

= 5.0 V 4.0 ns

CCA

V

= 3.3 V 4.0 ns

CCB

input/output capacitance 10.0 pF

A port

to B

A

n

n

B

to A

n

n

VI= GND to VCC; note 1 7.8 pF

VI= GND to VCC; note 1 27.9 pF

B port

to B

A

n

n

B

to A

n

n

VI= GND to VCC; note 1 26 pF

VI= GND to VCC; note 1 10.4 pF

(except in

Note

1. C

is used to determine the dynamic power dissipation (PDin µW).

PD

PD=CPD× V

2

× fi+ Σ(CL× V

CC

2

× fo) where:

CC

fi= input frequency in MHz;

fo= output frequency in MHz;

CL= output load capacitance in pF;

VCC= supply voltage in Volts;

Σ(CL× V

2

× fo) = sum of the outputs.

CC

1999 Jun 15 2

Philips Semiconductors Product specification

Octal dual supply translating transceiver; 3-state 74LVC4245A

FUNCTION TABLE

See note 1.

INPUT INPUT/OUTPUT

OE DIR A

n

B

n

L L A = B inputs

L H inputs B = A

HX Z Z

Note

1. H = HIGH voltage level;

L = LOW voltage level;

X = don’t care;

Z = high-impedance OFF-state.

ORDERING INFORMATION

PACKAGE

OUTSIDE NORTH

AMERICA

NORTH AMERICA

TEMPERATURE

RANGE

PINS PACKAGE MATERIAL CODE

74LVC4245AD 74LVC4245AD −40 to +85 °C 24 SO plastic SOT137-1

74LVC4245ADB 74LVC4245ADB 24 SSOP plastic SOT340-1

74LVC4245APW 74LVC4245ADH 24 TSSOP plastic SOT355-1

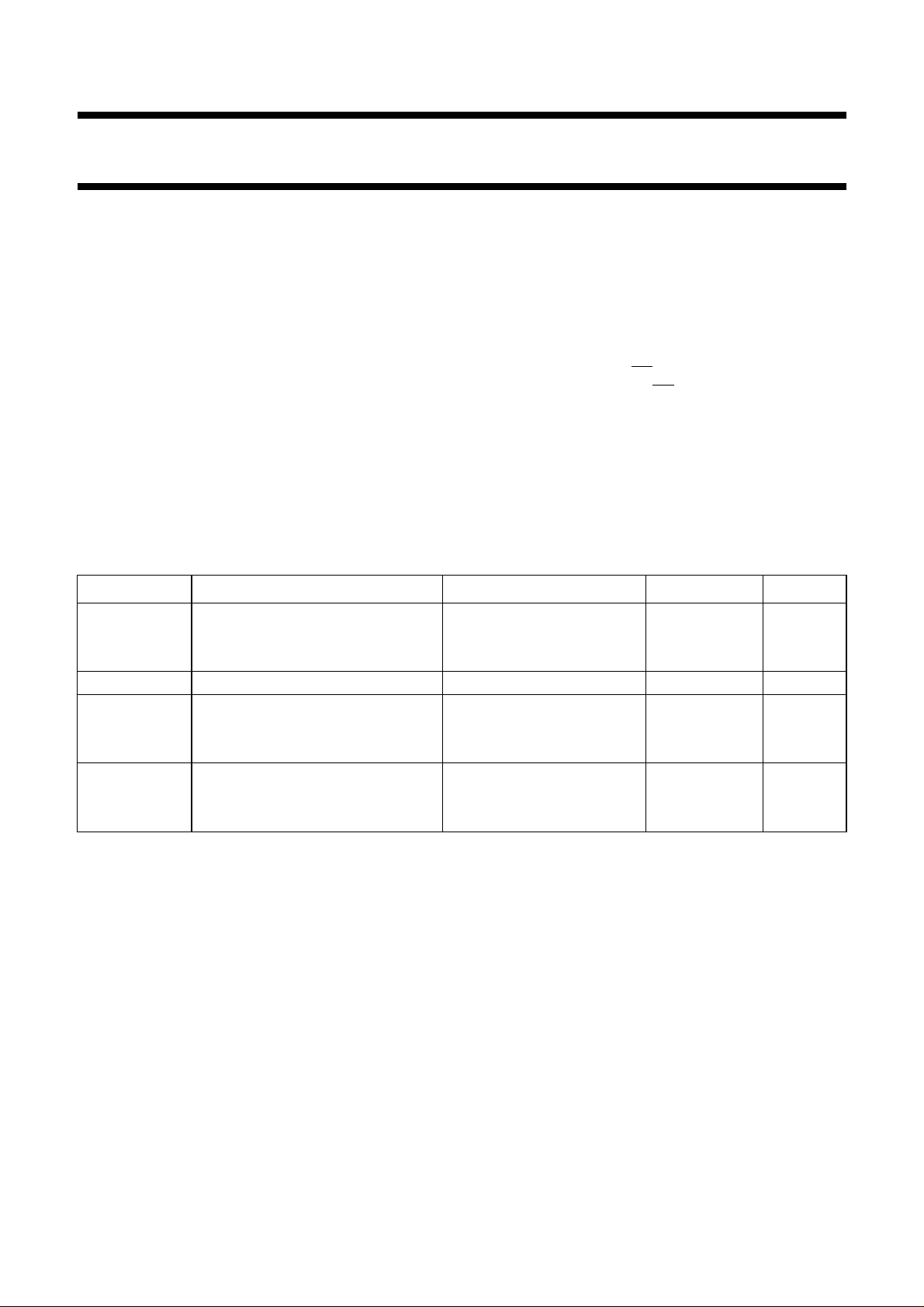

PINNING

PIN SYMBOL DESCRIPTION

1V

CCA

DC supply voltage (5 V bus)

2 DIR direction control

3, 4, 5, 6, 7, 8, 9 and 10 A

0

to A

7

data inputs/outputs

11, 12 and 13 GND ground (0 V)

14, 15, 16, 17, 18, 19, 20 and 21 B

22

23 and 24 V

7

to B

0

data inputs/outputs

OE output enable input (active LOW)

CCB

DC supply voltage (3 V bus)

1999 Jun 15 3

Philips Semiconductors Product specification

Octal dual supply translating transceiver; 3-state 74LVC4245A

handbook, halfpage

handbook, halfpage

V

1

CCA

2

DIR

A

3

0

A

4

1

A

5

2

A

6

A

A

A

A

GND

GND

3

4

5

6

7

4245

7

8

9

10

11

12

MNA451

Fig.1 Pin configuration.

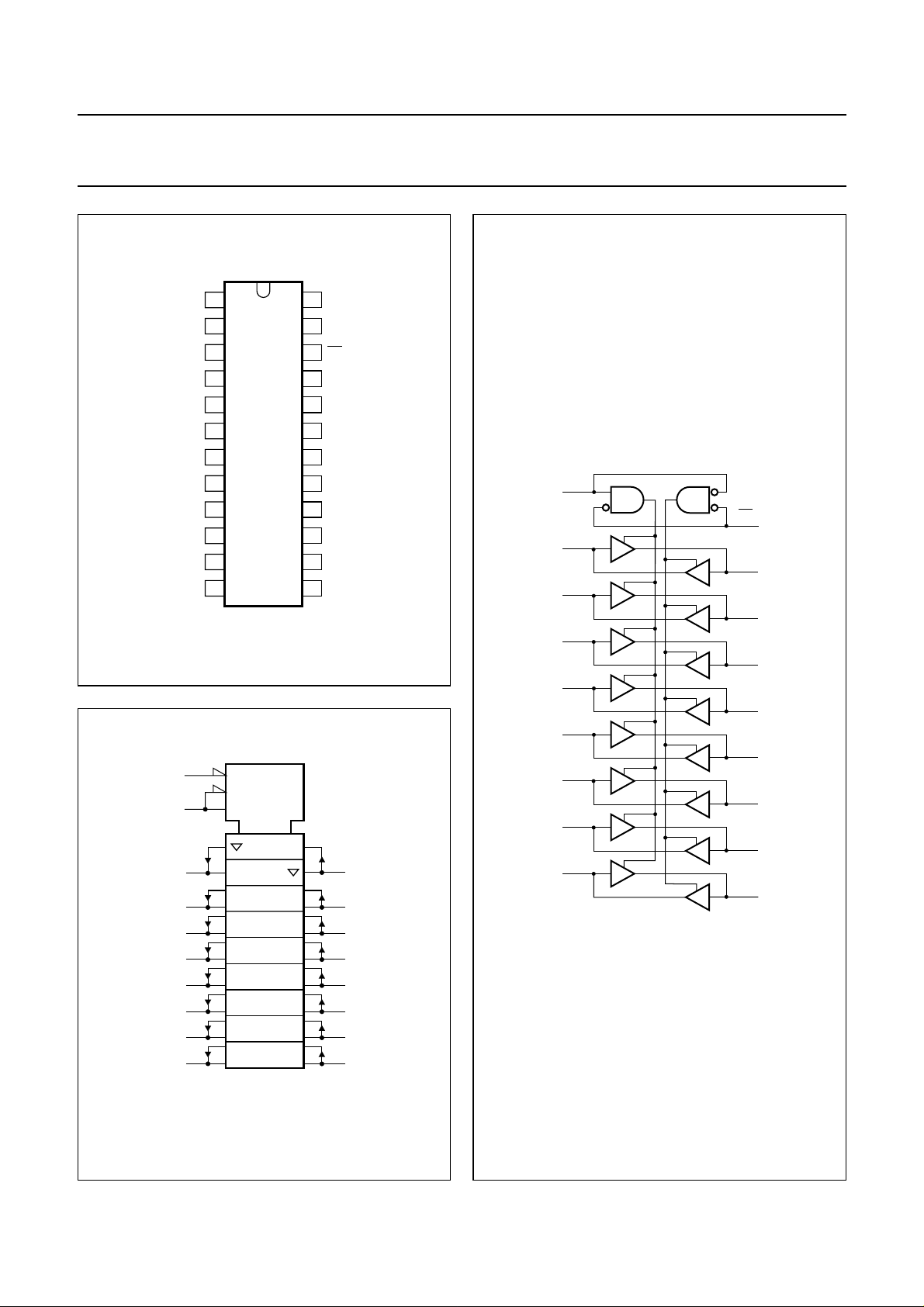

22

G3

3EN1

2

3EN2

1

3

4

5

6

7

8

9

10

2

MNA452

V

24

CCB

23

V

CCB

22

OE

21

B

0

20

B

1

19

B

2

18

B

3

17

B

4

16

B

5

15

B

6

14

B

7

13

GND

21

20

19

18

17

16

15

14

handbook, halfpage

10

DIR

2

OE

B

0

B

1

B

2

B

3

B

4

B

5

B

6

B

7

MNA453

22

21

20

19

18

17

16

15

14

A

0

3

A

1

4

A

2

5

A

3

6

A

4

7

A

5

8

A

6

9

A

7

Fig.3 IEC logic symbol.

1999 Jun 15 4

Fig.2 Logic symbol.

Philips Semiconductors Product specification

Octal dual supply translating transceiver; 3-state 74LVC4245A

RECOMMENDED OPERATING CONDITIONS

SYMBOL PARAMETER CONDITIONS

UNIT

MIN. MAX.

LIMITS

V

CCA

DC supply voltage 5 V port

V

CCA

≥ V

(see Fig.5) 1.5 5.5 V

CCB

(for maximum speed performance)

V

CCB

DC supply voltage 3 V port

V

CCA

≥ V

(see Fig.5) 1.5 3.6 V

CCB

(for low-voltage applications)

V

I

V

I/O

DC input voltage range (control inputs) 0 5.5 V

DC input voltage range; output 3-state 0 5.5 V

DC output voltage range; output HIGH or

0V

CC

V

LOW state

T

amb

operating ambient temperature range see DC and AC characteristics

−40 +85 °C

per device

t

r,tf

input rise and fall times V

= 2.7 to 3.0 V 0 20 ns/V

CCB

V

= 3.0 to 3.6 V 0 10

CCB

V

= 3.0 to 4.5 V 0 20

CCA

= 4.5 to 5.5 V 0 10

V

CCA

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to GND (ground = 0 V).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

V

I

V

I

V

CCA

CCB

IK

I

OK

I/O

DC supply voltage 5 V port −0.5 +6.5 V

DC supply voltage 3 V port −0.5 +4.6 V

DC input diode current VI<0 −−50 mA

DC input voltage note 1 −0.5 +6.5 V

DC output diode current VO>VCC or VO<0 −±50 mA

DC output voltage; output HIGH or LOW note 1 −0.5 VCC+ 0.5 V

DC input voltage; output 3-state note 1 −0.5 +6.5 V

I

O

I

GND

T

P

, I

stg

tot

DC output diode current VO=0toV

DC VCC or GND current −±100 mA

CC

CC

−±50 mA

storage temperature −65 +150 °C

power dissipation per package

plastic mini-pack (SO) above 70 °C derate linearly

− 500 mW

with 8 mW/K

plastic shrink mini-pack (SSOP and

TSSOP)

above 60 °C derate linearly

with 5.5 mW/K

− 500 mW

Note

1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

1999 Jun 15 5

Loading...

Loading...