INTEGRATED CIRCUITS

74LVC374A

Octal D-type flip-flop with 5-volt tolerant

inputs/outputs; positive edge-trigger

(3-State)

Product specification 1998 Jul 29

Philips Semiconductors Product specification

Octal D-type flip-flop with 5-volt tolerant

inputs/outputs; positive edge-trigger (3-State)

FEA TURES

•5-volt tolerant inputs/outputs, for interfacing with 5-volt logic

•Supply voltage range of 2.7V to 3.6V

•Complies with JEDEC standard no. 8-1A

•CMOS low power consumption

•Direct interface with TTL levels

•High impedance when V

CC

= 0V

•8-bit positive edge-triggered register

•Independent register and 3-State buffer operation

DESCRIPTION

The 74LVC374A is a high-performance, low-power, low-voltage,

Si-gate CMOS device, superior to most advanced CMOS

compatible TTL families.

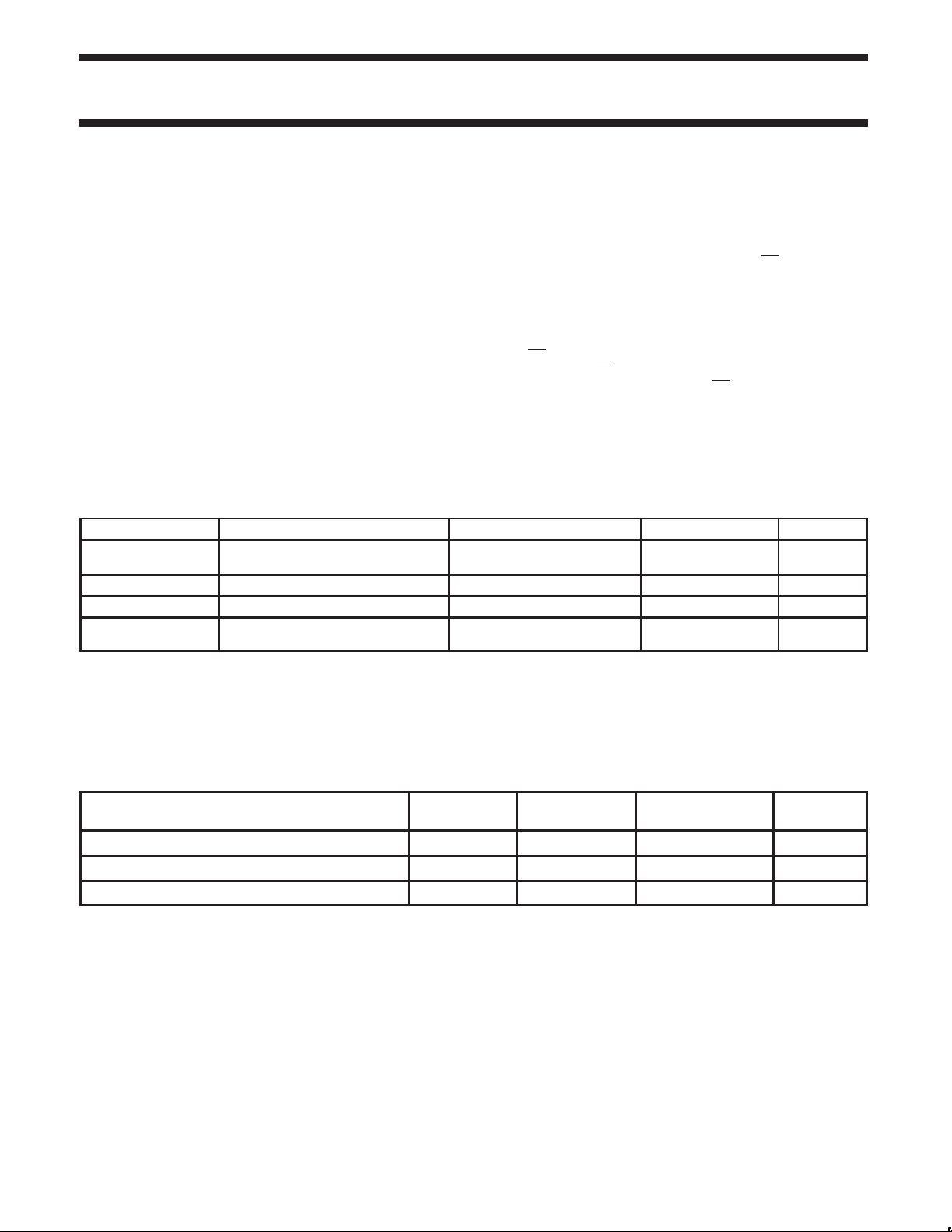

QUICK REFERENCE DATA

GND = 0V; T

SYMBOL

t

PHL/tPLH

f

max

C

I

C

PD

NOTE:

is used to determine the dynamic power dissipation (PD in W):

1. C

PD

= CPD x V

P

D

f

= input frequency in MHz; CL = output load capacity in pF;

i

= output frequency in MHz; VCC = supply voltage in V;

f

o

(C

2. The condition is V

=25°C; tr = tf 2.5ns

amb

2

CC

2

x V

x fo) = sum of outputs.

L

CC

PARAMETER CONDITIONS TYPICAL UNIT

Propagation delay

CP to Q

n

maximum clock frequency 150 MHz

Input capacitance 5.0 pF

Power dissipation capacitance per

flip-flop

x fi + (CL x V

= GND to V

I

CC

CC

2

x fo) where:

Inputs can be driven from either 3.3V or 5V devices. In 3-State

operation, outputs can handle 5V. This feature allows the use of

these devices as translators in a mixed 3.3V/5V environment.

The 74LVC374A is an octal D-type flip-flop featuring separate

D-type inputs for each flip-flop and 3-State outputs for bus-oriented

applications. A clock (CP) and an output enable (OE

common to all flip-flops.

The eight flip-flops will store the state of their individual D-inputs

that meet the setup and hold times requirements on the

LOW-to-HIGH CP transition.

When OE

the outputs. When OE

impedance OFF-state. Operation of the OE

state of the flip-flops.

The ’374’ is functionally identical to the ’574’, but the ’574’ has a

different pin arrangement.

CL = 50pF

VCC = 3.3V 4.8

Notes 1 and 2 20 pF

74L VC374A

) input are

is LOW, the contents of the eight flip-flops is available at

is HIGH, the outputs go to the high

input does not affect the

ns

ORDERING INFORMATION

PACKAGES

20-Pin Plastic Shrink Small Outline (SO) –40°C to +85°C 74LVC374A D 74LVC374A D SOT163-1

20-Pin Plastic Shrink Small Outline (SSOP) Type II –40°C to +85°C 74LVC374A DB 74LVC374A DB SOT339-1

20-Pin Plastic Thin Shrink Small Outline (TSSOP) Type I –40°C to +85°C 74LVC374A PW 7LVC374APW DH SOT360-1

1998 Jul 29 853-1861 19802

TEMPERATURE

RANGE

2

OUTSIDE

NORTH AMERICA

NORTH AMERICA PKG. DWG. #

Philips Semiconductors Product specification

Octal D-type flip-flop with 5-volt tolerant

inputs/outputs; positive edge-trigger (3-State)

PIN CONFIGURATION

V

1

OE

2

Q0

3

D0

4

D1

5

Q1

6

Q2

7

D2

8

D3

9

Q3 Q4

10 11

GND

PIN DESCRIPTION

PIN NUMBER SYMBOL FUNCTION

1 OE Output enable input (active-Low)

3, 4, 7, 8, 13,

14, 17, 18

2, 5, 6, 9, 12,

15, 16, 19

11 CP

10 GND Ground (0V)

20 V

D0-D7 Data inputs

Q0-Q7 3-state flip-flop outputs

CC

20

CC

Q7

19

D7

18

D6

17

Q6

16

Q5

15

D5

14

D4

13

12

CP

SA00389

Clock input (LOW-to-HIGH,

edge-triggered)

Positive supply voltage

LOGIC SYMBOL (IEEE/IEC)

11

1

32

4 5

7 6

89

13 12

14 15

17 16

18 19

C1

EN1

1D

FUNCTIONAL DIAGRAM

45

D1 Q1

89

D3 Q3

13

14 15

D5 Q5

18 19

D7 Q7

FF1

to

FF8

74LVC374A

SA00391

Q0D0

Q2D2

3-State

OUTPUTS

Q4D4

Q6D6

23

67

12

1617

LOGIC SYMBOL

13

14

17

18

1998 Jul 29

CP

11

1

11

CP

OE

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

1

2

5

6

9

12

15

16

19

SA00390

D0

3

D1

4

D2

7

D3

8

D4

D5

D6

D7

OE

SA00392

3

Philips Semiconductors Product specification

OPERATING MODES

INTERNAL FLIP-FLOPS

Octal D-type flip-flop with 5-volt tolerant

inputs/outputs; positive edge-trigger (3-State)

LOGIC DIAGRAM

D0

D

CP CP CP CP

FF1 FF2 FF3 FF4 FF5 FF6 FF7 FF8

CP

OE

D1

Q

Q0

D

D2

QQQ QQQQ

D

Q1 Q2 Q3 Q4 Q5 Q6 Q7

D3

D

74LVC374A

D4

D

CP CP CP CP

D5

D

D6

D

D7

D

SA00393

FUNCTION TABLE

INPUTS

OE LE D

Load and read register L

Load register and

disable outputs

L

H

H

°

°

°

°

H = HIGH voltage level

h = HIGH voltage level one setup time prior to the LOW-to-HIGH CP transition

L = LOW voltage level

l = LOW voltage level one setup time prior to the LOW-to-HIGH CP transition

Z = High impedance OFF-state

° = LOW-to-HIGH clock transition

n

l

h

l

h

OUTPUTS

Q0 to Q

7

L

H

L

H

L

H

Z

Z

1998 Jul 29

4

Loading...

Loading...