Philips 74LVCH32244A, 74LVC32244A Datasheet

INTEGRATED CIRCUITS

DATA SH EET

74LVC32244A; 74LVCH32244A

32-bit buffer/line driver; 5 V

input/output tolerant; 3-state

Product specification

File under Integrated Circuits, IC24

1999 Aug 31

Philips Semiconductors Product specification

32-bit buffer/line driver; 5 V input/output

tolerant; 3-state

FEATURES

• 5 V tolerant inputs/outputs for interfacing with 5 V logic

• Wide supply voltage range of 1.2 to 3.6 V

• CMOS low power consumption

• MULTIBYTE flow-trough standardpin-out architecture

• Low inductance multiple power and ground pins for

minimum noise and ground bounce

• Direct interface with TTL levels

• Bus hold on data inputs (74LVCH32244A only)

• Typical output ground bounce voltage:

V

<0.8 V at VCC= 3.3 V; T

OLP

• Typical output VOH undershoot voltage:

V

>2VatVCC= 3.3 V; T

OHV

• Power-off disabled outputs, permitting live insertion

• Plastic fine-pitch ball grid array package.

amb

amb

=25°C

=25°C

74LVC32244A;

74LVCH32244A

DESCRIPTION

The 74LVC(H)32244A is a high-performance, low-power,

low-voltage, Si-gate CMOS device, superior to most

advanced CMOS compatible TTL families. Inputs can be

driven from either 3.3 or 5 V devices. In 3-state operation,

outputs can handle 5 V. These features allow the use of

these devices in a mixed 3.3 and 5 V environment.

The 74LVC(H)32244A is a 32-bit non-inverting buffer/line

driver with 3-state outputs. The 3-state outputs are

controlled by the output enable inputs 1OE and 2OE.

A HIGH on input nOE causes the outputs to assume a

high-impedance OFF-state.

To ensure the high-impedance state during power-up or

power-down, input nOE should be tied to VCC through a

pull-up resistor; the minimum value of the resistor is

determined by the current-sinking capability of the driver.

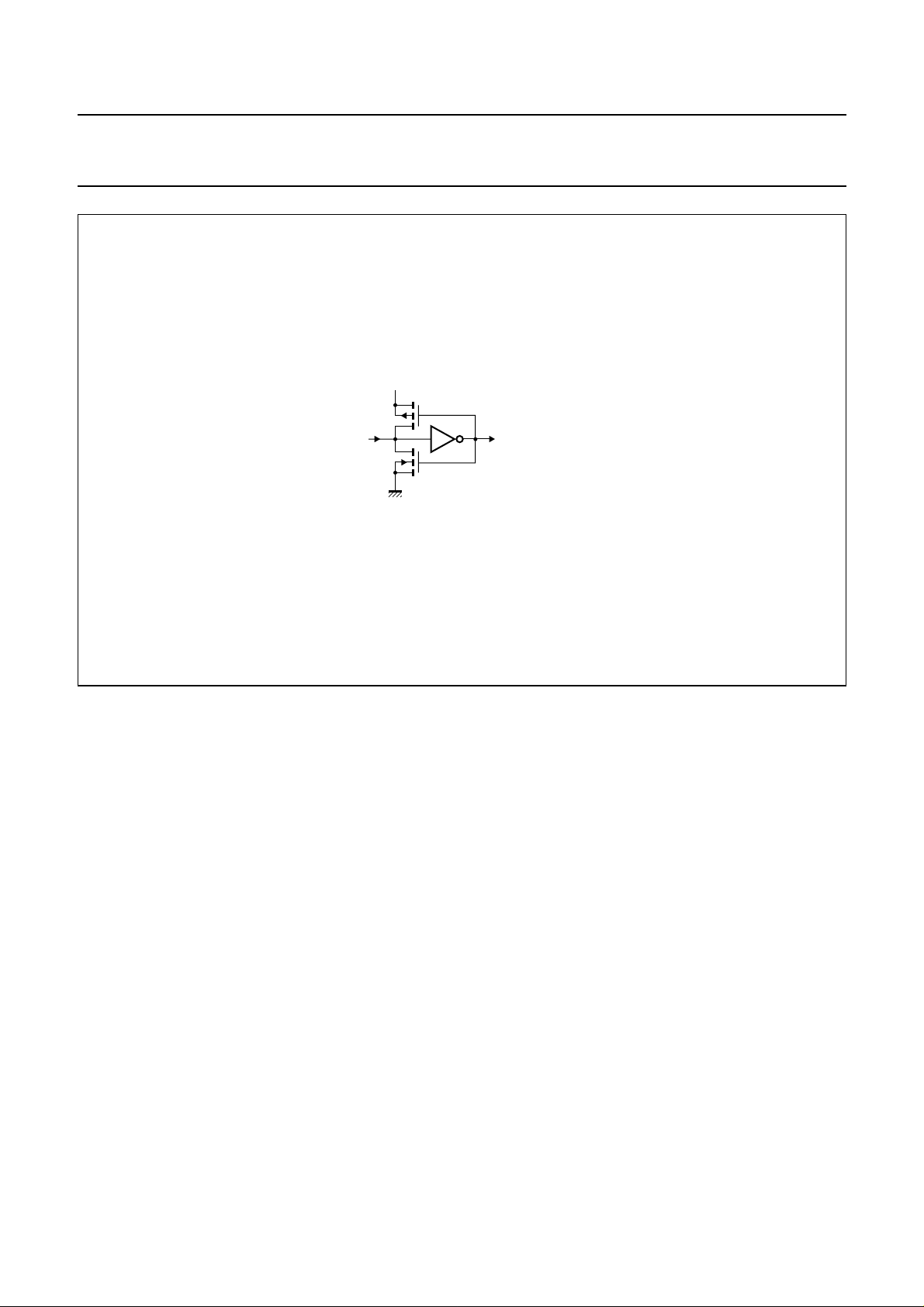

The 74LVCH32244A bus hold data input circuiteliminates

the need for external pull-up resistors to hold unused or

floating data inputs at a valid logic level (see Fig.3).

QUICK REFERENCE DATA

Ground = 0 V; T

=25°C; tr=tf≤2.5 ns.

amb

SYMBOL PARAMETER CONDITIONS TYPICAL UNIT

t

PHL/tPLH

C

I

C

PD

propagation delay nAnto nY

n

CL= 50 pF; VCC= 3.3 V 3.0 ns

input capacitance 5.0 pF

power dissipation capacitance per buffer VI= GND to VCC; note 1 25 pF

Note

1. C

is used to determine the dynamic power dissipation (PDin µW).

PD

PD=CPD× V

2

× fi+ Σ(CL× V

CC

2

× fo) where:

CC

fi= input frequency in MHz;

fo= output frequency in MHz;

CL= output load capacitance in pF;

= supply voltage in Volts;

V

CC

Σ(CL× V

2

× fo) = sum of the outputs.

CC

1999 Aug 31 2

Philips Semiconductors Product specification

32-bit buffer/line driver; 5 V input/output

tolerant; 3-state

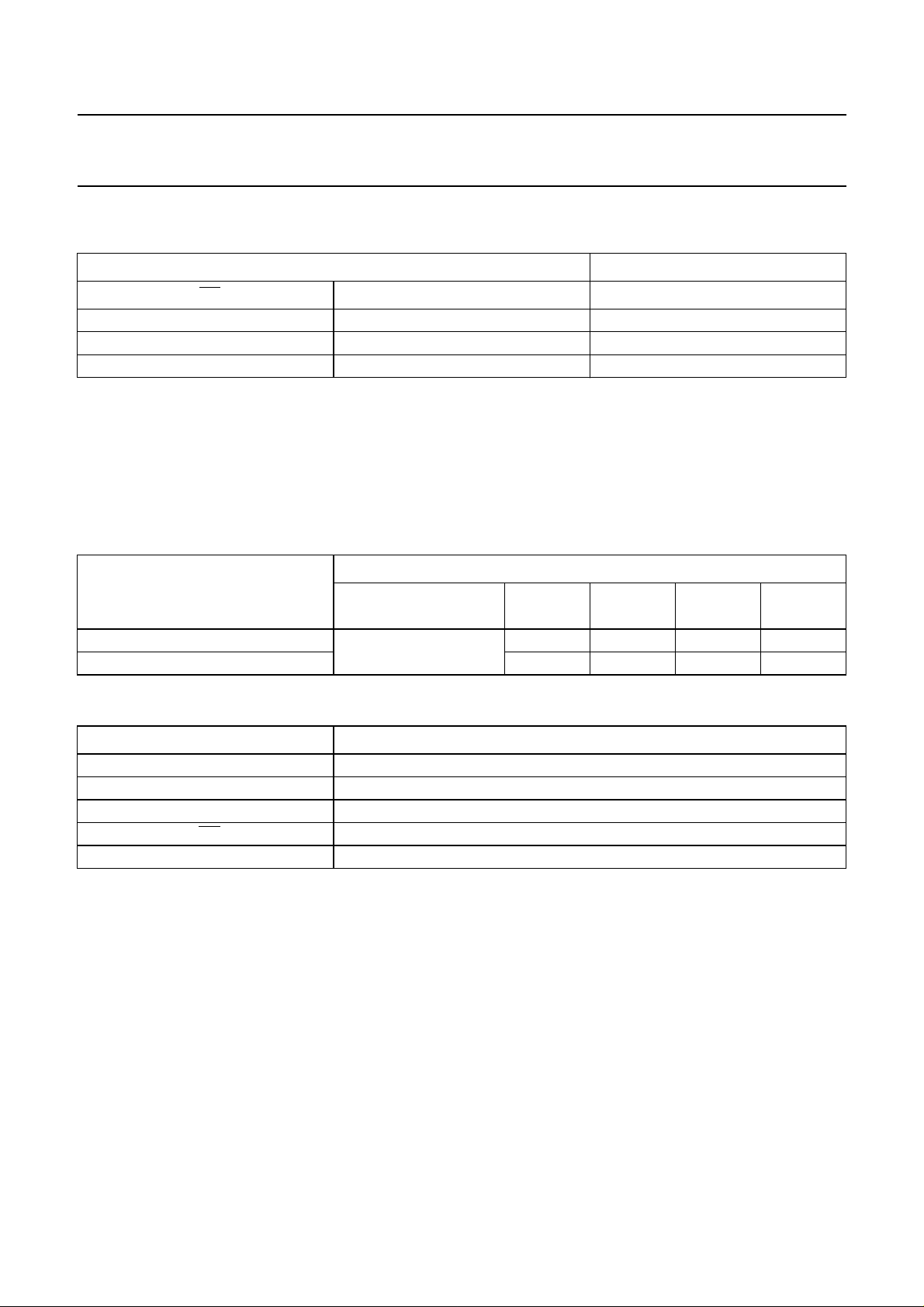

FUNCTION TABLE

See note 1.

INPUT OUTPUT

n

OE nA

LLL

LHH

HXZ

Note

1. H = HIGH voltage level;

L = LOW voltage level;

X = don’t care;

Z = high-impedance OFF-state.

ORDERING INFORMATION

TYPE NUMBER

74LVC32244AEC −40 to +85 °C 96 LFBGA96 plastic SOT536-1

74LVCH32244AEC 96 LFBGA96 plastic SOT536-1

TEMPERATURE

RANGE

n

PACKAGES

PINS PACKAGE MATERIAL CODE

74LVC32244A;

74LVCH32244A

nY

n

PINNING

SYMBOL DESCRIPTION

nA

n

nY

n

GND ground (0 V)

nOE 3-state output enable inputs (active LOW)

V

CC

data inputs

data outputs

DC supply voltage

1999 Aug 31 3

Philips Semiconductors Product specification

32-bit buffer/line driver; 5 V input/output

tolerant; 3-state

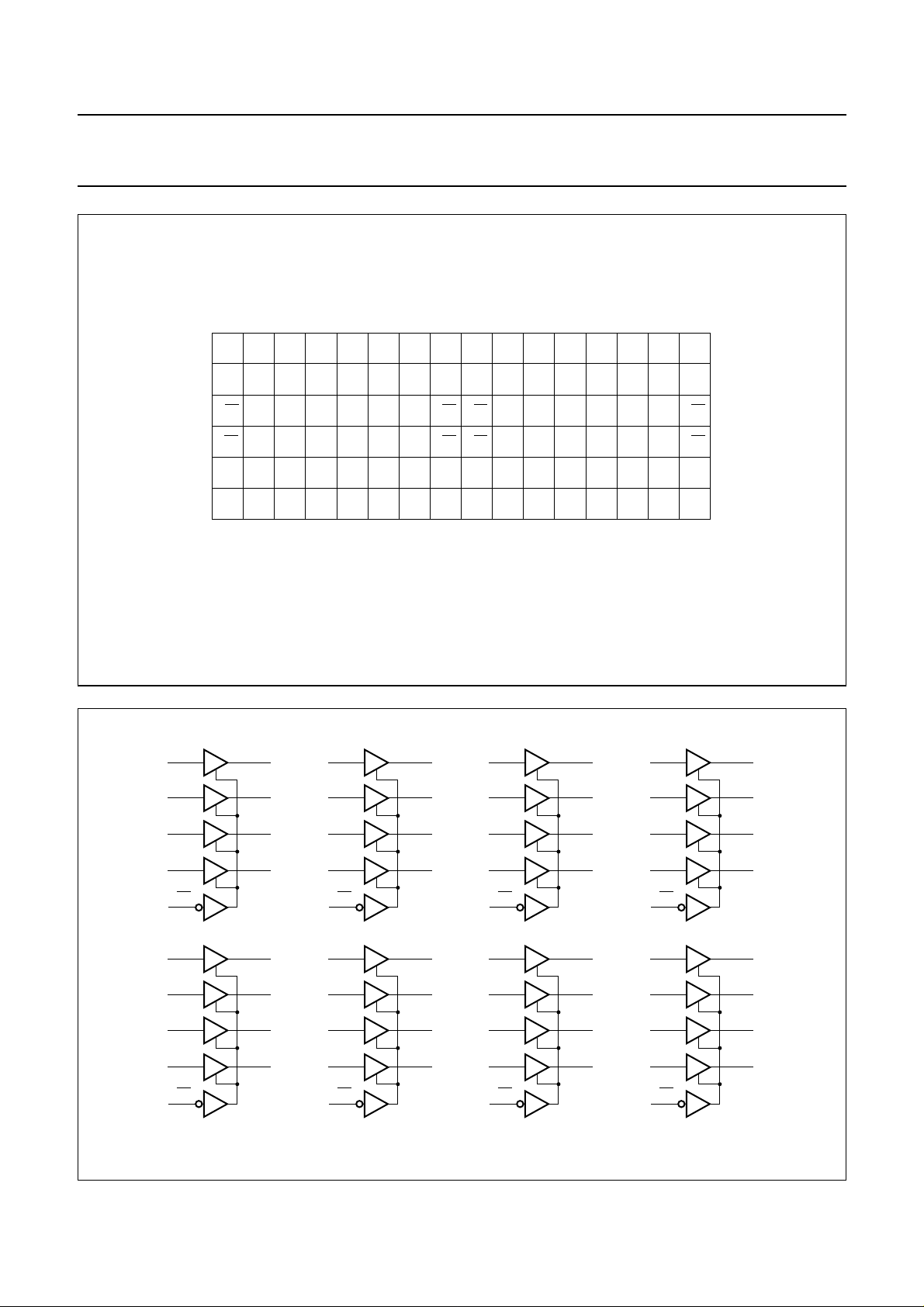

handbook, full pagewidth

6

1A11A32A12A33A13A34A14A25A15A36A16A37A17A38A18A

5

1A01A22A02A23A03A24A04A35A05A26A06A27A07A28A08A

2OE 3OE 6OEGND GND GND GND 7OEV

4

1OE

3 4OE 5OEGND GND GND GND 8OEV

1Y01Y22Y02Y23Y03Y24Y04Y35Y05Y26Y06Y27Y07Y28Y08Y

2

1Y11Y32Y12Y33Y13Y34Y14Y25Y15Y36Y16Y37Y17Y38Y18Y

1

AHJBDEG TCF KMNRLP

CC

CC

V

CC

V

CC

GND GND GND GNDV

GND GND GND GNDV

CC

CC

74LVC32244A;

74LVCH32244A

MNA471

2

3

V

CC

V

CC

3

2

handbook, full pagewidth

A5

A6

B5

B6

A3

C5

C6

D5

D6

A4

1A

1A

1A

1A

1OE

2A

2A

2A

2A

2OE

Fig.1 Pin configuration.

0

1

2

3

0

1

2

3

1Y

1Y

1Y

1Y

2Y

2Y

2Y

2Y

0

A2

1

A1

2

B2

3

B1

0

C2

1

C1

2

D2

3

D1

E5

E6

F5

F6

H4

G5

G6

H6

H5

H3

3A

3A

3A

3A

3OE

4A

4A

4A

4A

4OE

0

1

2

3

0

1

2

3

3Y

3Y

3Y

3Y

4Y

4Y

4Y

4Y

0

E2

1

E1

2

F2

3

F1

0

G2

1

G1

2

H1

3

H2

K5

K6

L5

L6

M5

M6

5A

0

J5

5A

1

J6

5A

2

5A

3

5OE

J3

6A

0

6A

1

6A

2

6A

3

6OE

J4

5Y

5Y

5Y

5Y

6Y

6Y

6Y

6Y

0

J2

1

J1

2

K2

3

K1

0

L2

1

L1

2

M2

3

M1

N5

N6

P5

P6

T4

R5

R6

T6

T5

T3

7A

7A

7A

7A

7OE

8A

8A

8A

8A

8OE

0

1

2

3

0

1

2

3

7Y

0

7Y

1

7Y

2

7Y

3

8Y

0

8Y

1

8Y

2

8Y

3

MNA472

N2

N1

P2

P1

R2

R1

T1

T2

Fig.2 Logic symbol.

1999 Aug 31 4

Philips Semiconductors Product specification

32-bit buffer/line driver; 5 V input/output

tolerant; 3-state

data

input

V

CC

handbook, halfpage

74LVC32244A;

74LVCH32244A

to internal circuit

MNA473

Fig.3 Bus hold circuit.

1999 Aug 31 5

Loading...

Loading...