Philips 74hc hct6323a DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT6323A

Programmable ripple counter with

oscillator; 3-state

Product specification

Supersedes data of December 1990

File under Integrated Circuits, IC06

September 1993

Philips Semiconductors Product specification

Programmable ripple counter with

oscillator; 3-state

FEATURES

• 8-pin space saving package

• Programmable 3-stage ripple

counter

• Suitable for over-tone crystal

application up to 50 MHz

(VCC=5V±10%)

• 3-state output buffer

• Two internal capacitors

• Recommended operating range for

use with third overtone crystals

3to6V

• Oscillator stop function (MR)

• Output capability:

bus driver → (15 LSTTL)

• ICC category: MSI.

APPLICATIONS

• Control counters

• Timers

• Frequency dividers

• Time-delay circuits

• CIO (Compact Integrated

Oscillator)

• Third-overtone crystal operation.

GENERAL DESCRIPTION

The HC/HCT6323A are high-speed

Si-gate CMOS devices.

They are specified in compliance with

JEDEC standard no. 7A.

The HC/HCT6323A are oscillators

designed for quartz crystal combined

with a programmable 3-state counter,

a 3-state output buffer and an

overriding asynchronous master

MR). With the two select inputs

reset (

S1 and S2 the counter can be

switched in the divide-by-1, 2, 4 or 8

mode. If left floating the clock is

divided by 8. The oscillator is

designed to operate either in the

fundamental or third overtone mode

depending on the crystal and external

components applied. On-chip

capacitors minimize external

component count for third overtone

crystal applications.

The oscillator may be replaced by an

external clock signal at input X1. In

this event the other oscillator pin (X2)

must be floating. The counter

advances on the negative-going

transition of X1. A LOW level on

resets the counter, stops the oscillator

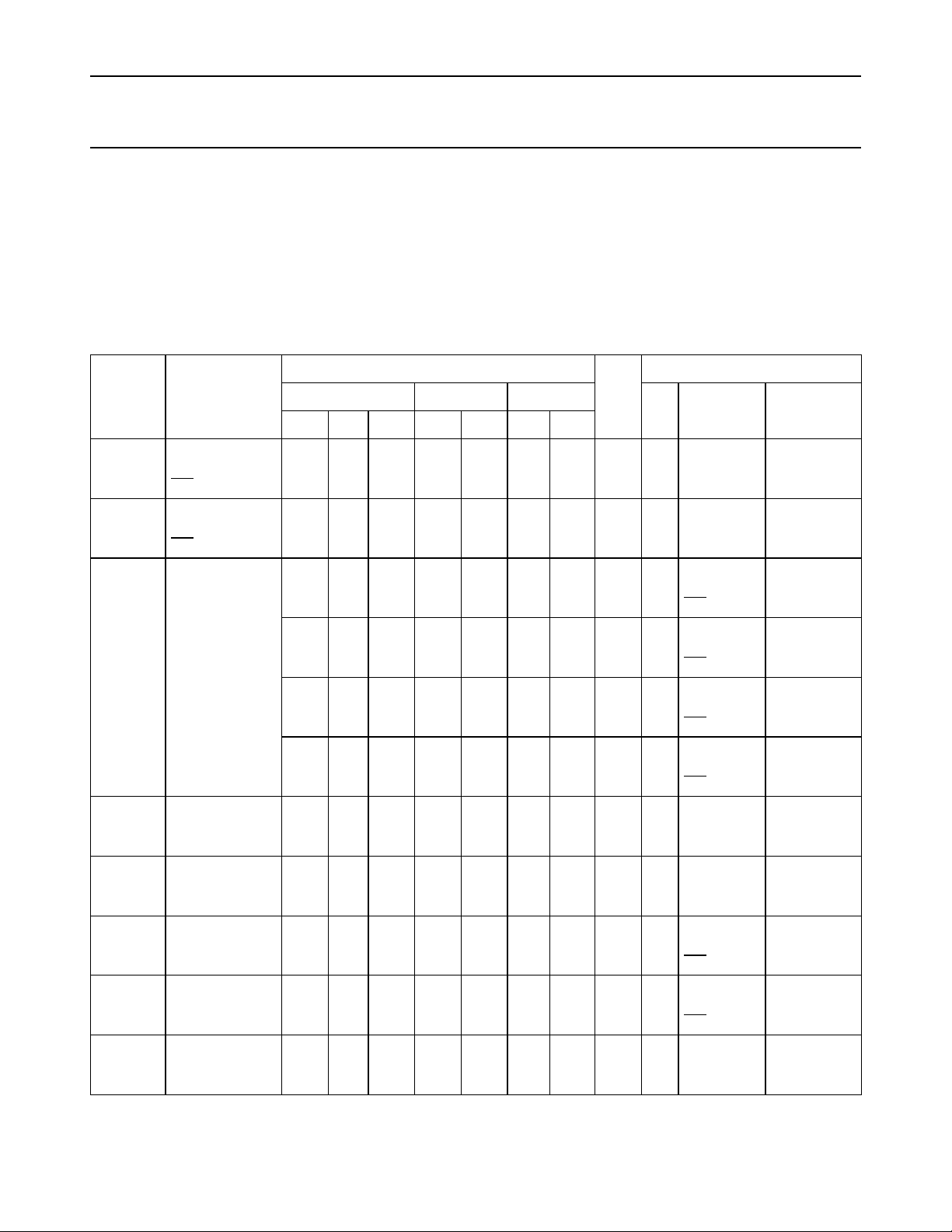

QUICK REFERENCE DATA

GND = 0 V; T

SYMBOL PARAMETER CONDITIONS

t

PHL/tPLH

f

max

C

I

C

PD

Notes

1. C

is used to determine the dynamic power dissipation (PD in µW):

PD

PD = (CPD x V

where:

fi = input frequency in MHz; fo = output frequency in MHz.

VCC = supply voltage in V; CL = output load capacitance in pF.

I

pull-up

2. For HC and HCT an external clock is applied to X1 with:

tr = tf≤ 6 ns, Vi is GND to VCC, MR = HIGH

I

pull-up

ORDERING INFORMATION

EXTENDED TYPE

NUMBER

74HC/HCT6323AD 8 SO plastic SOT96

74HC/HCT6323A

and sets the output buffer in the

3-state condition. MR can be left

floating since an internal pull-up

resistor will make the MR inactive. In

the HCT version, the MR input and

the two mode select pins S1 and S2

are TTL compatible, but the X1 input

has CMOS input switching levels and

MR

= 25 °C; tr = tf = 6 ns.

amb

propagation delay

X1 to OUT

(S1 = S2 = LOW)

maximum clock

frequency

input capacitance

except X1 and X2

power dissipation

capacitance per

package

2

x fi) + (CL + V

CC

= pull-up currents in µA.

is the summation of −II (µA) of S1 and S2 inputs at the LOW state.

PINS PIN POSITION MATERIAL CODE

may be driven by a TTL output using

a pull-up resistor connected to VCC.

TYP.

HC HCT

CL = 15 pF;

17 17 ns

VCC = 5 V

90 90 MHz

3.5 3.5 pF

+1; notes 1 and 2 54 54 pF

+2; notes 1 and 2 42 42 pF

+4; notes 1 and 2 36 36 pF

+8; notes 1 and 2 33 33 pF

2

CC

x fo) + (I

pull-up

x VCC)

PACKAGE

UNIT

September 1993 2

Philips Semiconductors Product specification

Programmable ripple counter with

oscillator; 3-state

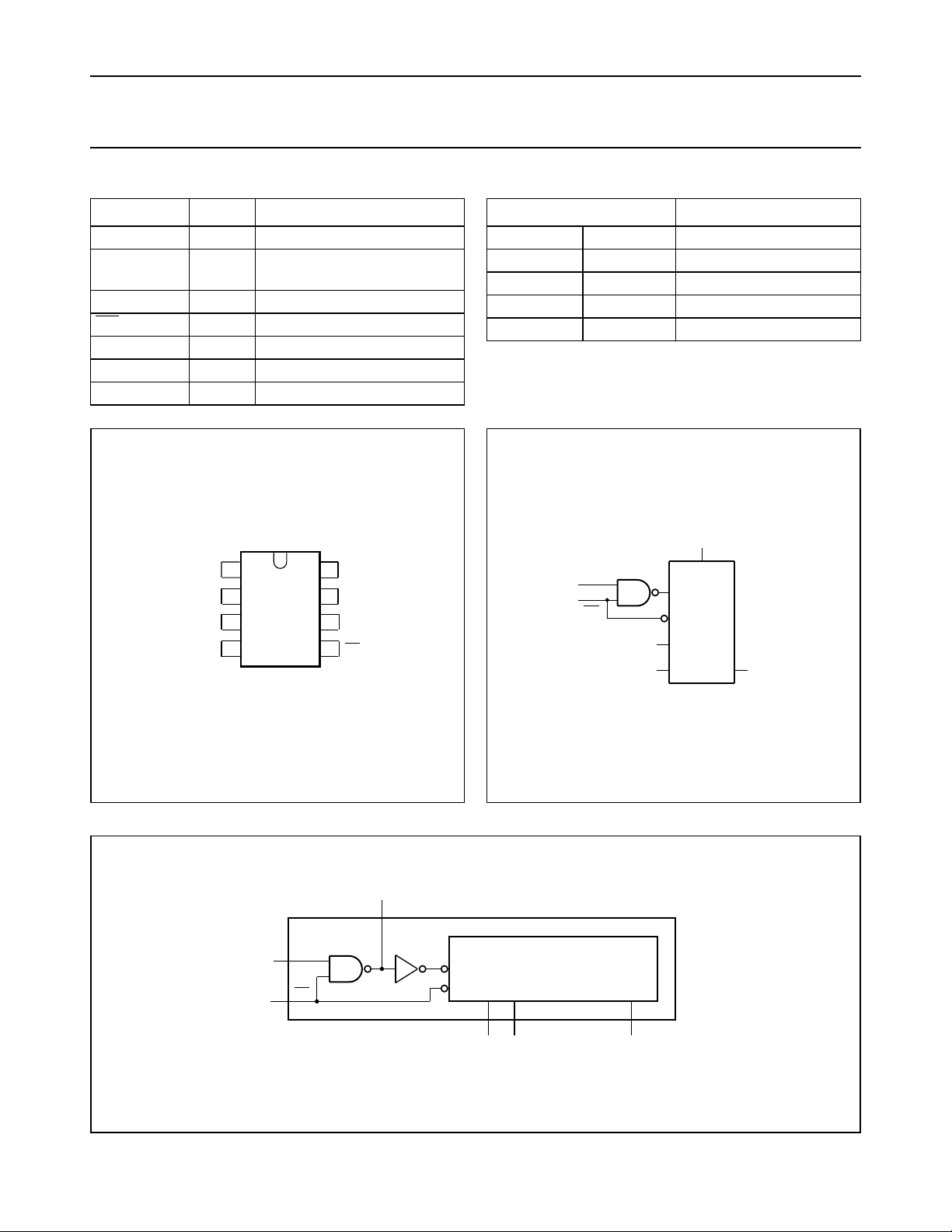

PINNING

SYMBOL PIN DESCRIPTION

OUT 1 counter output

S1 - S2 3, 2 mode select inputs for divide

by 1, 2, 4 or 8

GND 4 ground (0 V)

MR 5 master reset (active LOW)

X2 6 oscillator pin

X1 7 clock input/oscillator pin

V

CC

handbook, halfpage

8 positive supply

1

OUT

2

S2

6323A

3

S1

GND

4

MBA343

V

8

CC

X1

7

X2

6

5

MR

74HC/HCT6323A

FUNCTION TABLE

INPUTS OUTPUTS

S1 S2 OUT

00 f

01 f

10 f

11 f

handbook, halfpage

X1

7

5

MR

3

21

6

X2

CP

C

D

S1

OUT

S2

MBA344

i

/2

i

/4

i

/8

i

Fig.1 Pin configuration.

6

handbook, full pagewidth

7

5

X1

MBA350

X2

CP

C

D

Fig.3 Functional diagram.

September 1993 3

Fig.2 IEC logic symbol.

3 - STAGE BINARY COUNTER

AND DECODER

OUTS1 S2MR

32 1

Philips Semiconductors Product specification

Programmable ripple counter with

oscillator; 3-state

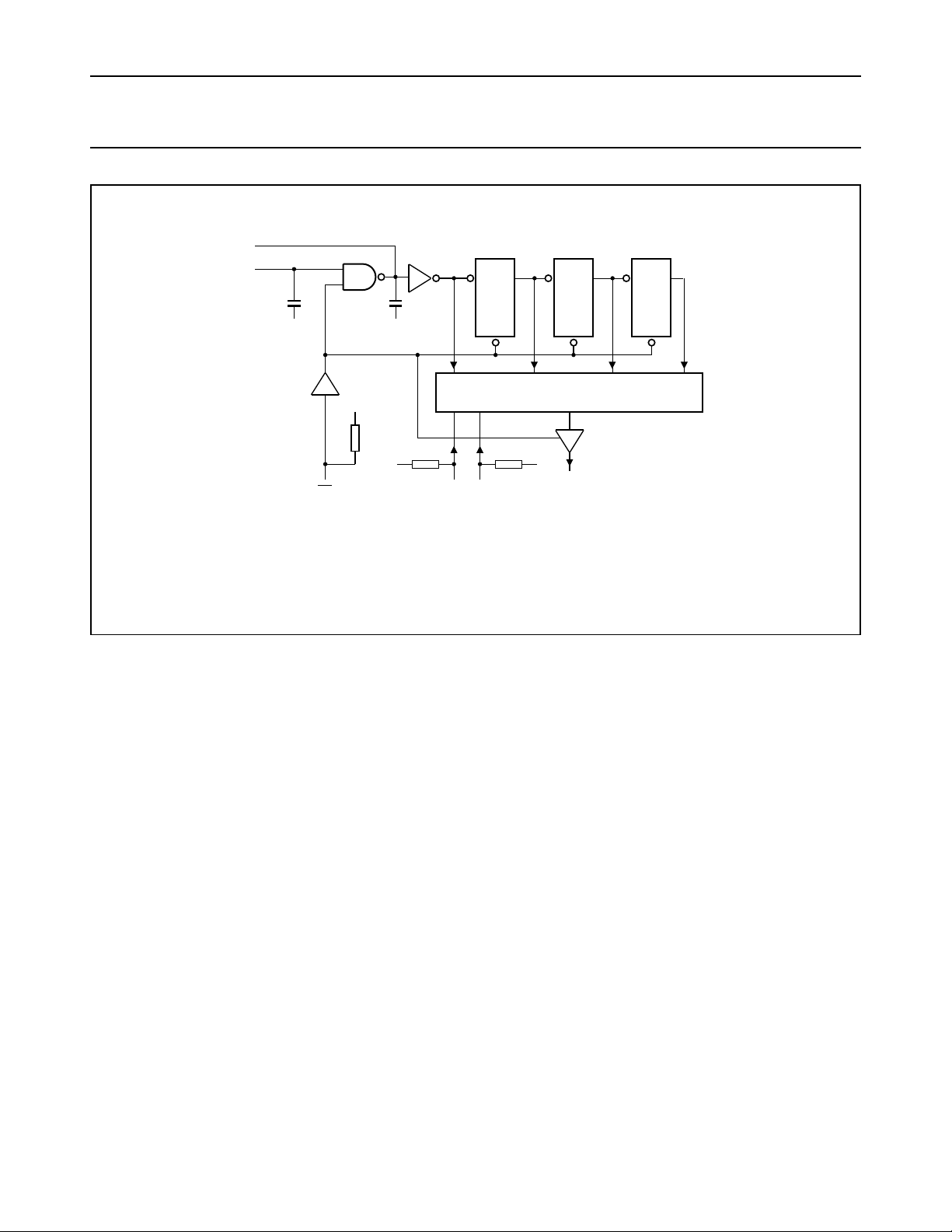

handbook, full pagewidth

Internal capacitors typical 7 pF each. Including

stray capacitors on pin X1 and X2, total capacitance

will be typical 12 pF per pin.

X2

X1

7 pF

MR

7 pF

V

CC

V

CC

V

CC

(1)

V

CC

74HC/HCT6323A

QCP

S1 S2

FF

R

V

CC

(1)

QCP

FF

R

DECODER

OUT

QCP

FF

R

MBA349

Fig.4 Logic diagram.

September 1993 4

Philips Semiconductors Product specification

Programmable ripple counter with

oscillator; 3-state

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see

Output capability: non-standard; bus driver (except for X2)

ICC category: MSI.

Voltages are referenced to GND (ground = 0 V).

DC CHARACTERISTICS FOR 74HC

SYMBOL PARAMETER

V

IH

HIGH level

input voltage

MR, X1 input

V

IL

LOW level

input voltage

MR, X1 input

V

OH

HIGH level

output voltage

X2 output

V

OH

HIGH level

output voltage

OUT

V

OH

HIGH level

output voltage

OUT

V

OL

LOW level

output voltage

X2 output

V

OL

LOW level

output voltage

OUT

“74HC/HCT/HCU/HCMOS Logic Family Specifications”

(°C)

T

amb

25 −40 to 85 −40 to 125

MIN TYP MAX MIN MAX MIN MAX

1.5

3.15

4.2

−

−

−

3.98

5.48−−

3.98

5.48−−

1.9

4.4

5.9

1.9

4.4

5.9

1.9

4.4

5.9

3.98

5.48−−

−

−

−

−

−

−

−

−

1.2

2.4

3.2

0.8

2.1

2.8

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

−

−

0

0

0

0

0

0

−

−

−

0.5

1.35

1.80

−

−

−

−

−

−

−

−

−

−

−

−

−

−

−

0.26

0.26−−

0.1

0.1

0.1

0.1

0.1

0.1

1.5

3.15

4.2

−

−

−

3.84

5.34−−

3.84

5.34−−

1.9

4.4

5.9

1.9

4.4

5.9

1.9

4.4

5.9

3.84

5.34−−

−

−

−

−

−

−

−

−

−

0.5

1.35

1.8

−

−

−

−

−

−

−

−

−

0.33

0.33−−

0.1

0.1

0.1

0.1

0.1

0.1

1.50

3.15

4.20

−

−

−

3.7

5.2−−

3.7

5.2−−

1.9

4.4

5.9

1.9

4.4

5.9

1.9

4.4

5.9

3.7

5.2−−

−

−

−

−

−

−

−

−

−

0.5

1.35

1.8

−

−

−

−

−

−

−

−

−

0.4

0.4VV

0.1

0.1

0.1

0.1

0.1

0.1

UNIT

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

74HC/HCT6323A

.

TEST CONDITION

V

CC

(V)

2.0

4.5

6.0

2.0

4.5

6.0

4.5

6.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

4.5

6.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

V

I

X1 = GND

and

MR = V

X1 = V

CC

CC

and

MR = GND

X1 = GND

and

MR = V

X1 = V

CC

CC

and

MR = GND

VIH or V

VIH or V

X1 = V

ILIO

ILIO

CC

and

MR = V

X1 = V

CC

CC

and

MR = V

VIH or V

CC

ILIO

IO = −2.6 mA

IO = −3.3 mA

IO = −2.6 mA

IO = −3.3 mA

−IO = 20 µA

IO = −20 µA

IO = −20 µA

IO = −20 µA

IO = −20 µA

IO = −20 µA

IO = −20 µA

IO = −20 µA

IO = −7.8 mA

IO = 2.6 mA

IO = 3.3 mA

IO = 20 µA

IO = 20 µA

IO = 20 µA

IO = 20 µA

IO = 20 µA

OTHER

= −20 µA

= −6 mA

= 20 µA

September 1993 5

Loading...

Loading...