Philips 74hc hct40104 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT40104

4-bit bidirectional universal shift

register; 3-state

Product specification

File under Integrated Circuits, IC06

December 1990

Philips Semiconductors Product specification

4-bit bidirectional universal shift

register; 3-state

FEATURES

• Synchronous parallel or serial operating

• 3-state outputs

• Output capability: bus driver

• ICCcategory: MSI

GENERAL DESCRIPTION

The 74HC/HCT40104 are high-speed Si-gate CMOS

devices and are pin compatible with the “40104” of the

“4000B” series. They are specified in compliance with

JEDEC standard no. 7A.

The 74HC/HCT40104 are universal shift registers

featuring parallel inputs, parallel outputs, shift-right and

shift-left serial inputs and 3-state outputs allowing the

devices to be used in bus-organized systems.

74HC/HCT40104

In the parallel-load mode (S

loaded into the associated flip-flop and appears at the

output after the positive transition of the clock input (CP).

During loading, serial data flow is inhibited. Shift-right and

shift-left are accomplished synchronously on the positive

clock edge with serial data entered at the shift-right (DSR)

and shift-left (DSL) serial inputs, respectively.

Clearing the register is accomplished by setting both mode

controls (S0and S1) LOW and clocking the register. When

the output enable input (OE) is LOW, all outputs assume

the high-impedance OFF-state (Z).

APPLICATIONS

• Arithmetic unit bus registers

• Serial/parallel conversion

• General-purpose register for bus organized systems

• General-purpose registers

and S1 are HIGH), data is

0

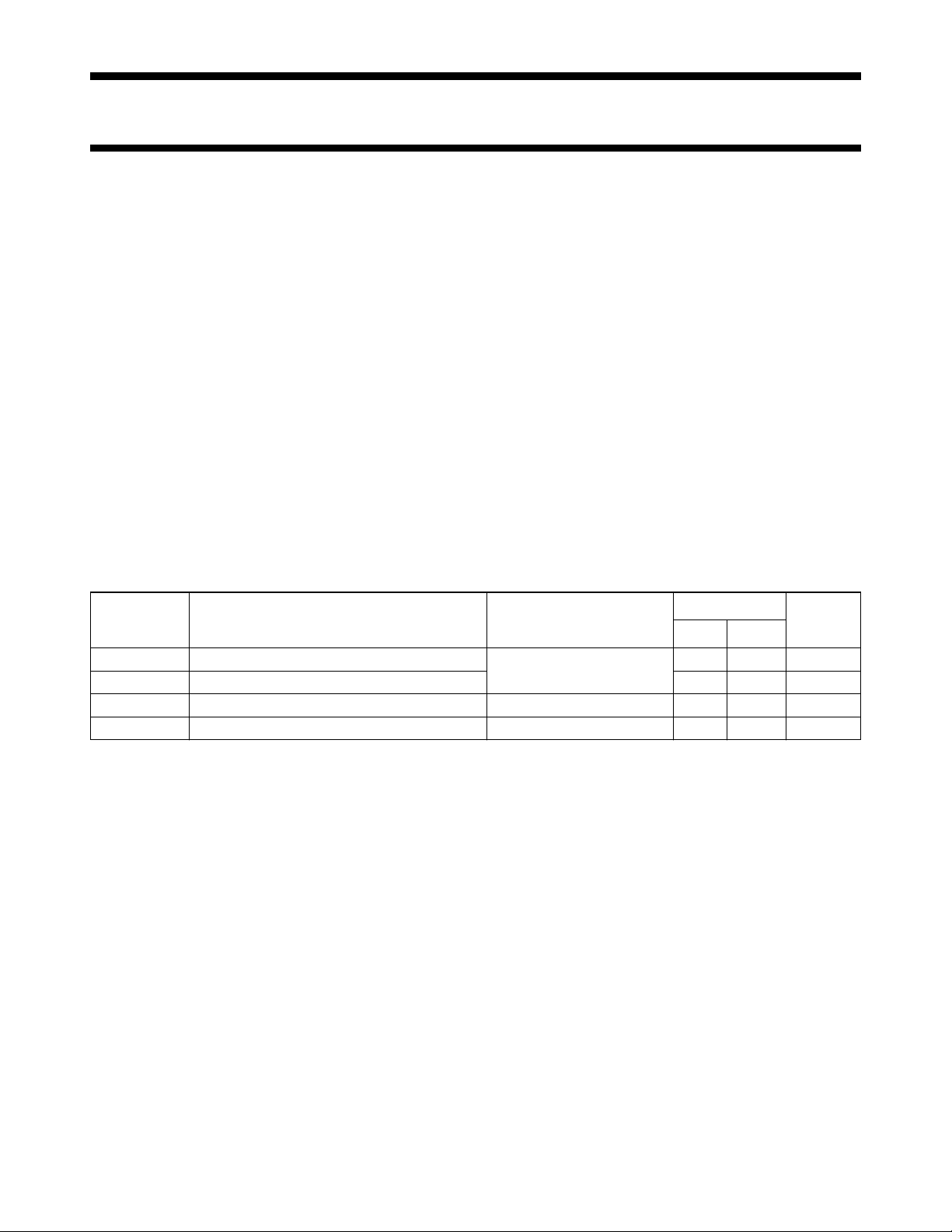

QUICK REFERENCE DATA

GND = 0 V; T

=25°C; tr=tf= 6 ns

amb

SYMBOL PARAMETER CONDITIONS

t

PHL

f

max

C

C

I

PD

/ t

PLH

propagation delay CP to Q

n

CL= 15 pF; VCC= 5 V 13 15 ns

maximum clock frequency 62 57 MHz

input capacitance 3.5 3.5 pF

power dissipation capacitance per package notes 1 and 2 75 75 pF

Notes

1. C

is used to determine the dynamic power dissipation (PDin µW):

PD

PD=CPD× V

2

× fi+∑(CL× V

CC

2

× fo) where:

CC

fi= input frequency in MHz

fo= output frequency in MHz

∑ (CL× V

2

× fo) = sum of outputs

CC

CL= output load capacitance in pF

VCC= supply voltage in V

2. For HC the condition is VI= GND to V

CC

For HCT the condition is VI= GND to VCC− 1.5 V

TYPICAL

UNIT

HC HCT

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

December 1990 2

.

Philips Semiconductors Product specification

4-bit bidirectional universal shift register;

3-state

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1 OE 3-state output enable input (active HIGH)

2D

3, 4, 5, 6 D

7D

SR

0

SL

to D

3

8 GND ground (0 V)

9, 10 S

, S

0

1

11 CP clock input (LOW-to-HIGH, edge-triggered)

15, 14, 13, 12 Q

16 V

0

CC

to Q

3

serial data shift-right input

parallel data inputs

serial data shift-left input

mode control inputs

3-state parallel outputs

positive supply voltage

74HC/HCT40104

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

December 1990 3

Loading...

Loading...