Philips 74f756, 74f757, 74f 760 DATASHEETS

INTEGRATED CIRCUITS

74F756

Octal inverter buffer (open-collector)

74F757

Octal buffer (open-collector)

74F760

Octal buffer (open-collector)

Product specification

IC15 Data Handbook

1989 Nov 27

Philips Semiconductors Product specification

Buffers

74F756/74F757/74F760

74F756 Octal Inverter Buffer (Open Collector)

74F757 Octal Buffer (Open Collector)

74F760 Octal Buffer (Open Collector)

FEA TURES

•Octal bus interface

•Open collector versions of 74F240, 74F241 and 74F244

DESCRIPTION

The 74F756, 74F757 and 74F760 are octal buffers that are ideal for

driving bus lines of buffer memory address registers. The 74F756 is

the open collector version of 74F240, 74F757 is the open collector

version of 74F241 and 74760 is the open collector version of

74F244. These devices feature two Output Enables. OE

(or OEb for the 74F757), each controlling four of the outputs.

a and OEb

TYPE

74F756 9.0ns 40mA

74F757 9.0ns 45mA

74F760 9.0ns 45mA

ORDERING INFORMATION

ORDER CODE

DESCRIPTION COMMERCIAL RANGE

20–pin plastic DIP N74F756N, N74F757AN, N74F760N SOT146-1

20–pin plastic SOL N74F756D, N74F757AD, N74F760D SOT163-1

VCC = 5V ±10%, T

= 0°C to +70°C

amb

TYPICAL

PROPAGATION DELAY

TYPICAL SUPPL Y

CURRENT (TOTAL)

PKG DWG #

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

PINS DESCRIPTION

Ian, Ibn Data inputs 1.0/1.67 20µA/1.0mA

OEa, OEb Output enable input (active Low) 1.0/1.67 20µA/0.2mA

OEb Output enable input (active High 74F757) 1.0/1.67 20µA/1.0mA

Yan, Ybn Data outputs (74F757, 74F760) OC/106.7 OC/64mA

Yan, Ybn Data outputs (74F756) OC/106.7 OC/64mA

Notes:

One (1.0) FAST unit load is defined as: 20µA in the high state and 0.6mA in the Low state.

OC=Open Collector

74F (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

1989 Nov 27 853–0270 98220

2

Philips Semiconductors Product specification

74F756/74F757/74F760Buffers

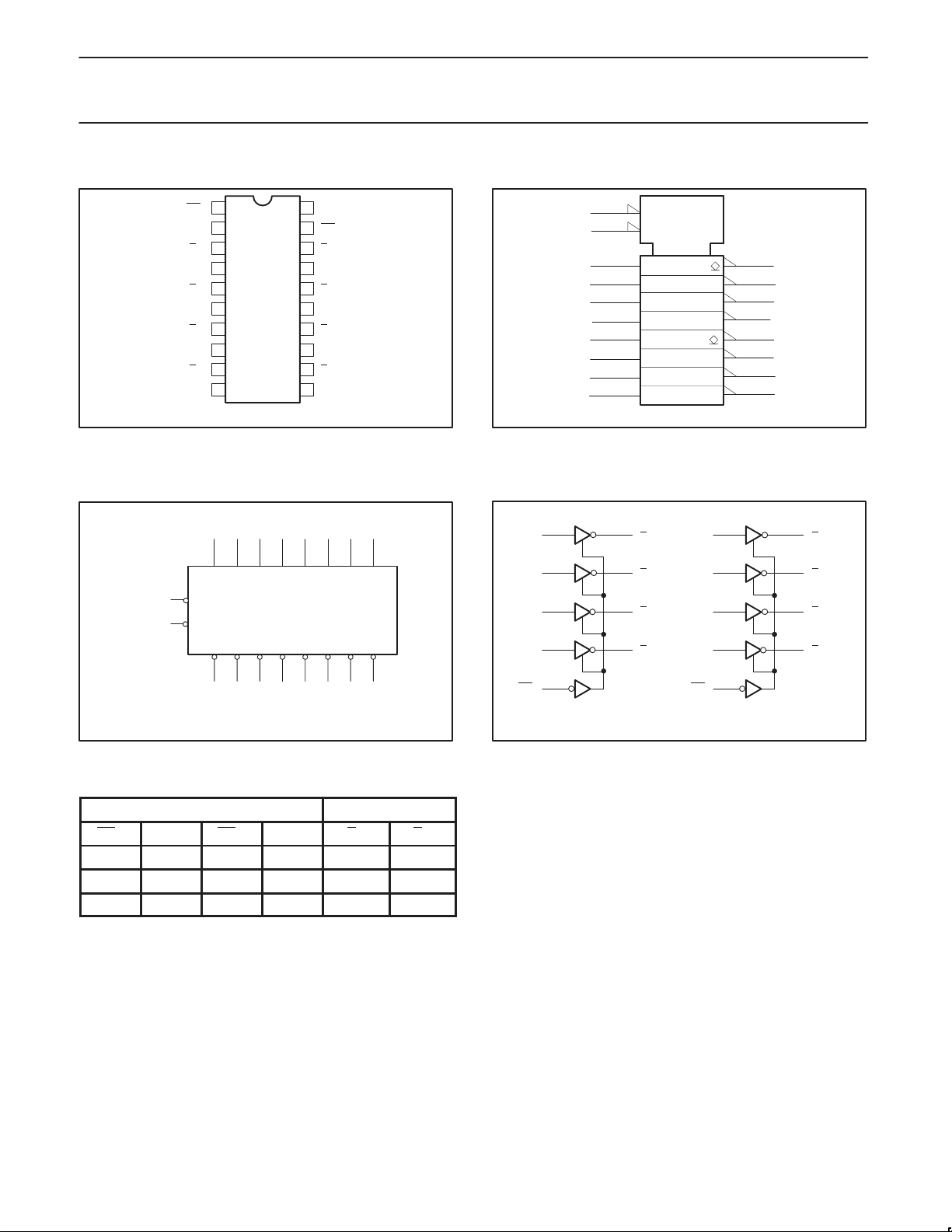

PIN CONFIGURATION for 74F756

1

OEa

2

Ia0

3

Yb0

4

Ia1

5

Y

b1

6

Ia2

7

Y

b2

8

Ia3

9

Yb3

10 11

GND

20

19

18

17

16

15

14

13

12

SF00320

LOGIC SYMBOL for 74F756

2 4 6 8 17 15 13 11

Ia0 Ia1 Ia2 Ia3 Ib0 Ib1 Ib2 Ib3

119OEa

OEb

Ya0 Ya1 Ya2 Ya3 Yb0 Yb1 Yb2 Yb3

V

OEb

Y

Ib0

Y

Ib1

Y

Ib2

Ya3

Ib3

IEC/IEEE SYMBOL for 74F756

CC

a0

a1

a2

1

19

2

4

6

8

17

15

13

11

EN1

EN2

1

2

18

16

14

12

3

5

7

9

SF01246

LOGIC DIAGRAM for 74F756

Ia0

Ia1

Ia2

Ia3

2

4

6

8

18

Y

a0

16

a1

Y

14

a2

Y

12

Y

a3

Ib0

Ib1

Ib2

Ib3

17

15

13

11

3

Y

b0

5

b1

Y

7

b2

Y

9

Y

b3

181614123579

VCC = Pin 20

GND = Pin 10

SF00321

FUNCTION TABLE for 74F756

INPUTS OUTPUTS

OEa Ia OEb Ib Ya Yb

L L L L H H

L H L H L L

H X H X H (off) H (off)

H = High voltage level

L = Low voltage level

X = Don’t care

OEb

VCC = Pin 20

GND = Pin 10

1

OE

19

b

SF01247

1989 Nov 27

3

Philips Semiconductors Product specification

74F756/74F757/74F760Buffers

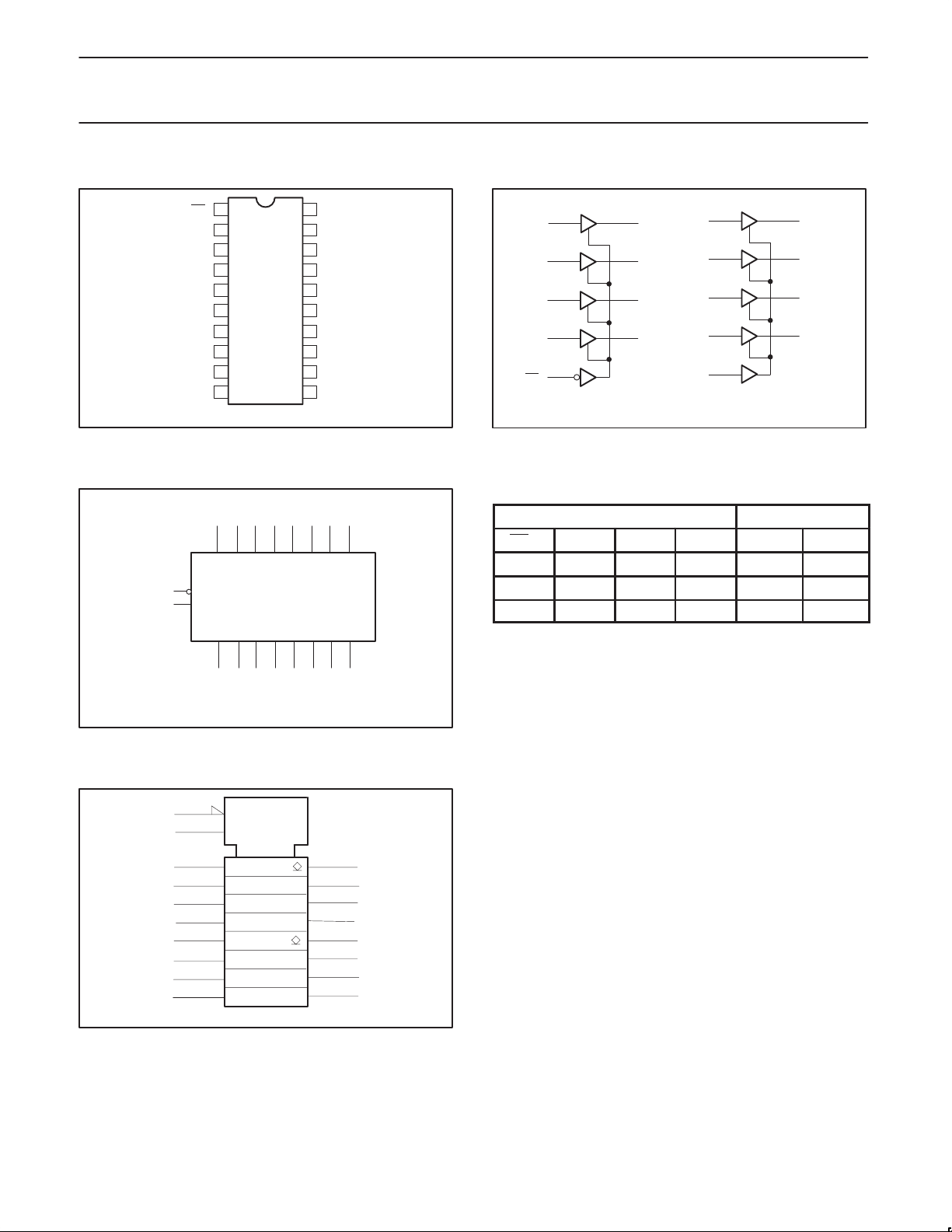

PIN CONFIGURATION for 74F757

OE

1

a

2

Ia0

3

Yb0

4

Ia1

5

Yb1

6

Ia2

7

Yb2

8

Ia3

9

Yb3

10 11

GND

20 V

19

18

17

16

15

14

13

12

SF01248

LOGIC SYMBOL for 74F757

2 4 6 8 17 15 13 11

Ia0 Ia1 Ia2 Ia3 Ib0 Ib1 Ib2 Ib3

1

OEa

19

OEb

Ya0 Ya1Ya2Ya3Yb0Yb1Yb2Yb3

18 16 14 12 3 5 7 9

CC

OEb

Ya0

Ib0

Ya1

Ib1

Ya2

Ib2

Ya3

Ib3

LOGIC DIAGRAM for 74F757

Ia0

Ia1

Ia2

Ia3

OEa

V

= Pin 20

CC

GND = Pin 10

2

4

6

8

1

18

Ya0

16

Ya1

14

Ya2

12

Ya3

Ib0

Ib1

Ib2

Ib3

OEb

17

15

13

11

19

3

5

7

9

SF01251

FUNCTION TABLE for 74F757

INPUTS OUTPUTS

OEa Ia OEb Ib Ya Yb

L L H L L L

L H H H H H

H X L X H (off) H (off)

H = High voltage level

L = Low voltage level

X = Don’t care

Yb0

Yb1

Yb2

Yb3

V

= Pin 20

CC

GND = Pin 10

IEC/IEEE SYMBOL for 74F757

1

19

2

4

6

8

17

15

13

11

EN1

EN2

1

2

SF01250

18

16

14

12

3

5

7

9

SF01249

1989 Nov 27

4

Loading...

Loading...