Philips 74f723a, 74f 723, 74f 725a, 74f725 DATASHEETS

INTEGRATED CIRCUITS

74F723A

Quad 2-to-1 data selector multiplexer

(3-State)

74F723-1

Quad 2-to-1 data selector multiplexer

with 30Ω equivalent output termination

impedance (3-State)

74F725A

Quad 3-to-1 data selector multiplexer

(3-State)

74F725-1

Quad 3-to-1 data selector multiplexer

with 30Ω equivalent output termination

impedance (3-State)

Product specification

1990 Dec 13

IC15 Data Handbook

Philips Semiconductors Product specification

,,

SOT222-1

24-Pin Plastic SOL

,,

SOT137-1

74F723A/74F723–1/

Multiplexers

74F723A Quad 3-to-1 Data Selector Multiplexer (3-State)

74F723-1 Quad 3-to-1 Data Selector Multiplexer with 30 Equivalent Output Termination Impedance (3-State)

74F725A Quad 4-to-1 Data Selector Multiplexer

74F725-1 Quad 4-to-1 Data Selector Multiplexer with 30

Equivalent Output Termination Impedance

74F725A/74F725–1

FEATURES for 74F723A/74F723-1

•Consists of four 3-to-1 Multiplexers

•High impedance PNP base inputs for reduced loading

(20µA in High and Low states)

•Inverting or non-inverting data path capability by an inverting (INV)

input

•Designed for address multiplexing of dynamic RAM and other

applications

•Multiple side pins for V

(improves speed and noise immunity)

and GND to reduce lead inductance

CC

•3-State outputs sink 64mA (74F723A only)

•30 termination impedance on each output – 74F723-1

FEATURES for 74F725A/74F725-1

•Consists of four 4-to-1 Multiplexers

•High impedance PNP base inputs for reduced loading

(20µA in High and Low states)

•Equivalent to two 74F253s without 3-State

•Outputs sink 64mA (74F725A only)

•30 termination impedance on each output – 74F725-1

DESCRIPTION

The 74F723A/74F723-1 consist of four 3-to-1 multiplexers designed

for address multiplexing of dynamic RAMs and other multiplexing

applications. Select (S0, S1) inputs control which line is to be

selected, as defined in the Function Table for 74F723A/74F723-1.

When the invering input (INV

To improve speed and noise immunity, VCC and GND side pins are

used. The 3-State outputs source 15mA and sink 64mA. The

) is Low, the input data path is inverted.

74F723-1 is the same as 74F723A except that it has a 30

temination impedance on each output to reduce line noise and the

3-State outputs sink 5mA.

The 74F725A/74F725-1 consist of four 4-to1 multiplexers designed

for general multiplexing purpose. The select (S0, S1) inputs control

which line is to be selected, as defined in the Function Table for

74F725A/725-1. The outputs source 15mA and sink 64mA. The

74F725-1 is the same as the 74F725A except that it has a 30

termination impedance on each output to reduce line noise and the

outputs sink 5mA.

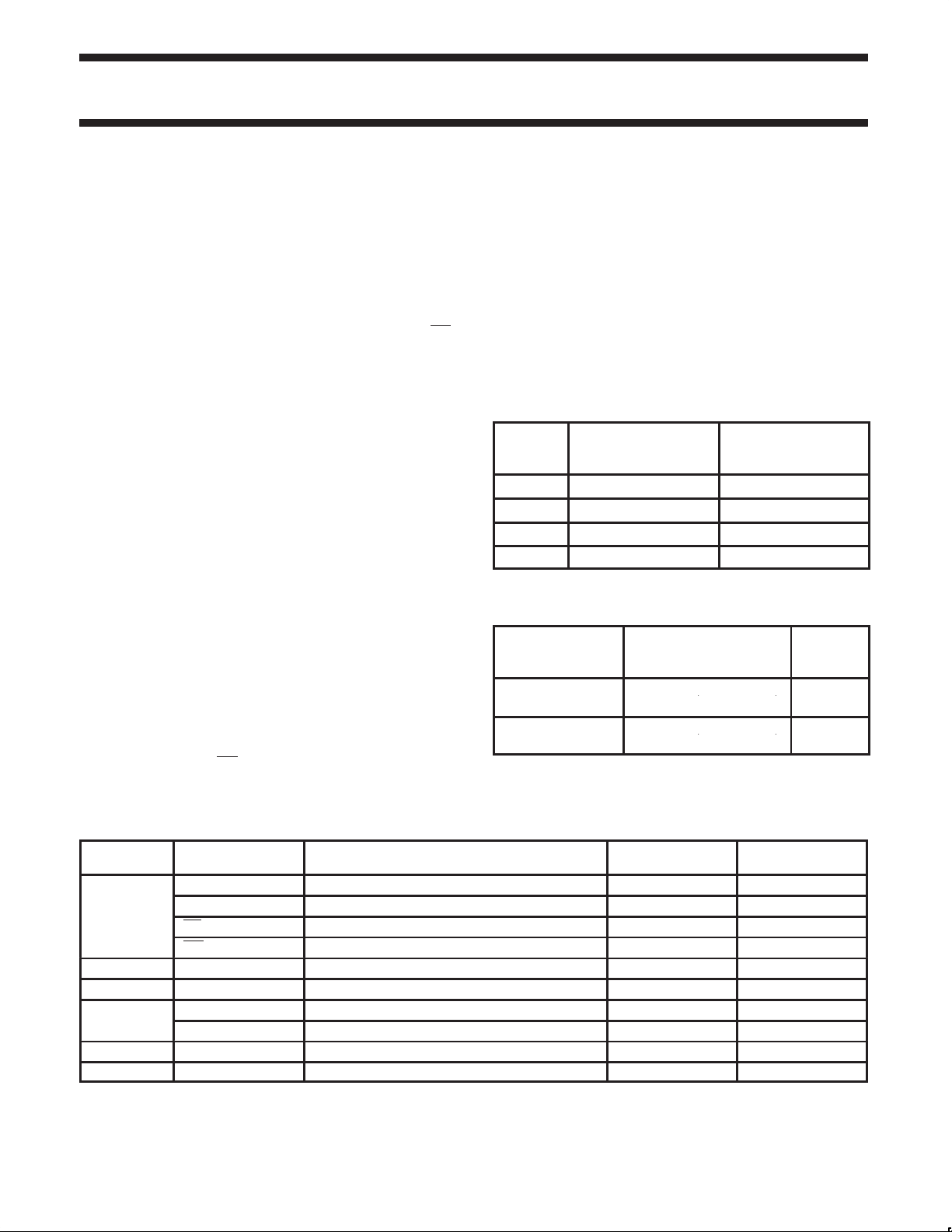

TYPE

74F723A 5.5ns 25mA

74F723-1 7.0ns 26mA

74F725A 5.5ns 20mA

74F725-1 6.5ns 20mA

TYPICAL

PROPAGATION DELAY

TYPICAL SUPPL Y

CURRENT

(TOTAL)

ORDERING INFORMATION

COMMERCIAL RANGE

DESCRIPTION

20-Pin Plastic Slim N74F723AN, N74F723-1N,

DIP (300 mil)

VCC = 5V ± 10%

T

= 0° C to +70°C

amb

N74F725AN, N74F725-1N

N74F723AD, N74F723-1D,

N74F725AD, N74F725-1D

PKG DWG

#

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

74F723A/

74F723-1

74F723A Q0 - Q3 Data outputs for 74F723A 750/106.7 15mA/64mA

74F723-1 Q0 - Q3 Data outputs for 74F723-1 750/8.33 15mA/5mA

74F725A/

74F725-1

74F725A Q0 - Q3 Data outputs 750/106.7 15mA/64mA

74F725-1 Q0 - Q3 Data outputs 750/8.33 15mA/5mA

NOTE: One (1.0) FAST Unit Load (U.L.) is defined as: 20µA in the High state and 0.6mA in the Low state.

1990 Dec 13 853-1369 01257

TYPE PINS DESCRIPTION

Dna, Dnb, Dnc Data inputs 1.0/0.066 20µA/40µA

S0, S1 Select inputs 1.0/0.033 20µA/20µA

OE Output Enable input 1.0/0.033 20µA/20µA

INV Output inverting input 1.0/0.033 20µA/20µA

Dna, Dnb, Dnc, Dnd Data inputs 1.0/0.066 20µA/40µA

S0, S1 Select inputs 1.0/0.033 20µA/20µA

2

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

Philips Semiconductors Product specification

Multiplexers

PIN CONFIGURATION – 74F723A/74F723-1

1

D0a

2

D0b

3

D0c

4

Q0

5

Q1

6

GND

7

GND

8

Q2

9

Q3

10

D3a

11

D3b

D3c

LOGIC SYMBOL – 74F723A/74F723-1

24

OE

23

INV

22

D1a

21

D1b

20

D1c

19

V

18

V

17

D2a

16

D2b

15

D2c

14

S0

1312

S1

SF01226

CC

CC

74F723A/74F723–1/

74F725A/74F725–1

PIN CONFIGURATION – 74F725A/74F725-1

1

D0a

2

D0b

3

D0c

4

D0d

5

Q0

6

Q1

7

GND

8

Q2

9

Q3

10

D3a

11

D3b

D3c

LOGIC SYMBOL – 74F725A/74F725-1

24

SO

23

S1

22

D1a

21

D1b

20

D1c

19

D1d

18

V

17

D2a

16

D2b

15

D2c

14

D2d

1312

D3d

SF01227

CC

14

13

23

24

= Pin 18, 19

V

CC

GND = Pin 6, 7

1 2 3 22212017161510

D0a D0b D1a D1b D2a D2b D3a D3bD0c D1c D2c D3c

S0

S1

INV

OE

48

Q2 Q3

Q1Q0

59

11 12

SF01228

LOGIC SYMBOL (IEEE/IEC) – 74F723A/74F723-1

14

13

23

24

1

2

3

22

21

20

17

16

15

10

11

12

G1

G2

MUX

M

EN

4

5

8

9

SF01230

1 2 3 4 22 21 20 19 17 16

D0a D0b D1a D1b D2a D2b D3a

D0c D1c D2c D3c

D0d D1d D2d D3d

24

23S0S1

Q1Q0

55

VCC = Pin 18

GND = Pin 7

69

15 14 10 11 12

D3b

Q2 Q3

SF01229

LOGIC SYMBOL (IEEE/IEC) – 74F725A/74F725-1

24

23

1

2

3

4

22

21

20

19

17

16

15

14

10

11

12

13

G1

G2

MUX

5

6

8

9

SF01231

13

1990 Dec 13

3

Philips Semiconductors Product specification

Multiplexers

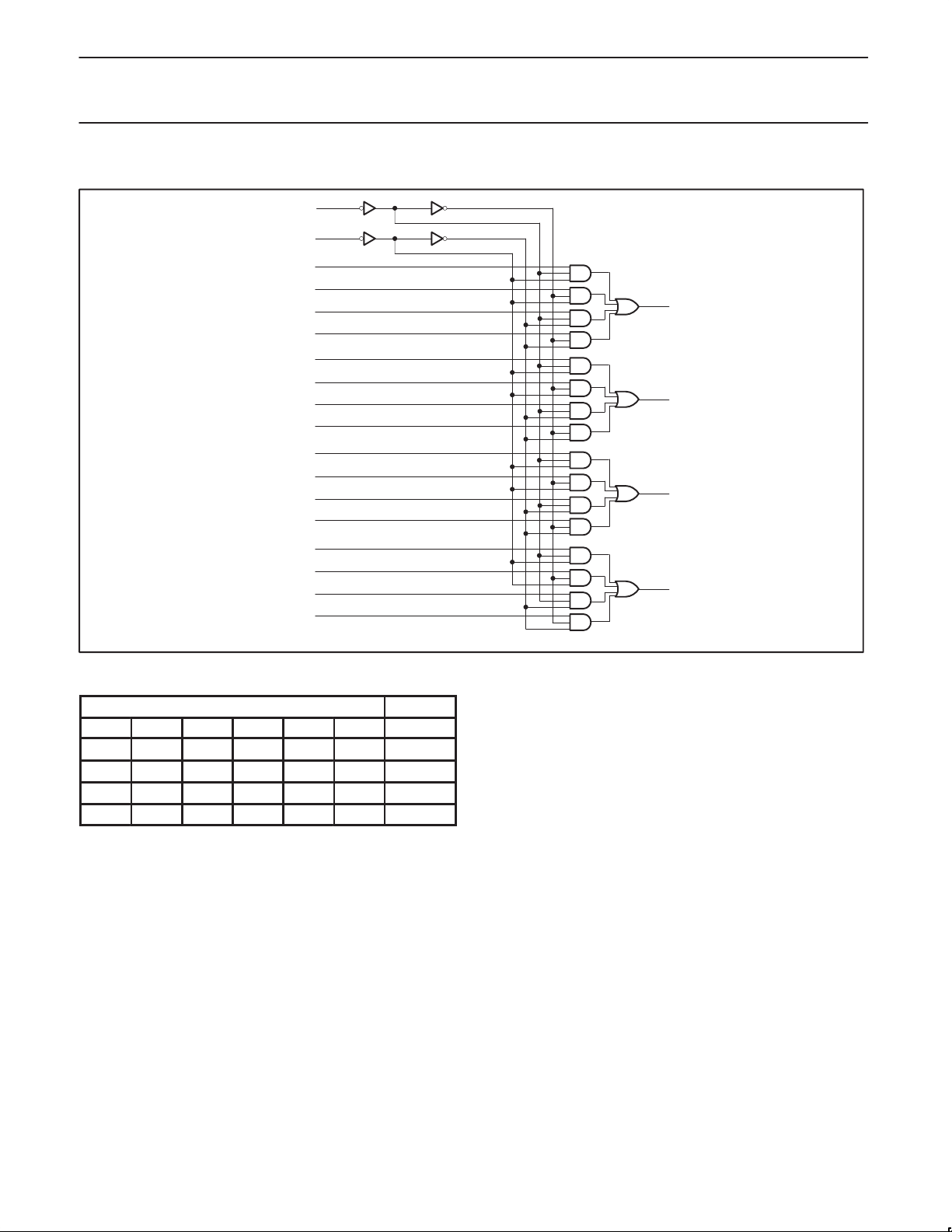

LOGIC DIAGRAM – 74F723A/74F723-1

24

OE

23

INV

14

S0

13

S1

1

D0a

2

D0b

3

D0c

22

D1a

21

D1b

20

D1c

17

D2a

16

D2b

15

D2c

10

D3a

11

D3b

12

V

= Pin 18, 19

CC

GND = Pin 6, 7

D3c

74F723A/74F723–1/

74F725A/74F725–1

4

Q0

5

Q1

8

Q2

9

Q3

SF01232

FUNCTION TABLE – 74F723A/74F723-1

INPUTS OUTPUT

S0 S1 INV OE Dna Dnb Dnc Qn

L L L L Data a Data b Data c Data a

L L H L Data a Data b Data c Data a

H L L L Data a Data b Data c Data b

H L H L Data a Data b Data c Data b

X H L L Data a Data b Data c Data c

X H H L Data a Data b Data c Data c

X X X H X X X Z

H = High voltage level

L = Low voltage level

X = Don’t care

Z = High impedance “off” state

1990 Dec 13

4

Philips Semiconductors Product specification

Multiplexers

LOGIC DIAGRAM – 74F725A/74F725-1

24

S0

23

S1

1

D0a

2

D0b

3

D0c

4

D0d

22

D1a

21

D1b

20

D1c

19

D1d

17

D2a

16

D2b

15

D2c

14

D2d

10

D3a

11

D3b

12

D3c

13

V

= Pin 18

CC

GND = Pin 7

D3d

74F723A/74F723–1/

74F725A/74F725–1

5

Q0

6

Q1

8

Q2

9

Q3

SF01233

FUNCTION TABLE – 74F725A/74F725-1

INPUTS OUTPUT

S0 S1 Dna Dnb Dnc Dnd Qn

L L Data a Data b Data c Data d Data a

H L Data a Data b Data c Data d Data b

L H Data a Data b Data c Data d Data c

H H Data a Data b Data c Data d Data d

H = High voltage level

L = Low voltage level

1990 Dec 13

5

Loading...

Loading...