Philips 74f670 DATASHEETS

INTEGRATED CIRCUITS

74F670

4 x 4 register file (3-State)

Product specification

IC15 Data Handbook

1990 Jul 12

Philips Semiconductors Product specification

74F6704 x 4 register file (3-State)

FEA TURES

•Simultaneous and Independent Read and Write operations

•Expandable to almost any word size and bit length

•3-State outputs

DESCRIPTION

The 74F670 is a 16-bit 3-State Register File organized as 4 words of

4 bits each. Separate Read and Write Address and Enable inputs

are available, permitting simultaneous writing into one word location

and reading from another location. The 4-bit word to be stored is

presented to four data inputs.

The Write address inputs (WA and WB) determine the location of the

stored word. The Write Address inputs should only be changed

when the Write Enable input (WE

operation. When the WE

is Low, the data is entered into the

addressed location.

The addressed location remains transparent to the data while the

WE

is Low. Data supplied at the inputs will be read out in true

(non-inverting) form from the 3-State outputs. Data and address

inputs are inhibited when the WE is High. Direct acquisition of data

stored in any of the four registers is made possible by individual

Read Address inputs (RA, RB). The addressed word appears at the

four outputs when the Read Enable (RE

the high impedance “off” state when the RE

outputs to be tied together to increase the word capacity to very

large numbers.

Up to 128 devices can be stacked to increase the word size to 512

locations by tying the 3-State outputs together. Since the limiting

factor for expansion is the output High current, further stacking is

possible by tying pullup reisistors to the outputs to increase the I

current available. Design of the Read Enable signals for the stacked

devices must ensure that there is no overlap in the Low levels which

cause more than one output to be active at the same time. Parallel

expansion to generate n-bit words is accomplished by driving the

Enable and address inputs of each device in parallel.

) is High for conventional

) is Low. Data outputs are in

is High. This permits

OH

PIN CONFIGURATION

1

D1

2

D2

3

D3

4

RB

5

RA

Q3

6

7

Q2

GND

8

TYPICAL

TYPE

PROPAGATION

DELAY

74F670 6.5ns 50mA

V

16

CC

15

D0

14

WA

13

WB

12

WE

11

RE

10

Q0

Q1

9

SF01178

TYPICAL

SUPPLY CURRENT

(TOTAL)

ORDERING INFORMATION

COMMERCIAL RANGE

DESCRIPTION

16-pin plastic DIP N74F670N SOT38-4

16-pin plastic SOL N74F670D SOT162-1

VCC = 5V ±10%,

T

= 0°C to +70°C

amb

PKG DWG #

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

D0 - D3 Data inputs 1.0/1.0 20µA/0.6mA

WA, WB Write address inputs 1.0/1.0 20µA/0.6mA

RA, RB Read address inputs 1.0/1.0 20µA/0.6mA

WE Write Enable inputs 1.0/1.0 20mA/0.6mA

RE Read Enable inputs 1.0/1.0 20mA/0.6mA

Q0–Q3 Data output 150/40 3.0mA/24mA

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

1990 Jul 12 853-0014 99965

2

LOAD VALUE

HIGH/LOW

Philips Semiconductors Product specification

OPERATING MODE

Read

OPERATING MODE

Write data

74F6704 x 4 register file (3-State)

LOGIC SYMBOL

14 13 5 4 15 1 2 3

WA WB RA RB D0 D1 D2 D3

WE

12

RE

11

Q3Q2

76

SF01179

V

=Pin 16

CC

GND=Pin 8

Q1Q0

10 9

WORD SELECT FUNCTION TABLE

WRITE MODE READ MODE OPERATING MODE

WB WA RB RA Word Selected

L L L L W ord 0

L H L H Word 1

H L H L Word 2

H H H H Word 3

H = High voltage level

L = Low voltage level

READ MODE FUNCTION TABLE

INPUT

RE

INTERNAL

LATCHES*

L L L

L H H

H X Z Disabled

H = High voltage level

L = Low voltage level

X = Don’t care

Z = High impedance “off” state

* = The selection of “internal latches” by Read Address

(RA and RB) are not constrained by WE

OUTPUT

Qn

or RE operation.

LOGIC SYMBOL (IEEE/IEC)

14

13

5

4

12

11

15

1

2

3

RAM 4X4

0

0

1A

3

1

0

0

2A

3

1

C4 [WRITE]

EN [READ]

1A, 4D

10

2A

9

7

6

SF01180

WRITE MODE FUNCTION TABLE

INPUTS

WE Dn

L L L

L H H

H X NC Data latched

H = High voltage level

L = Low voltage level

NC= No change

X = Don’t care

* = The write address (WA and WB) to the “internal latches”

must be stabled while WE

INTERNAL

LATCHES*

is Low for conventional operation.

1990 Jul 12

3

Philips Semiconductors Product specification

74F6704 x 4 register file (3-State)

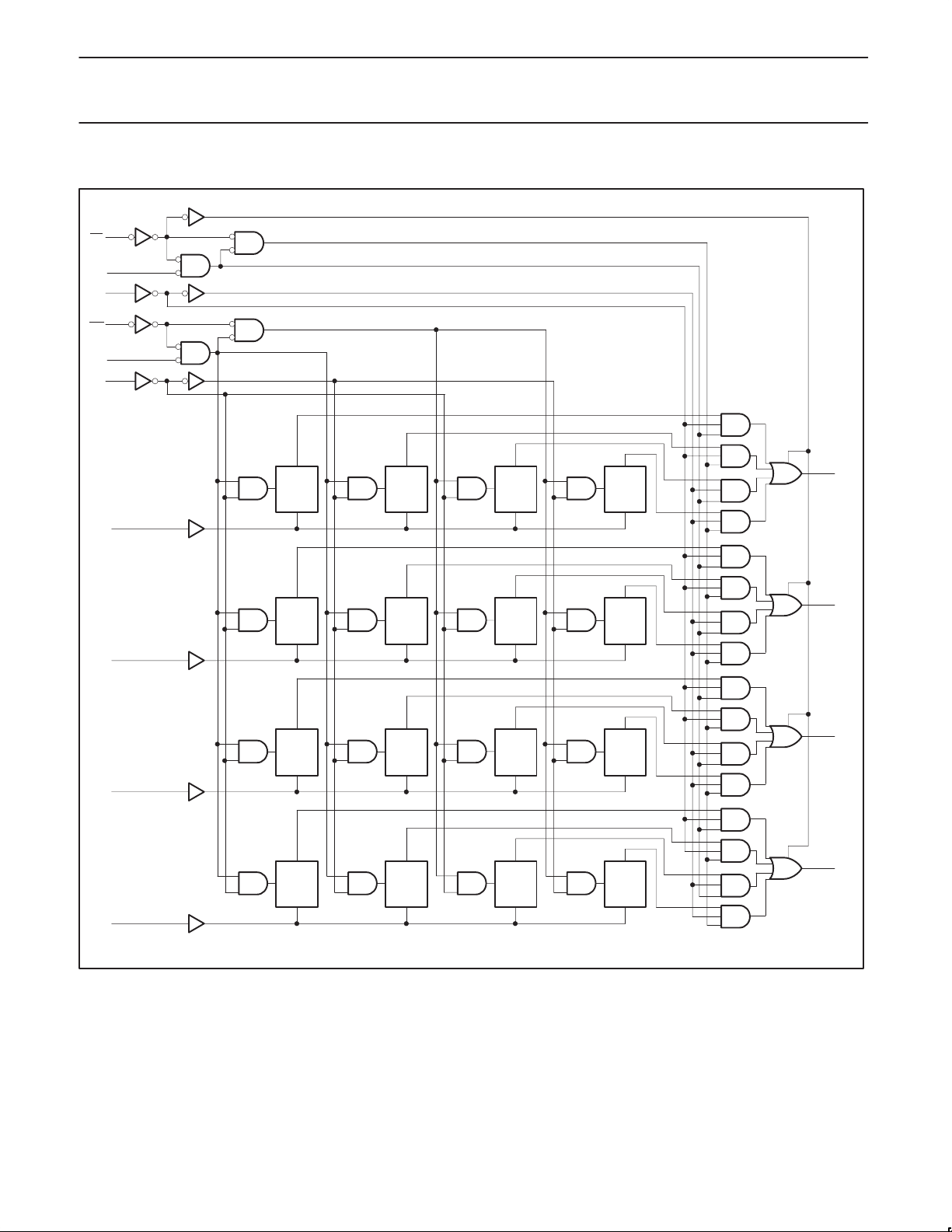

LOGIC DIAGRAM

11

RE

5

RA

4

RB

12

WE

13

WB

14

WA

6

Q

E

D

3

D3

Q

E

D

Q

E

D

Q

E

D

Q3

2

D2

1

D1

15

D0

V

=Pin 16

CC

GND=Pin 8

7

9

10

SF01181

Q2

Q1

Q0

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

Q

E

D

1990 Jul 12

4

Loading...

Loading...