Philips 74f656a DATASHEETS

INTEGRATED CIRCUITS

74F656A

Octal buffer/driver with parity,

non-inverting (3-State)

Product specification

Supersedes data of 1991 Jul 17

IC15 Data Handbook

2000 Jun 30

Philips Semiconductors Product specification

Octal buffer/driver with parity, non-inverting (3-State)

FEA TURES

•Significantly improved AC performance over 74F656

•High impedance NPN base input for reduced loading

(40µA in High and Low states)

•Ideal in applications where high output drive and light bus loading

are required (I

is 40µA vs. FAST std of 600µA)

IL

•74F656A combines 74F244 and 74F280A functions in one

package

•Non-inverting

•3-State outputs sink 64mA and source 15mA

•24-pin plastic Slim DIP (300mil) package

•Inputs on one side and outputs on the other side simplifies PC

board layout

•Combined functions reduce part count and enhance system

performance

•Industrial temperature range available (–40°C to +85°C)

DESCRIPTION

The 74F656A is an octal buffer and line driver with parity

generation/checking designed to be employed as memory address

drivers, clock drivers and bus-oriented transmitters/receivers. These

parts include parity generator/checker to improve PC board density.

TYPICAL

TYPE

74F656A 6.5ns 64mA

PROPAGATION

DELA Y

74F656A

TYPICAL SUPPL Y CURRENT

(TOTAL)

ORDERING INFORMATION

COMMERCIAL RANGE

DESCRIPTION

24-pin Plastic Slim

DIP (300mil)

24-pin Plastic SOL N74F656AD I74F656AD SOT137-1

VCC = 5V ±10%,

T

= 0°C to +70°C

amb

N74F656AN I74F656AN SOT222-1

INDUSTRIAL RANGE

VCC = 5V ±10%,

T

= –40°C to +85°C

amb

PKG DWG #

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

D0–D7 Data inputs 2.0/0.066 40µA/40µA

PI Parity input 1.0/0.033 20µA/20µA

OE0, OE1, OE2 Output Enable Inputs (active Low) 1.0/0.033 20µA/20µA

ΣE, ΣO Parity outputs 750/106.7 15mA/64mA

Q0–Q7 Data outputs 750/106.7 15mA/64mA

NOTE: One (1.0) FAST Unit Load (U.L.) is defined as: 20µA in the High state and 0.6mA in the Low state.

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

2000 Jun 30 853-0383 24025

2

Philips Semiconductors Product specification

Octal buffer/driver with parity, non-inverting (3-State)

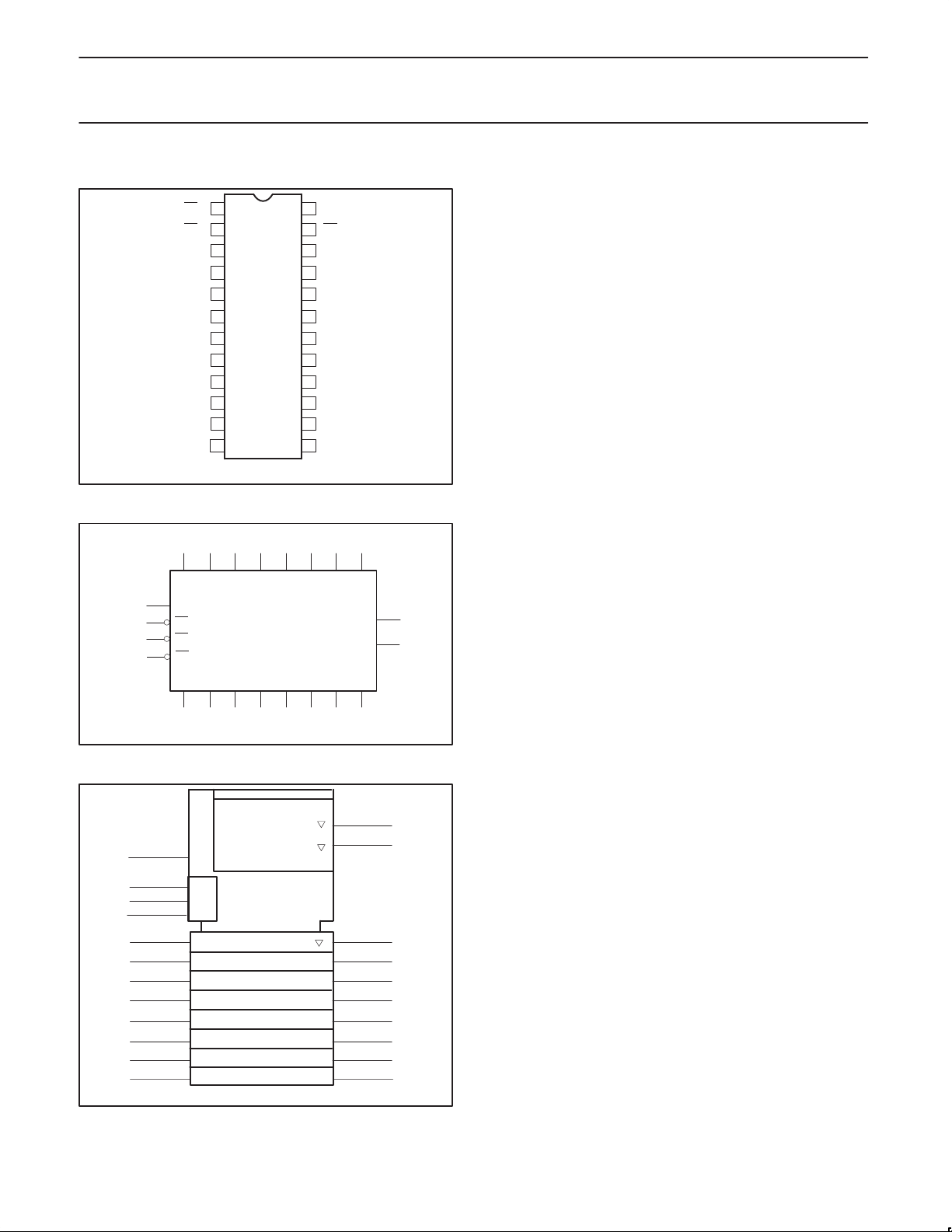

PIN CONFIGURATION

OE

OE

GND

LOGIC SYMBOL

0

1

1

2

PI

3

D0

4

D1

5

D2

6

D3

7

D4

8

D5

9

D6

10

D7

11

24

23

22

21

20

19

18

17

16

15

14

1312

SF01169

VCC

OE2

ΣO

ΣE

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

74F656A

4567891011

D0 D1 D2 D3 D4 D5 D6 D7

PI

3

OE0

1

OE1

2

23

VCC=Pin 24

GND=Pin 12

OE2

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

20 19 18 17 16 15 14 13

LOGIC SYMBOL (IEEE/IEC)

2K

3,5,6,7,8

9,10,11,12

3

1

2

23

4

5

6

7

8

9

10

P3

≥1

Z5

Z6

Z7

Z8

Z9

Z10

Z11

Z12

3,5,6,7,8

9,10,11,12

EN4

[EVEN]

[ODD]

21

ΣE

22

ΣO

SF01171

21

22

4

20

19

18

17

16

15

14

1311

SF01173

2000 Jun 30

3

Loading...

Loading...