Philips 74f604 DATASHEETS

Philips Semiconductors Product specification

74F604Dual octal latch (3-State)

FEA TURES

•High impedance NPN base inputs for reduced loading

(20µA in High and Low states)

•Stores 16-bit–wide Data inputs, multiplexed 8-bit outputs

•3-State outputs

•Power supply current 75mA typical

DESCRIPTION

The 74F604 multiplexed latch is ideal for storing data from two input

buses, A or B, and providing data from either the A or B latches to

the output bus. Organized as 8-bit A and B latches, the latch outputs

are connected by pairs to eight 2-input multiplexers. A Select

(SELECT A/B

are multiplexed to the eight 3-State outputs. Data entered from the B

inputs are selected when SELECT A/B

inputs are selected when SELECT A/B

latches when the Latch Enable (LE

the LE

disabled when LE

) input determines whether the A or B latch contents

is Low; data from the A

is High. Data enters the

) input is Low and is latched on

rising edge. The outputs are enabled when LE is High and

is Low.

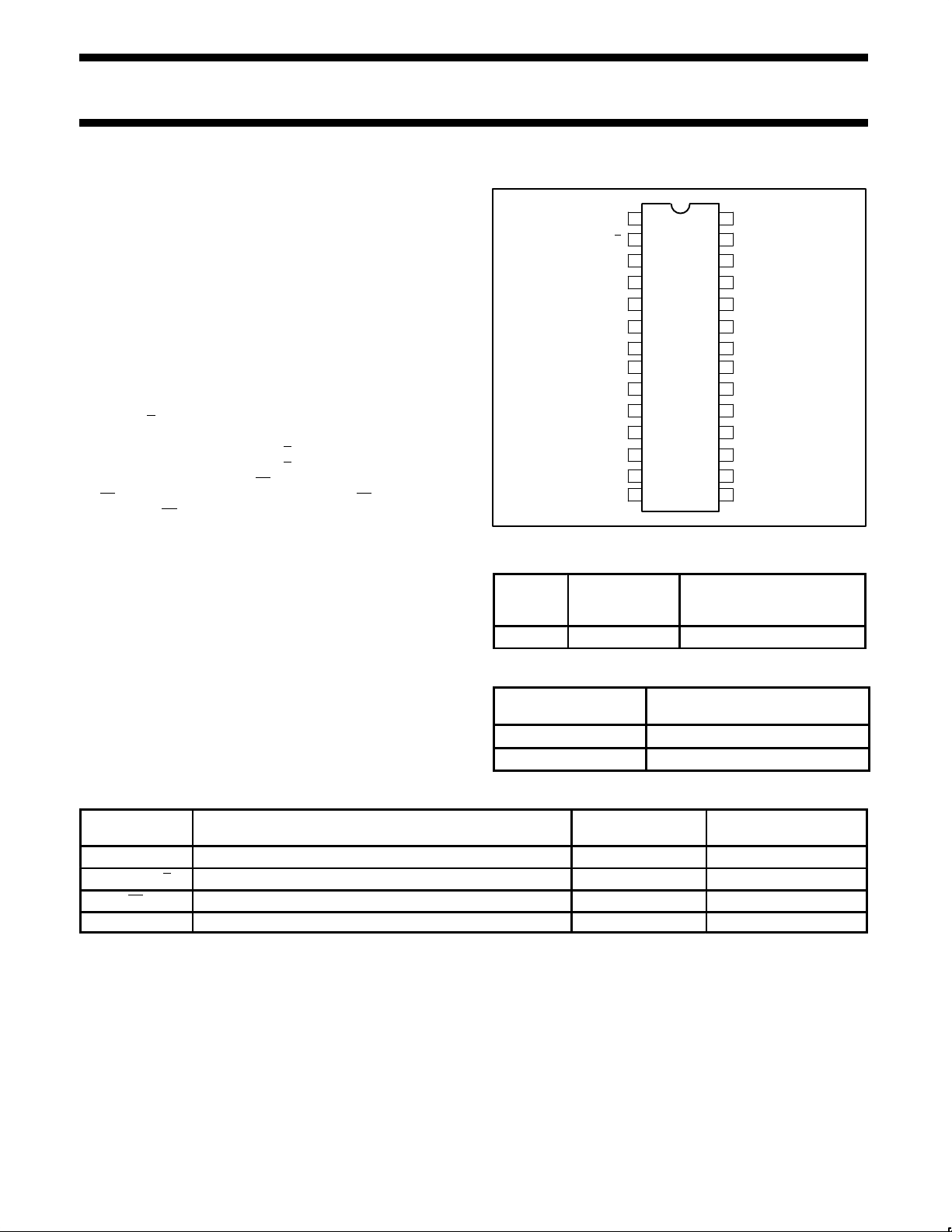

PIN CONFIGURA TION

1

LE

A0

B0

A1

B1

A2

A3

B3

Q3

Q2

Q1

2

3

4

5

6

9

10

11

12

SELECT A/B

TYPICAL

TYPE

PROPAGATION

DELAY

74F604 7.5ns 75mA

28

V

27

A4

26

B4

25

A5

24

B5

23

A6

227

B6

218B2 A7

20

B7

19

Q7

18

Q6

17

Q5

1613

Q4

1514GND Q0

TYPICAL SUPPLY CURRENT

CC

SF01115

(TOTAL)

ORDERING INFORMATION

DESCRIPTION

28-pin plastic DIP N74F604N

28-pin plastic SOL N74F604D

COMMERCIAL RANGE

= 5V ±10%, T

V

CC

= 0°C to +70°C

amb

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F (U.L.)

HIGH/LOW

A0–A7, B0–B7 Data inputs 1.0/0.033 20µA/20µA

SELECT A/B Select input 1.0/0.033 20µA/20µA

LE Latch Enable input (active Low) 1.0/0.033 20µA/20µA

Q0–Q7 Data outputs 150/40 3mA/24mA

NOTE:

One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state.

LOAD VALUE

HIGH/LOW

1990 Mar 01 853–0029 98991

1

Philips Semiconductors Product specification

74F604Dual octal latch (3-State)

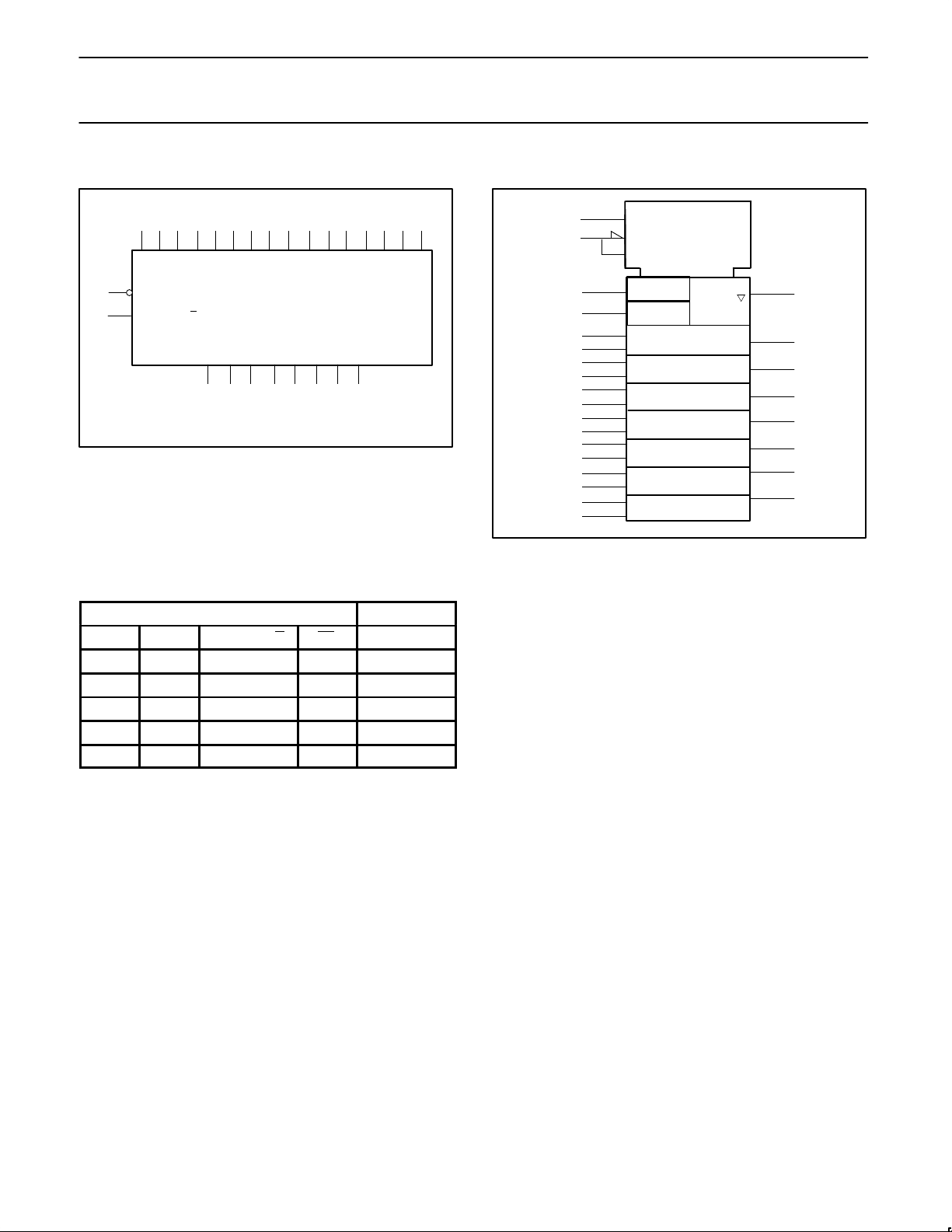

LOGIC SYMBOL

3

456

B0 B1 B2 B3 B4 B5 B6 B7

A0 A1 A2 A3

LE

1

SELECT A/B

2

VCC= Pin 28

GND = Pin 14

8910

Q0 Q1 Q2 Q3

15

13 12 11

27 26 25 24 23

A4 A5 A67A7

Q4 Q5 Q616Q7

17 18 19

22 21 20

FUNCTION TABLE

INPUTS OUTPUTS

A0–A7 B0–B7 SELECT A/B LE Q0–Q7

A data B data L ↑ B data

A data B data H ↑ B data

X X X L Z

X X L H B latched data

X X H H A latched data

H = High voltage level

L = Low voltage level

X = Don’t care

Z = High impedance “off” state

↑ = Low-to-High clock transition

SF01116

IEC/IEEE SYMBOL (IEEE/IEC)

2

1

3

4

5

6

7

8

9

10

27

26

25

24

23

22

21

20

G2

E1

EN

1D 2

1D 2

≥1

15

13

12

11

16

17

18

19

SF01117

1990 Mar 01

2

Philips Semiconductors Product specification

74F604Dual octal latch (3-State)

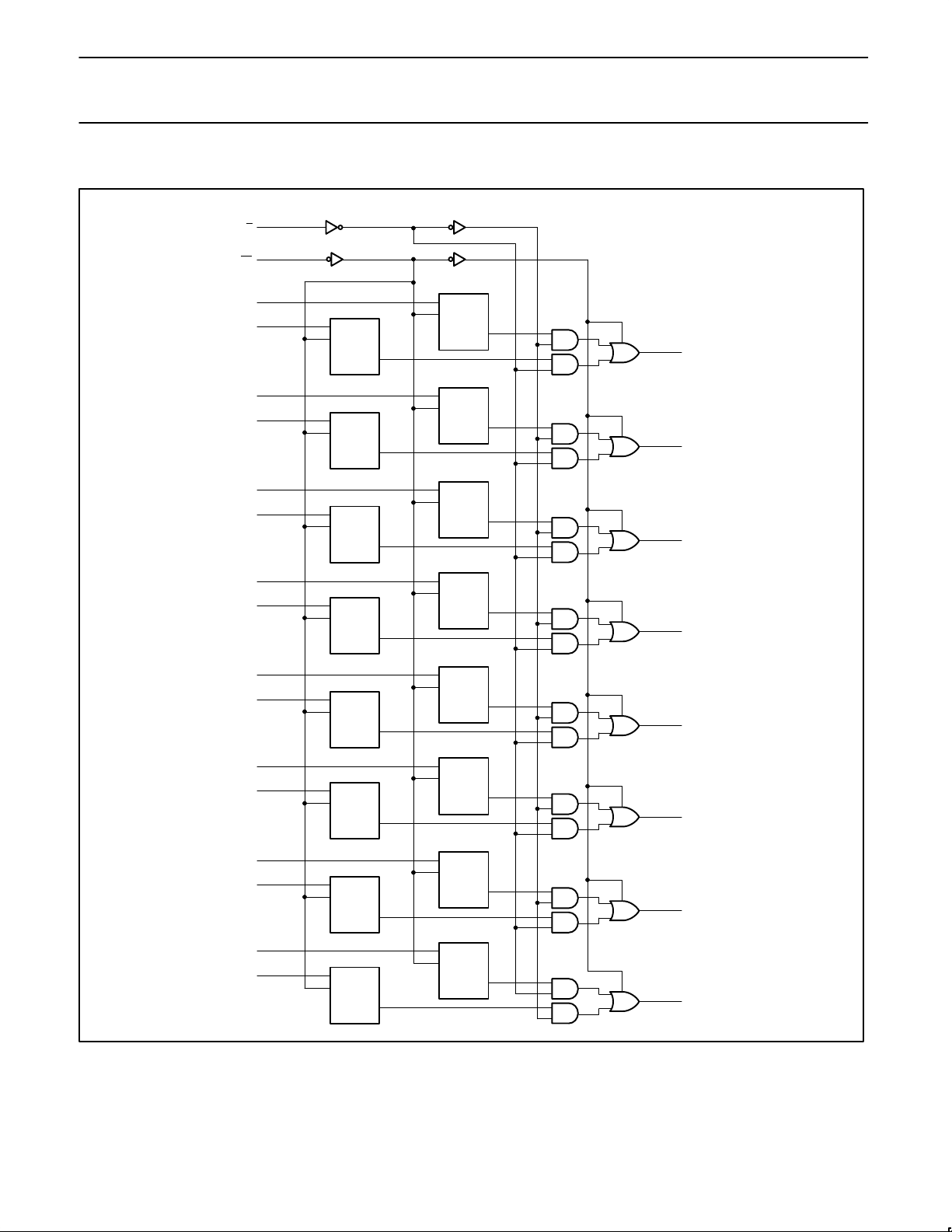

LOGIC DIAGRAM

SELECT A/B

2

1

LE

3

A0

4

B0

5

A1

6

B1

7

A2

8

B2

9

A3

10

B3

27

A4

26

B4

D

E

D

E

D

E

D

E

D

E

D

E

15

Q0

D

E

13

Q1

D

E

12

Q2

D

E

11

Q3

D

E

16

Q4

VCC = Pin 28

GND = Pin 14

1990 Mar 01

25

A5

24

B5

23

A6

22

B6

21

A7

20

B7

D

E

D

E

D

E

D

E

17

Q5

D

E

18

Q6

D

E

19

Q7

SF01118

3

Loading...

Loading...