Philips 74f538 DATASHEETS

INTEGRATED CIRCUITS

74F538

1-of -8 decoder (3–state)

Product specification

IC15 Data Handbook

1989 Apr 06

Philips Semiconductors Product specification

74F5381-of-8 decoder (3-State)

DESCRIPTION

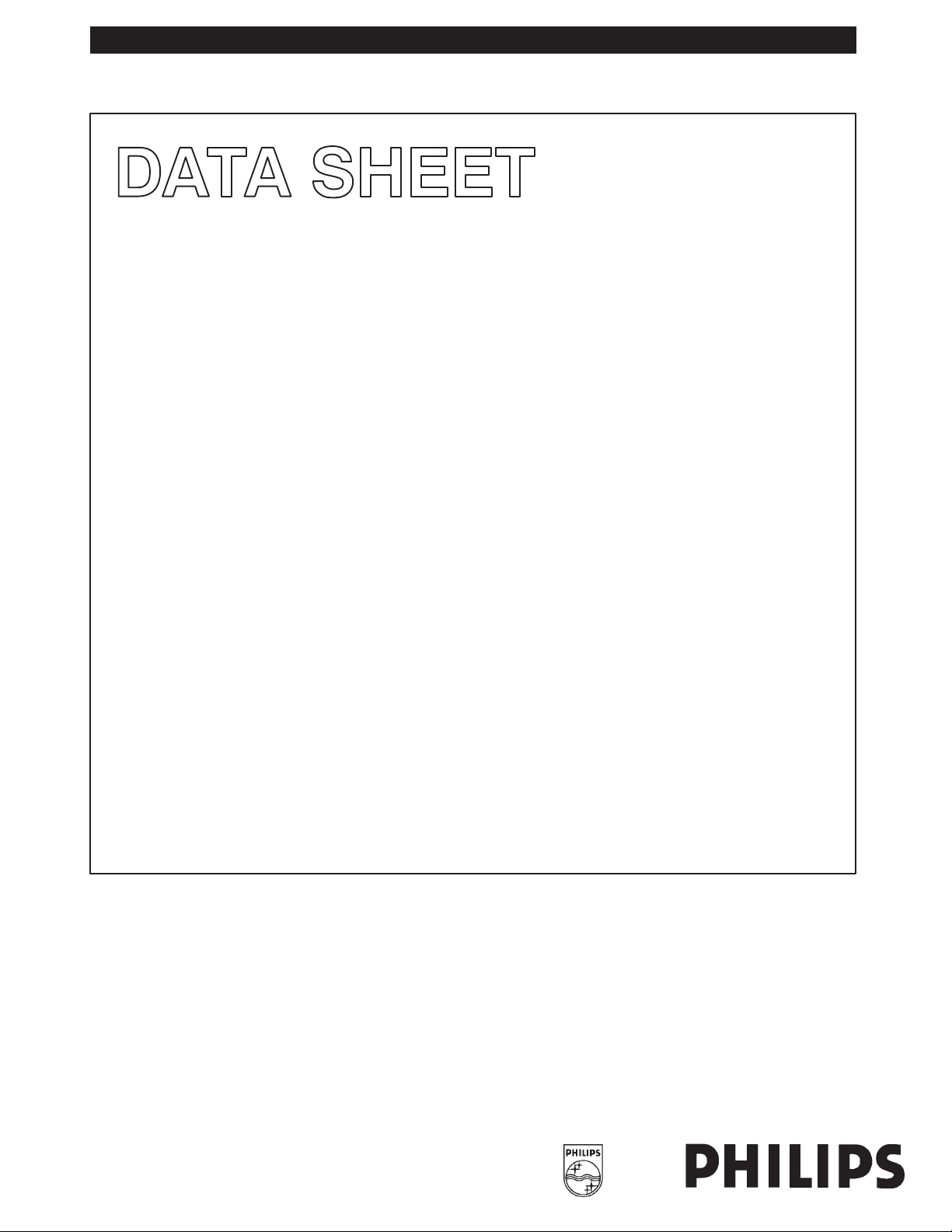

PIN CONFIGURATION

The 74F538 decoder/demultiplexer accepts three address (A0 - A2)

input signals and decodes them to select one of eight mutually

exclusive outputs. A Polarity control (P) input determines whether

the outputs are active Low or active High. The 74F538 has 3-State

outputs, and a High signal on the Output Enables (OE

n) inputs will

force all outputs to the high impedance state. Two active High (E2,

E3) and two active Low (E

0, E1) inputs are available for easy

expansion to 1-of-32 decoding with four packages, or for data

demultiplexing to 1-of-8 or 1-of-16 destinations.

TYPE

TYPICAL

PROPAGATION DELAY

TYPICAL SUPPL Y

CURRENT

(TOTAL)

74F538 8.5ns 35mA

ORDERING INFORMATION

Q2

1

Q1

2

Q0

3

0

OE

4

OE1

5

A0

6

A1

7

Q5

8

Q6

9

GND

10 11

20

19

18

17

16

15

14

13

12

SF00996

V

Q3

Q4

A2

E

E1

E2

E3

P

Q7

CC

0

COMMERCIAL RANGE

DESCRIPTION

VCC = 5V ±10%,

T

= 0°C to +70°C

amb

PKG DWG #

20-Pin Plastic DIP N74F538N SOT146-1

20-Pin Plastic SOL N74F538D SOT163-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

A0 - A2 Address inputs 1.0/1.0 20µA/0.6mA

E0, E1 Enable inputs (active Low) 1.0/1.0 20µA/0.6mA

E2, E3 Enable inputs (active High) 1.0/1.0 20µA/0.6mA

P Polarity control input 1.0/1.0 20µA/0.6mA

OE0, OE1 Output Enable inputs 1.0/1.0 20µA/0.6mA

Q0 - Q7 Data outputs 150/40 3.0mA/24mA

NOTE: One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

LOAD VALUE

HIGH/LOW

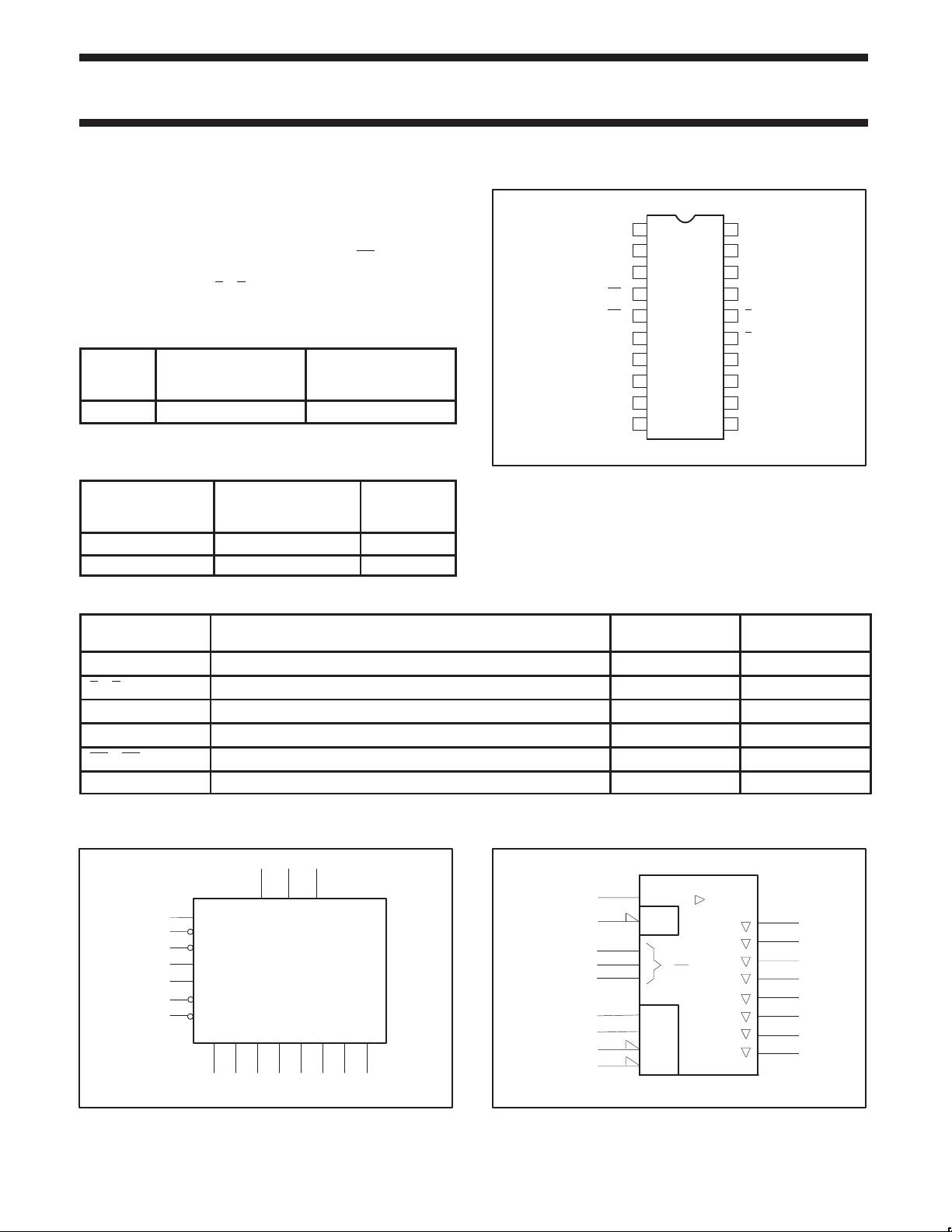

LOGIC SYMBOL

6717

P

12

E0

16

E1

15

14

E2

13

E3

4

OE0

5

OE1

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

= Pin 20

V

CC

GND = Pin 10

1989 Apr 06 853–1273 96267

A0 A1 A2

32119188911

SF00997

LOGIC SYMBOL (IEEE/IEC)

4

5

6

7

17

13

14

15

16

2

DMUX

N8

&

EN

0,8

0

G

2

&

1,8

0

2,8

7

3,8

4,8

5,8

6,8

7,8

3

2

1

19

18

8

9

11

SF00998

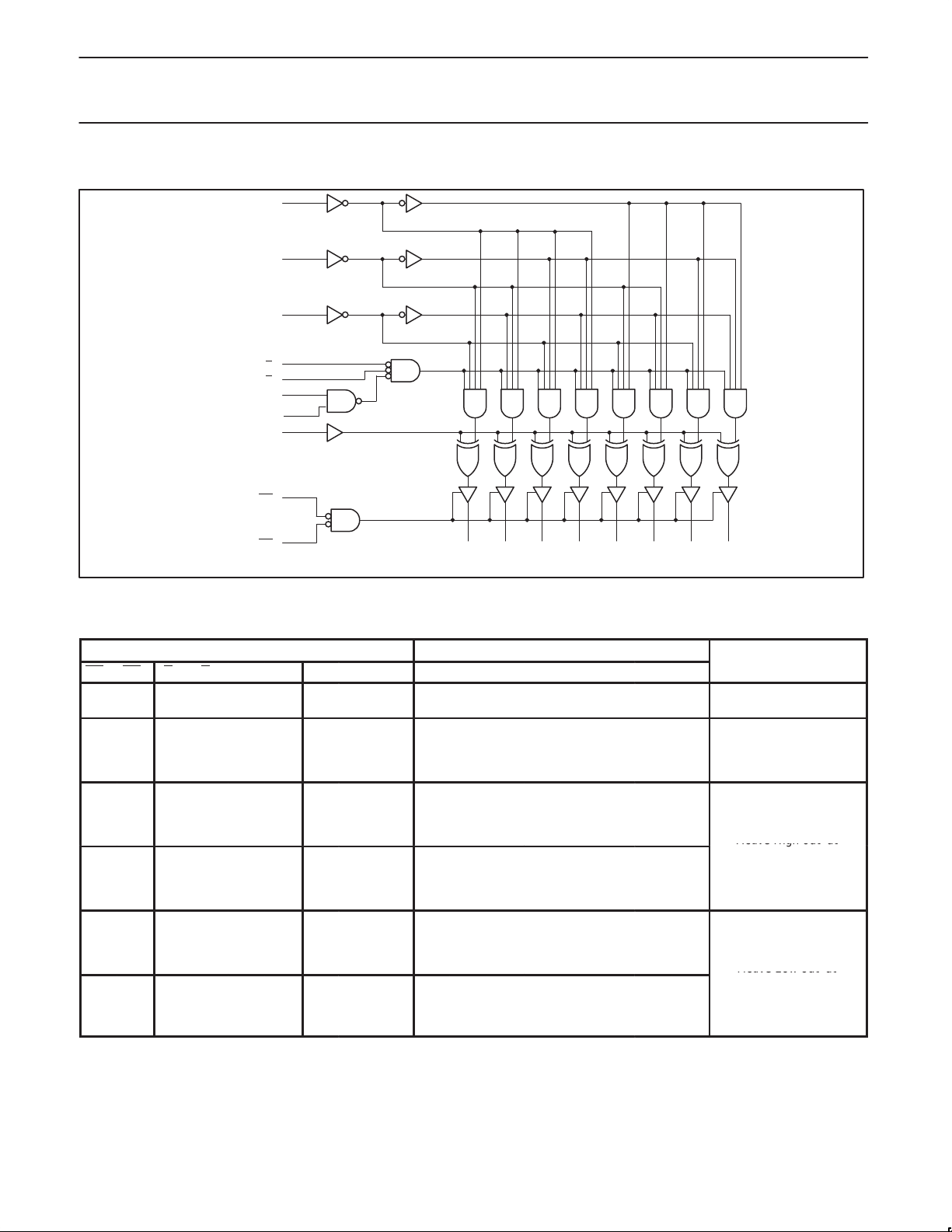

Philips Semiconductors Product specification

OPERATING MODE

Active High out ut

Active Low out ut

74F5381-of-8 decoder (3-State)

LOGIC DIAGRAM

17

A2

7

A1

6

A0

16

0

E

15

E

1

14

E2

13

E3

12

P

4

OE0

32119188911

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

V

= Pin 20

CC

GND = Pin 10

OE

5

1

FUNCTION TABLE

INPUTS OUTPUTS

OE0OE1E0E1E2E3A2A1A0Q0Q1Q2 Q3 Q4 Q5 Q6 Q7

HXXHXXXXXXXXXXXXXXZZZZZZZZZZZZZZZ

L

L

H

X

X

X

X

X

L

L

X

H

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

X

L

X

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

X

X

L

X

X

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

H = High voltage level

L = Low voltage level

X = Don’t care

Z = High impedance “off” state

X

X

X

X

L

X

H

L

H

L

H

L

H

L

H

H

H

H

H

H

H

H

H

L

H

L

H

L

H

L

H

H

H

H

H

H

H

H

X

X

X

X

X

X

X

L

L

L

H

H

L

L

H

H

L

L

H

H

L

L

H

H

H

H

L

L

L

H

L

L

L

H

L

L

L

H

L

L

L

H

H

L

H

H

H

L

H

H

H

L

H

H

H

Outputs equal P input Disable

L

L

L

L

L

H

L

L

L

H

L

L

L

L

L

L

L

L

L

L

H

H

L

H

H

L

H

H

H

H

H

H

H

H

H

H

L

L

L

H

L

L

H

L

L

L

L

L

L

H

H

H

H

H

H

L

H

H

L

H

H

H

H

H

H

L

L

L

L

L

L

L

L

L

H

L

L

H

L

L

H

H

H

H

H

H

H

H

H

H

L

H

H

L

H

H

Z

L

L

L

L

L

L

L

H

H

H

H

H

H

H

H

L

SF00999

High Impedance

Active High output

(P = L)

Active Low output

(P = H)

1989 Apr 06

3

Loading...

Loading...