Philips 74f353 DATASHEETS

INTEGRATED CIRCUITS

74F353

Dual 4-input multiplexer (3-State)

Product specification 1996 Jan 05

IC15 Data Handbook

Philips Semiconductors Product specification

74F353Dual 4-input multiplexer (3-State)

FEA TURES

•Inverting version of 74F253

•3-State outputs for bus interface and multiplex expansion

•Common select inputs

•Separate Output Enable Inputs

DESCRIPTION

The 74F353 has two identical 4-input multiplexers with 3-State

outputs which select two bits from four sources selected by common

Select inputs (S0, S1). When the individual Output Enable (OE

OE

b) inputs of the 4-input multiplexers are High, the outputs are

forced to a high impedance (Hi-Z) state.

The 74F353 is the logic implementation of a 2-pole, 4-position

switch; the position of the switch being determined by the logic

levels supplied to the two common Select inputs.

To avoid exceeding the maximum current ratings when the outputs

of the 3-State devices are tied together, all but one device must be

in the high-impedance state. Therefore, only one Output Enable

must be active at a time.

a,

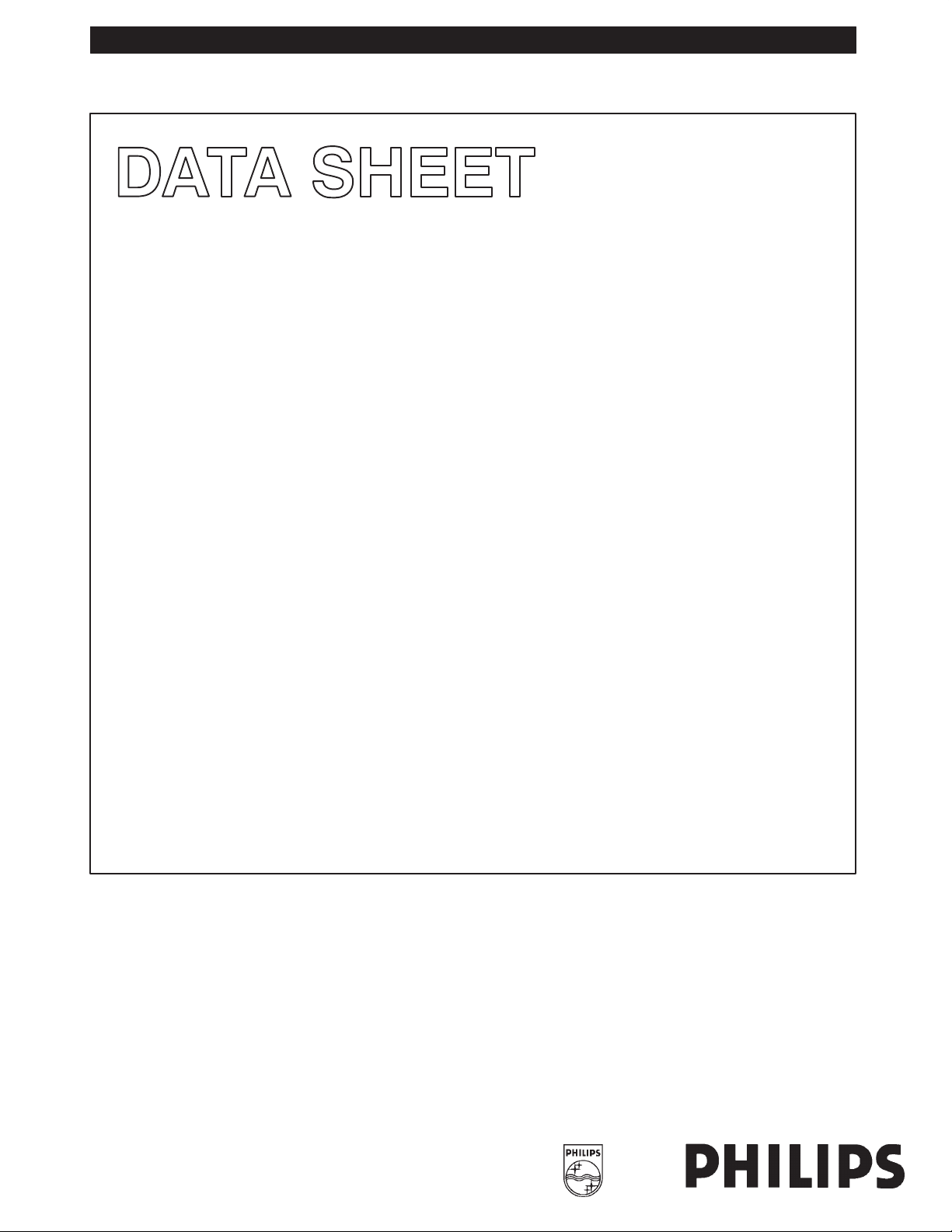

PIN CONFIGURATION

1

a

OE

2

S1

3

I3a

4

I2a

5

I1a

I0a

6

Y

a

TYPICAL

TYPE

PROPAGATION

DELAY

74F353 6.0ns 11mA

16

V

CC

15

b

OE

14

S0

13

I3b

I2b

12

I1b

11

I0b

107

98GND Yb

SF00891

TYPICAL

SUPPLY CURRENT

(TOTAL)

ORDERING INFORMATION

COMMERCIAL RANGE

DESCRIPTION

VCC = 5V ±10%,

T

= 0°C to +70°C

amb

16-pin plastic DIP N74F353N SOT38-4

16-pin plastic SO N74F353D SOT162-1

PACKAGE

DRAWING

NUMBER

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION 74F (U.L.) HIGH/LOW LOAD VALUE HIGH/LOW

I0a–I3a Port A data inputs 1.0/1.0 20µA/0.6mA

I0b–I3b Port B data inputs 1.0/1.0 20µA/0.6mA

S0, S1 Common Select inputs 1.0/1.0 20µA/0.6mA

OEa Port A Output Enable input (active Low) 1.0/1.0 20µA/0.6mA

OEb Port B Output Enable input (active Low) 1.0/1.0 20µA/0.6mA

Ya, Yb 3-State outputs 150/40 3mA/24mA

NOTE:

One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state.

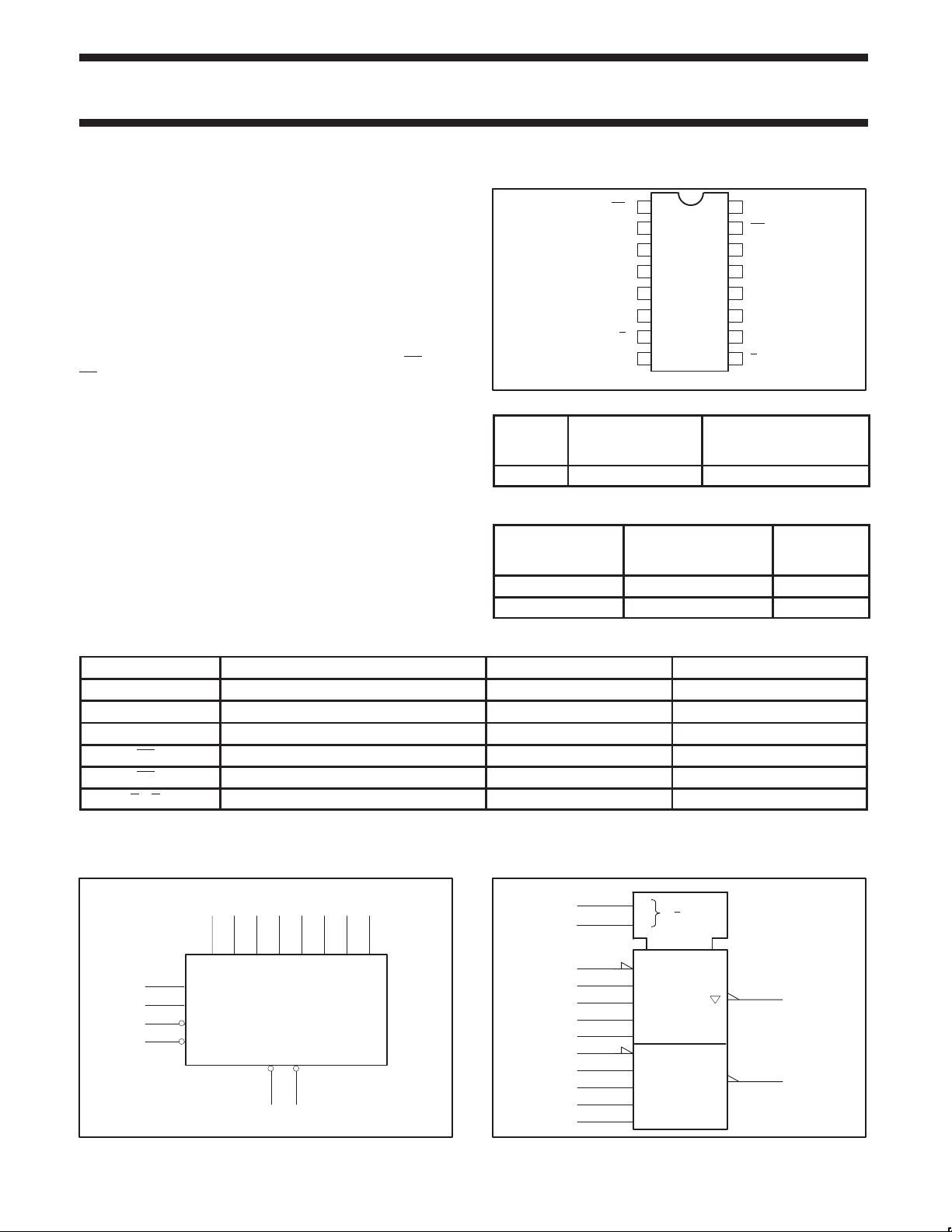

LOGIC SYMBOL

14

2

1

15

V

= Pin 16

CC

GND = Pin 8

6 13121110

I0a I1a I2a I3a I0b I1b I2b I3b

S0

S1

OEa

OEb

345

Ya Yb

97

SF00892

IEC/IEEE SYMBOL

14

2

1

6

5

4

3

15

10

11

12

13

EN

0

0

G

3

1

MUX

0

1

2

3

7

9

SF00893

1996 Jan 05 853–0103 16188

2

Philips Semiconductors Product specification

74F353Dual 4-input multiplexer (3-State)

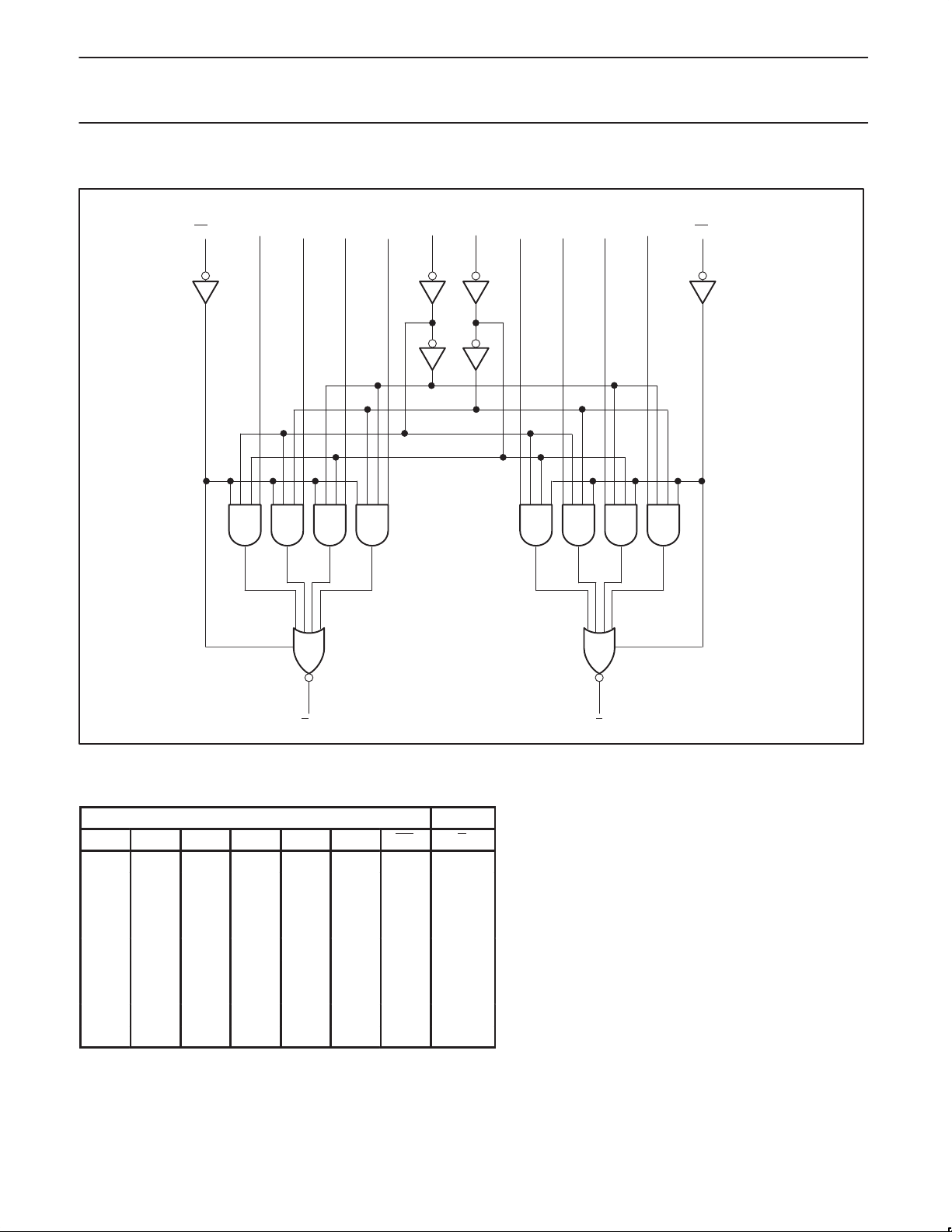

LOGIC DIAGRAM

S0

a

I0a I1a I2a I3aOE

1

S1

2

3456

I0b I1b I2b I3b OE

14

10 11 12 13

b

15

7

VCC = Pin 16

GND = Pin 8

Ya

FUNCTION TABLE

INPUTS OUTPUT

S0 S1 I0 I1 I2 I3 OE Y

X X X X X X H Z

L L L X X X L H

L L H X X X L L

H L X L X X L H

H L X H X X L L

L H X X L X L H

L H X X H X L L

H H X X X L L H

H H X X X H L L

NOTES:

H = High voltage level

L = Low voltage level

X = Don’t care

Z = High impedance “off” state

9

Yb

SF00894A

1996 Jan 05

3

Loading...

Loading...