Philips 74f193 DATASHEETS

INTEGRATED CIRCUITS

74F193

Up/down binary counter with separate

up/down clocks

Product specification

IC15 Data Handbook

1995 Jul 17

Philips Semiconductors Product specification

74F193Up/down binary counter with separate up/down clocks

FEA TURES

•Synchronous reversible 4-bit counting

•Asynchronous parallel load capability

•Asynchronous reset (clear)

•Cascadable without external logic

DESCRIPTION

The 74F193 is a 4-bit synchronous up/down counter in the binary

mode. Separate up/down clocks, CP

simplify operation. The outputs change state synchronously with the

Low-to-High transition of either clock input. If the CP

pulsed while CP

is pulsed while CP

is held High, the device will count up. If CPD clock

D

is held High, the device will count down. The

U

device can be cleared at any time by the asynchronous reset pin. It

may also be loaded in parallel by activating the asynchronous

parallel load pin.

Inside the device are four master-slave JK flip-flops with the

necessary steering logic to provide the asynchronous reset,

asynchronous preset, load, and synchronous count up and count

down functions.

Each flip-flop contains JK feedback from slave to master, such that a

Low-to-High transition on the CP

one, while a similar transition on the CP

count by one.

One clock should be held High while counting with the other,

because the circuit will either count by twos or not at all, depending

on the state of the first JK flip-flop, which cannot toggle as long as

either clock input is Low. Applications requiring reversible operation

must make the reversing decision while the activating clock is High

to avoid erroneous counts.

The Terminal Count Up (TC

) and Terminal Count Down (TCD)

U

outputs are normally High. When the circuit has reached the

maximum count state of 15, the next High-to-Low transition of CP

will cause TCU to go Low. TCU will stay Low until CPU goes High

again, duplicating the count up clock, although delayed by two gate

delays. Likewise, the TC

the zero state and the CP

output will go Low when the circuit is in

D

goes Low. The TC outputs can be used

D

as the clock input signals to the next higher order circuit in a

multistage counter, since they duplicate the clock waveforms.

and CPD respectively,

U

clock is

U

input will decrease the count by

D

input will advance the

U

U

Multistage counters will not be fully synchronous since there is a

two-gate delay time difference added for each stage that is added.

The counter may be preset by the asynchronous parallel load

capability of the circuit. Information present on the parallel Data

inputs (D0 - D3) is loaded into the counter and appears on the

outputs regardless of the conditions of the clock inputs when the

Parallel Load (PL

) input is Low. A High level on the Master Reset

(MR) input will disable the parallel load gates, override both clock

inputs, and set all Q outputs Low. If one of the clock inputs is Low

during and after a reset or load operation, the next Low-to-High

transition of the clock will be interpreted as a legitimate signal and

will be counted.

TYPICAL

TYPE

TYPICAL f

MAX

SUPPLY CURRENT

(TOTAL)

74F193 125MHz 32mA

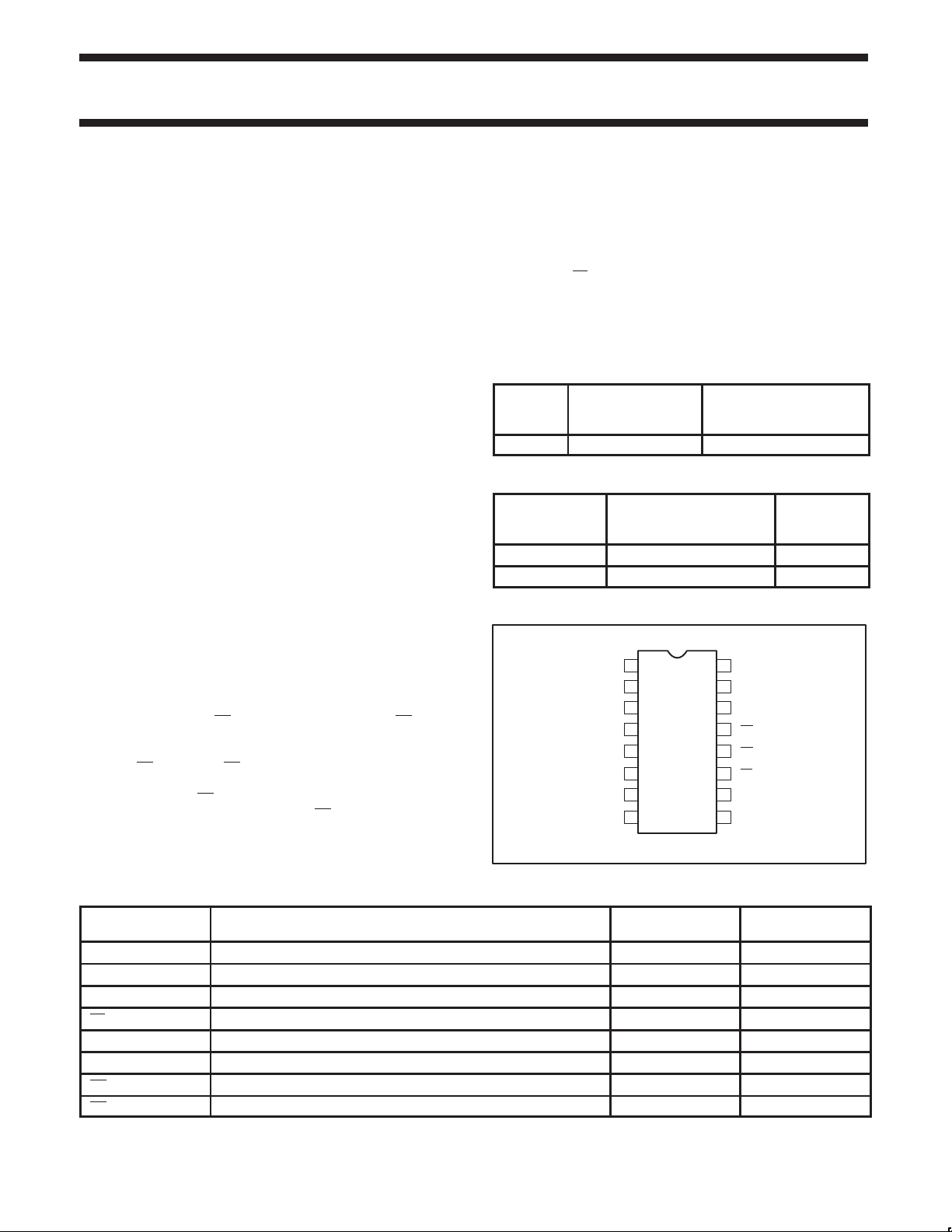

ORDERING INFORMATION

COMMERCIAL RANGE

DESCRIPTION

VCC = 5V ±10%,

T

= 0°C to +70°C

amb

PKG DWG #

16-pin plastic DIP N74F193N SOT38-4

16-pin plastic SO N74F193D SOT109-1

PIN CONFIGURATION

16

V

CC

D0

15

MR

14

13

TC

D

12

TC

U

PL

11

D2

10

D3

98

SF00745

Q1

Q0

CP

CP

Q2

Q3

GND

1D1

2

3

4

D

5

U

6

7

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

D0 - D3 Data inputs 1.0/1.0 20µA/0.6mA

CP

CP

U

D

Count up clock input (active rising edge) 1.0/3.0 20µA/1.8mA

Count down clock input (active rising edge) 1.0/3.0 20µA/1.8mA

PL Asynchronous parallel load control input (active Low) 1.0/1.0 20µA/0.6mA

MR Asynchronous master reset input 1.0/1.0 20µA/0.6mA

Q0 - Q3 Flip-flop outputs 50/33 1.0mA/20mA

TC

TC

U

D

Terminal count up (carry) output (active Low) 50/33 1.0mA/20mA

Terminal count down (borrow) output (active Low) 50/33 1.0mA/20mA

NOTE: One (1.0) FAST Unit Load (U.L.) is defined as: 20µA in the High state and 0.6mA in the Low state.

1995 Jul 17

2

LOAD VALUE

HIGH/LOW

853-0353 15459

Philips Semiconductors Product specification

74F193Up/down binary counter with separate up/down clocks

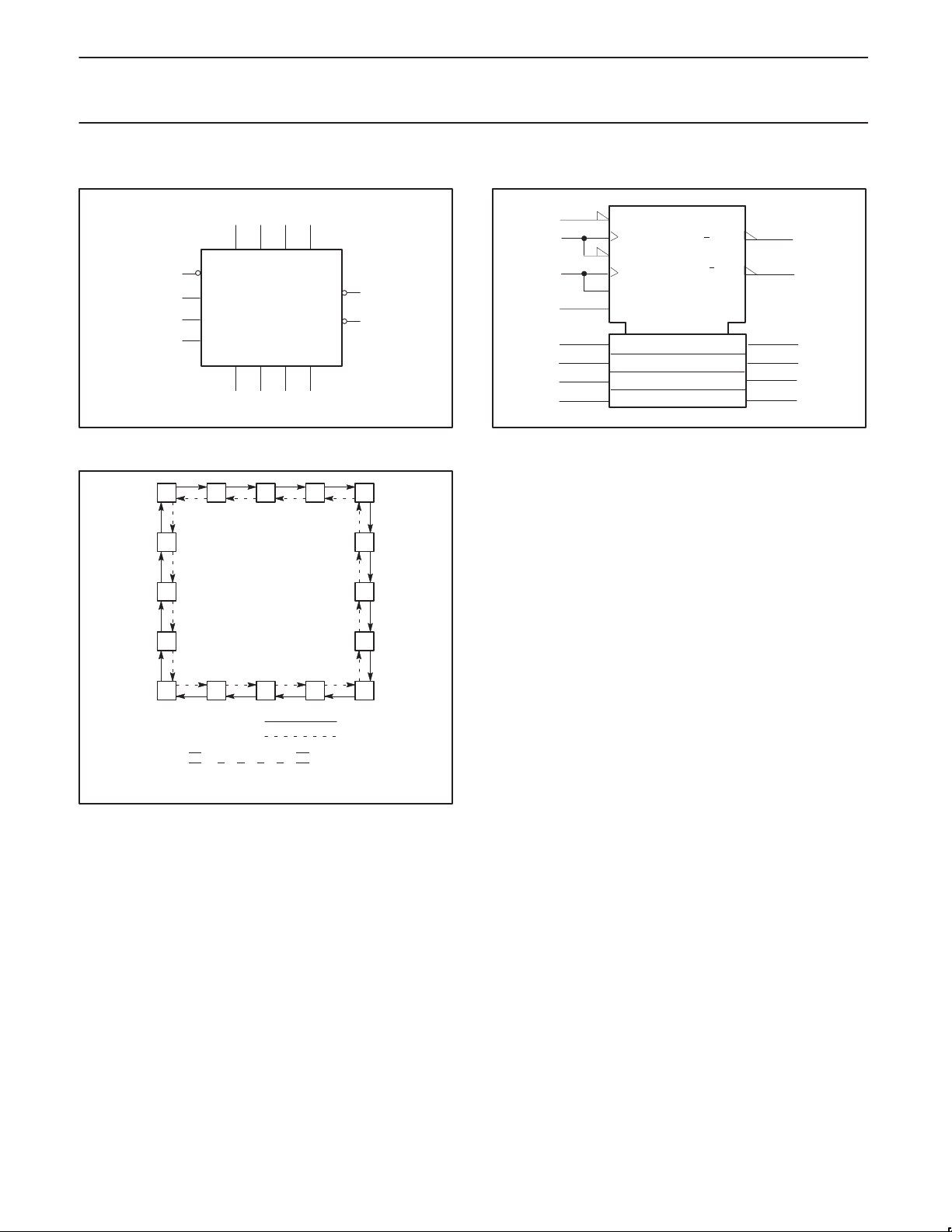

LOGIC SYMBOL

11

5

4

14

VCC = Pin 16

GND = Pin 8

STATE DIAGRAM

01234

15

14

15 1 10 9

D0 D1Q1D2

PL

CP

U

CP

D

MR

Q0

D3

Q2 Q3

LOGIC SYMBOL (IEEE/IEC)

11

5

4

U

D

SF00746

12

13

5

6

14

15

1

10

9

TC

TC

7623

C3

G1

G2

R

2+

1–

3D

CTR DIV 16

[1]

[2]

[4]

[8]

CT=15

1

2CT=0

12

13

3

2

6

7

SF00747

13

COUNT UP

COUNT DOWN

TCU = Q0 . Q1 . Q2 . Q3 . CP

TCD = Q0 . Q1 . Q2 . Q3 . CP

Logic Equations for Terminal Count

7

89101112

U

D

SF00748

1995 Jul 17

3

Philips Semiconductors Product specification

74F193Up/down binary counter with separate up/down clocks

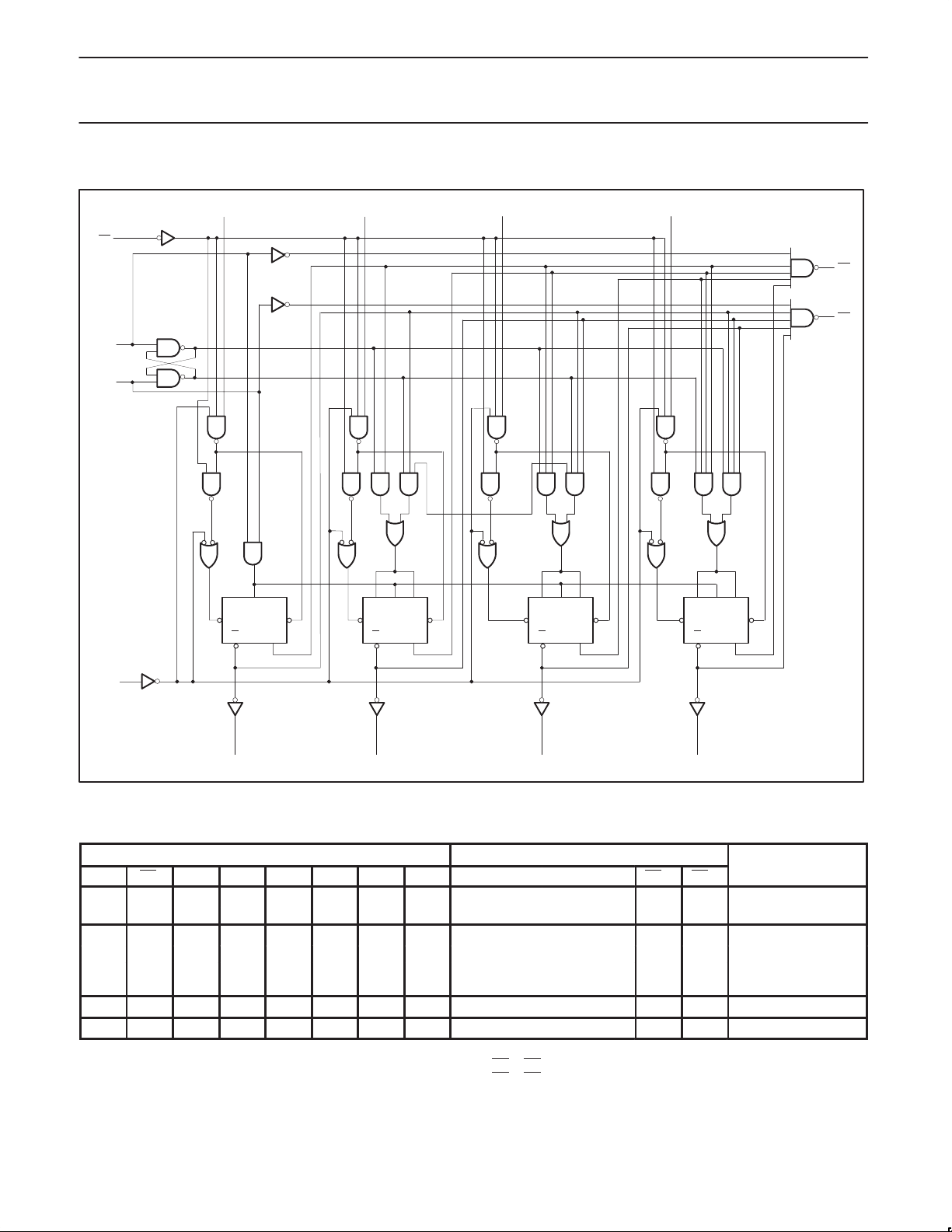

LOGIC DIAGRAM

CP

CP

D0 D1 D3

11

PL

5

U

4

D

15 1

KJ

CP

S

R

D

D

Q

Q

J

CP

S

R

D

D

Q

Q

D2

10

KJ

CP

S

R

D

D

Q

Q

9

12

TC

U

13

TC

D

K

JQCP

S

R

D

D

Q

14

MR

V

= Pin 16

CC

GND = Pin 8

23

Q1Q0

Q1

6

7

Q1

FUNCTION TABLE

INPUTS OUTPUTS OPERATING

MR PL CPUCP

H X X L X X X X L L L L H L Reset (clear)

H X X H X X X X L LLLHH

L L X L L L L L L L L L H L

L L X H L L L L L LLLHH Parallel load

L L L X H H H H H HHHLH

L L H X H H H H H HHHHH

L H ↑ H X X X X Count up H

L H H ↑ X X X X Count down H H2Count down

H = High voltage level

L = Low voltage level

X = Don’t care

↑ = Low-to-High clock transition

D0 D1 D2 D3 Q0 Q1 Q2 Q3 TCUTC

D

NOTES:

TC

=CPU at terminal count up (HHHH)

U

=CPD at terminal count down (LLLL)

TC

D

1

D

H Count up

SF00749

MODE

1995 Jul 17

4

Loading...

Loading...