Philips 74F1763 Technical data

查询N74F1763N供应商

INTEGRATED CIRCUITS

74F1763

Intelligent DRAM controller (IDC)

Product specification

Supersedes data of 1989 Nov 17

IC15 Data Handbook

1999 Jan 08

Philips Semiconductors Product specification

74F1763Intelligent DRAM controller (IDC)

FEA TURES

•DRAM signal timing generator

•Automatic refresh circuitry

•Selectable row address hold and RAS precharge times

•Facilitates page mode accesses

•Controls 1 MBit DRAMs

•Intelligent burst-mode refresh after page-mode access cycles

ability to select the RAS

to fit the particular DRAMs being used. DTACK

from previous family parts to become a negative true, tri-stated

output. The options for latched or unlatched address are contained

on a single device by the addition of an Address Latch Enable (ALE

input. Finally , a burst refresh monitor has been added to ensure

complete refreshing after length page-mode access cycles. With a

maximum clock frequency of 100 MHz, the F1763 is capable of

controlling DRAM arrays with access times down to 40 nsec.

precharge time and Row-Address Hold time

has been modified

)

PRODUCT DESCRIPTION

The Philips Semiconductors Intelligent Dynamic RAM Controller is a

1 MBit, single-port version of the 74F1764 Dual Port Dynamic RAM

Controller. It contains automatic signal timing, address multiplexing

and refresh control required for interfacing with dynamic RAMs.

Additional features have been added to this device to take

advantage of technological advances in Dynamic RAMs. A

Page-Mode access pin allows the user to assert RAS

access cycle rather than the pre-defined four-clock-cycle pulse width

used for normal random access cycles. In addition, the user has the

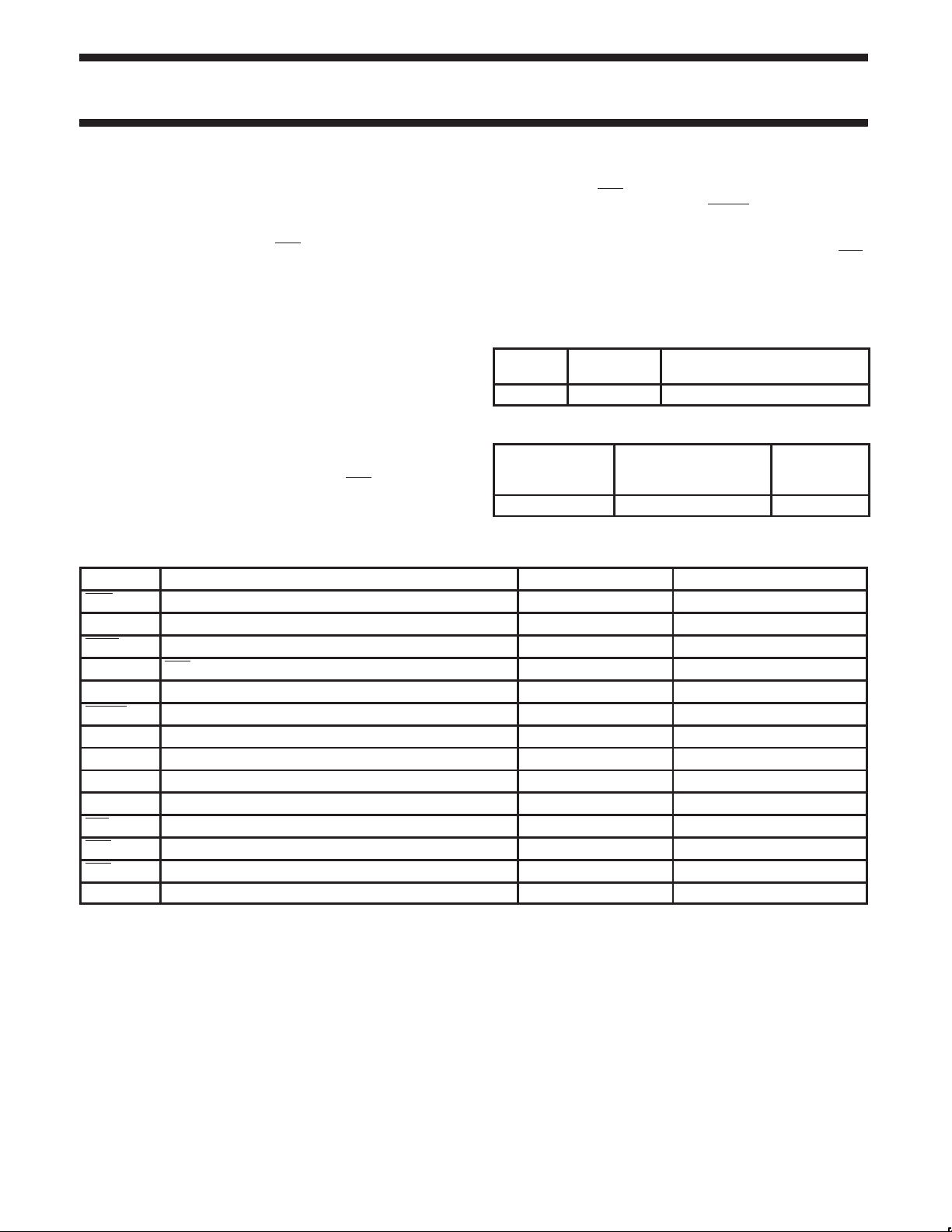

INPUT AND OUTPUT LOADING FAN-OUT TABLE

PINS

REQ DRAM Request Input 1.0/1.0

CP Clock Input 1.0/1.0

PAGE Page Mode Select Input 1.0/1.0

PRECHRG RAS Precharge Select Input 1.0/1.0

HLDROW Row Hold Select Input 1.0/1.0

DTACK Data Transfer Ack. Output 50/80 35 mA/60 mA

GNT Access Grant Output 50/80 35 mA/60 mA

RCP Refresh Clock Input 1.0/1.0

RA0–9 Row Address Inputs 1.0/1.0

CA0–9 Column Address Inputs 1.0/1.0

ALE Address Latch Enable Input 1.0/1.0

RAS Row Address Strobe Output NA 35 mA/60 mA

CAS Column Address Strobe Output NA 35 mA/60 mA

MA0–9 DRAM Address Outputs NA 35 mA/60 mA

NOTES:

One (1.0) FAST Unit Load is defined as 20 A in the HIGH state and 0.6 mA in the LOW state.

FAST Unit Loads do not correspond to DRAM Input Loads. See Functional Description for details.

DESCRIPTION 74F (U.L.) HIGH/LOW LOAD VALUE HIGH/LOW

for the entire

NO TAG

TYPE

74F1763 100 MHz 150 mA

ORDERING INFORMATION

PACKAGES

48-pin Plastic DIP N74F1763N SOT240-1

f

MAX

COMMERCIAL RANGE

TYPICAL SUPPL Y CURRENT

VCC = 5V 10%;

= 0C TO 70C

T

A

(TOTAL)

20 A/0.6 mA

20 A/0.6 mA

20 A/0.6 mA

20 A/0.6 mA

20 A/0.6 mA

20 A/0.6 mA

20 A/0.6 mA

20 A/0.6 mA

20 A/0.6 mA

PKG DWG #

1999 Jan 08 853–1406 20619

2

Philips Semiconductors Product specification

74F1763Intelligent DRAM controller (IDC)

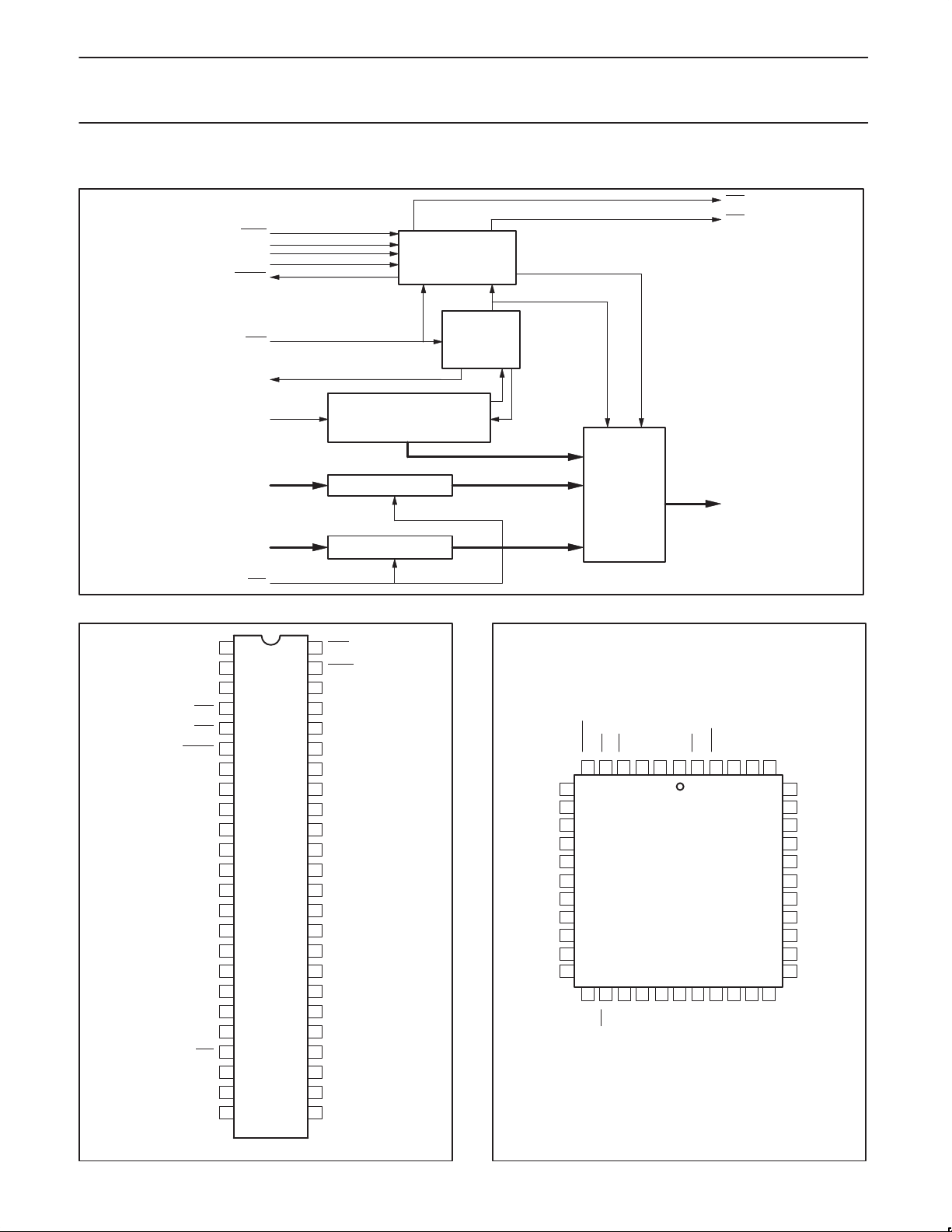

BLOCK DIAGRAM

RAS

PAGE

CP

PRECHRG

HLDROW

DTACK

RAS, CAS, MUX, DTACK

TIMING

CAS

REQ

GNT

RCP

RA0–9

CA0–9

ALE

DIP PIN CONFIGURATION

GNT

1

HLDROW

PRECHRG

2

3

4

RAS

5

CAS

6

DTACK

7

MA0

8

MA1

9

MA2

10

MA3

11

GND

12 37

GND

13

GND

14

GND

15

MA4

16

MA5

17

MA6

18 31

MA7

19 30

MA8

20

MA9

21

ALE

22

CA9

23

RA9

24 25

CA8

BURST REFRESH MONITOR

REFRESH ADDRESS COUNTER

ROW ADDRESS LATCH

COLUMN ADDR. LATCH

REQ

48

47

PAGE

46

CP

45

RCP

44

RA0

43

CA0

42

RA1

CA1

41

40

RA2

39

CA2

38

V

CC

V

CC

36

V

CC

RA3

35

34

CA3

RA4

33

32

CA4

RA5

CA5

29

RA6

28

CA6

27

RA7

26

CA7

RA8

REFRESH

ARBITRATION

MULTIPLEXER

PLCC PIN CONFIGURA TION

DTACK

6

7

MA0

8

MA1

9

MA2

10

MA3

11

GND

12

GND

13

MA4

MA5

14

MA6

15

16

MA7

17

MA8

18 19 20 21 22 24 25 26 27 28

MA9

MA0–9

SF01400

CAS

RAS

PRECHRG

HLDROW

5 4 32 144 43 42 41 40

ALE

CA9

RA9

CA8

PAGECPRCP

GNT

REQ

23

RA8

CA7

RA7

CA6

RA6

RA0

CA5

39

CA0

38

RA1

37

CA1

36

RA2

35

CA2

34

V

CC

33

RA3

32

CA3

31

RA4

30

CA4

29

RA5

1999 Jan 08

SF01401

SF01402

3

Philips Semiconductors Product specification

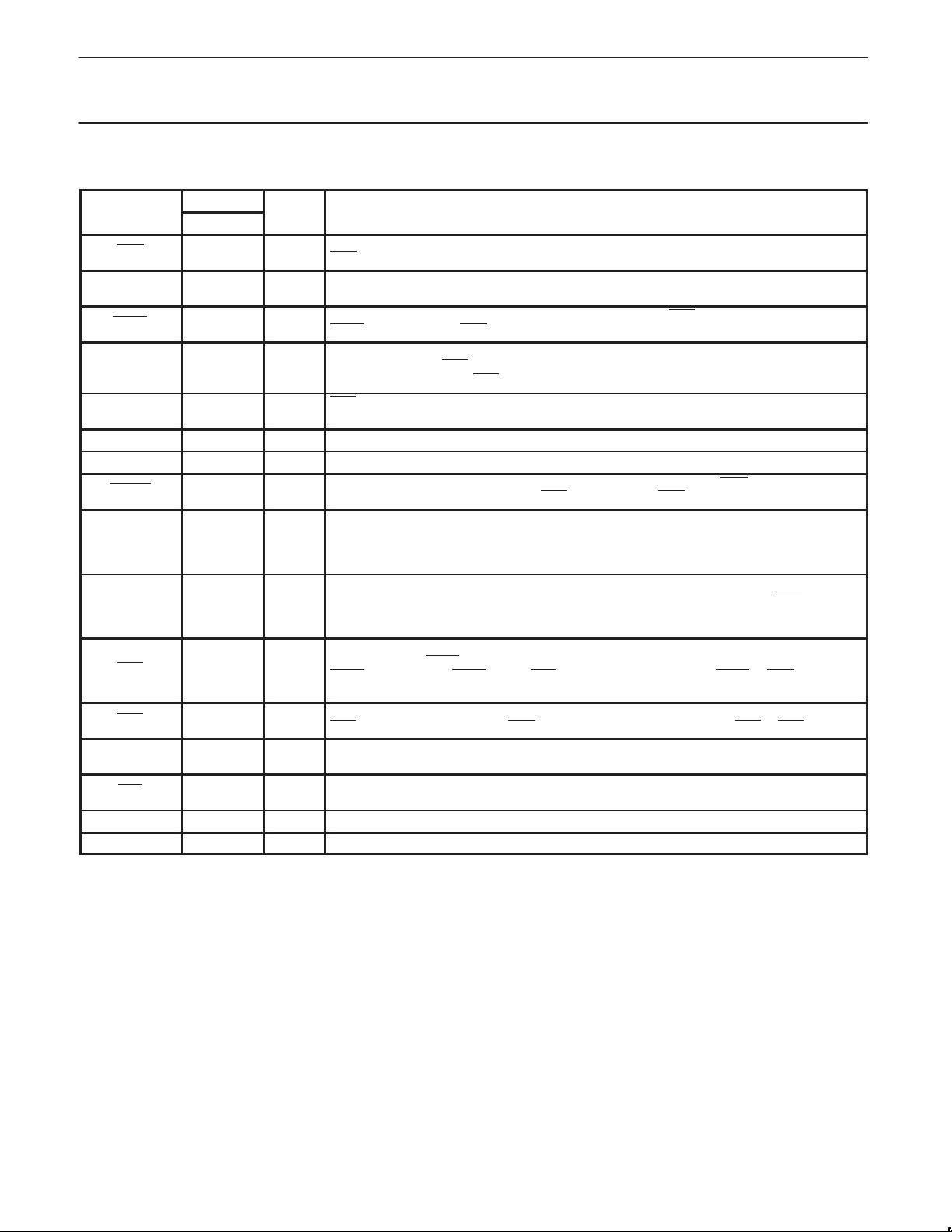

SYMBOL

TYPE

NAME AND FUNCTION

74F1763Intelligent DRAM controller (IDC)

PIN DESCRIPTION

PINS

DIP

REQ 48 Input

GNT 1 Output

PAGE 47 Input

HLDROW 2 Input

PRECHRG 3 Input

CP 46 Input Clock input. Used by the Controller for all timing and arbitration functions.

RCP 45 Input Refresh Clock input. Divided internally by 64 to produce an internal Refresh Request.

DTACK 6 Output

44, 42, 40,

RA0–9

CA0–9

RAS 4 Output

CAS 5 Output

MA0–9

ALE 21 Input

V

CC

GND 11–14 Ground

35, 33, 31,

29, 27, 25,

23

43, 41, 39,

34, 32, 30,

28, 26, 24,

22

7–10,

15–20

36–38 +5V 10% Supply voltage.

Inputs Row Address inputs.

Inputs

Output

Active Low Memory Access Request input, must be asserted for the entire DRAM access cycle.

REQ is sampled on the rising edge of the CP clock.

Active High Grant output. When High indicates that a DRAM access (inactive during refresh)

cycle has begun. Asserted from the rising edge of the CP clock.

Active Low Page-Mode Access input. Forces the IDC to keep RAS asserted for as long as the

PAGE input is Low and REQ is asserted Low.

Row Address Hold input. If Low will configure the IDC to maintain the row addresses for a full

CP clock cycle after RAS is asserted. If High will program the IDC to maintain row addresses for

a 1/2 CP clock cycle after RAS

RAS Precharge input. A Low will program the IDC to guarantee a minimum of 4 CP clock cycles

of precharge. A High will guarantee 3 clock cycles of precharge.

Active Low, 3-state Data T ransfer Acknowledge output. Enabled by the REQ input and asserted

four clock cycles after the assertion of RAS, 3-stated when REQ goes High.

Column Address inputs. Propagated to the MA0–9 outputs 1 CP clock cycle after RAS is

asserted, if HLDROW = 0 or 1/2 clock cycle later if HLDROW is 1.

Active Low Row Address Strobe. Asserted for four clock cycles during each refresh cycle

regardless of the PAGE input. Also asserted for four clock cycles during processor access if the

PAGE

input is High. If PAGE is Low, RAS is negated upon negation of PAGE or REQ, whichever

occurs first.

Active Low Column Address Strobe. Always asserted 1.5 CP clock cycles after the assertion of

RAS. Negated upon negation of REQ. HLDROW input pin does not affect RAS to CAS timing.

DRAM multiplexed address outputs. Row and column addresses asserted on these pins during

an access cycle. Refresh counter addresses presented on these outputs during refresh cycles.

Active Low Address Latch Enable input. A Low on this pin will cause the address latches to be

transparent. A High level will latch the RA0–9 and CA0–9 inputs.

is asserted.

1999 Jan 08

4

Philips Semiconductors Product specification

74F1763Intelligent DRAM controller (IDC)

FUNCTIONAL DESCRIPTION

The 74F1763 1 Megabit Intelligent DRAM Controller (IDC) is a

synchronous device with most signal timing being a function of the

CP input clock.

Arbitration

Once the DRAM’s RAS precharge time has been satisfied, the REQ

input is sampled on each rising edge of the CP clock and an

internally generated refresh request is sampled on each falling edge

of the same clock. When only one of these requests is sampled as

active the appropriate memory cycle will begin immediately. For a

memory access cycle this will be indicated by GNT and RAS

both being asserted and for a refresh cycle by multiplexing refresh

address to the MA0–9 outputs and subsequent assertion of RAS

after 1/2CP clock cycle. If both memory access and refresh requests

are active at a given time the request sampled first will begin

immediately and the other request (if still asserted) will be serviced

upon completion of the current cycle and it’s associated RAS

precharge time.

outputs

Memory access

The row (RA0–9) and column (CA0–9) address inputs are latched

when ALE

propagate directly to the outputs. When GNT and RAS

after a REQ

already propagated to the MA0–9 outputs for the row address. One

or one-half CP clock cycles later (depending on the state of the

HLDROW input) the column address (CA0–9) inputs are propagated

to the MA0–9 outputs. CAS

clock cycles after RAS

will be negated approximately four CP clock cycles after its initial

assertion. At this time the DTACK

the completion of a memory access cycle. The IDC will maintain the

state of all its outputs until the REQ

waveforms).

input is High. When ALE is Low the input addresses

are asserted,

has been sampled the RA0–9 address inputs will have

is always asserted one and one-half CP

is asserted. If the PAGE input is High, RAS

output becomes valid indicating

input is negated ( see timing

Row address hold times

If the HLDROW input of the IDC is High the row address outputs will

remain valid 1/2 CP clock cycle after RAS

HLDROW input is Low the row address outputs will remain valid one

CP clock cycle after RAS

is asserted.

is asserted. If the

RAS precharge timing

In order to meet the RAS precharge requirement of dynamic RAMs,

the controller will hold-off a subsequent RAS

a processor access request or a refresh cycle for four or three full

CP clock cycles from the previous negation of RAS

the state of the PRECHRG input. If the PRECHRG input is Low,

RAS

remains High for at least 4 CP clock cycles. If the PRECHRG

input is High RAS

remains High for at least 3 CP clock cycles.

signal assertion due to

, depending on

Refresh timing

The refresh address counter wakes-up in an all 1’s state and is an

up counter. The refresh clock (RCP) is internally divided down by 64

to produce an internal refresh request. This refresh request is

recognized either immediately or at the end of a running memory

access cycle. Due to the possibility that page mode access cycles

may be lengthy, the controller keeps track of how many refresh

requests have been missed by logging them internally (up to 128)

and servicing any pending refresh requests at the end of the

memory access cycle. The controller performs RAS

cycles until all pending refresh requests are depleted.

-only refresh

Page-mode access

Fast accesses to consecutive locations of DRAM can be realized by

asserting the PAGE

mode, the controller does not automatically negate RAS

CP clock cycles, but keeps it asserted throughout the access cycle.

By using external gates, the CAS

while changing the column address inputs to the controller, which

will propagate to the MA

column address. This is only useful if the ALE

the user to charge addresses. This mode can be used with DRAMs

that support page or nibble mode addressing.

input as shown in the timing waveforms. In this

after four

output can be gated on and off

–MA9 address outputs and provide a new

0

input is Low, enabling

Output driving characteristics

Considering the transmission line characteristic of the DRAM arrays,

the outputs of the IDC have been designed to provide incident-edge

switching (in Dual-Inline-Packaged memory arrays), needed in high

performance systems. For more information on the driving

characteristics, please refer to Philips Semiconductors application

note AN218. The driving characteristics of the 74F1763 are the

same as those of the 74F765 shown in the application note.

1999 Jan 08

5

Loading...

Loading...