Philips 74f112 DATASHEETS

INTEGRATED CIRCUITS

74F112

Dual J-K negative edge-triggered flip-flop

Product specification

IC15 Data Handbook

1990 Feb 09

Philips Semiconductors Product specification

74F1 12Dual J-K negative edge-triggered flip-flop

FEA TURE

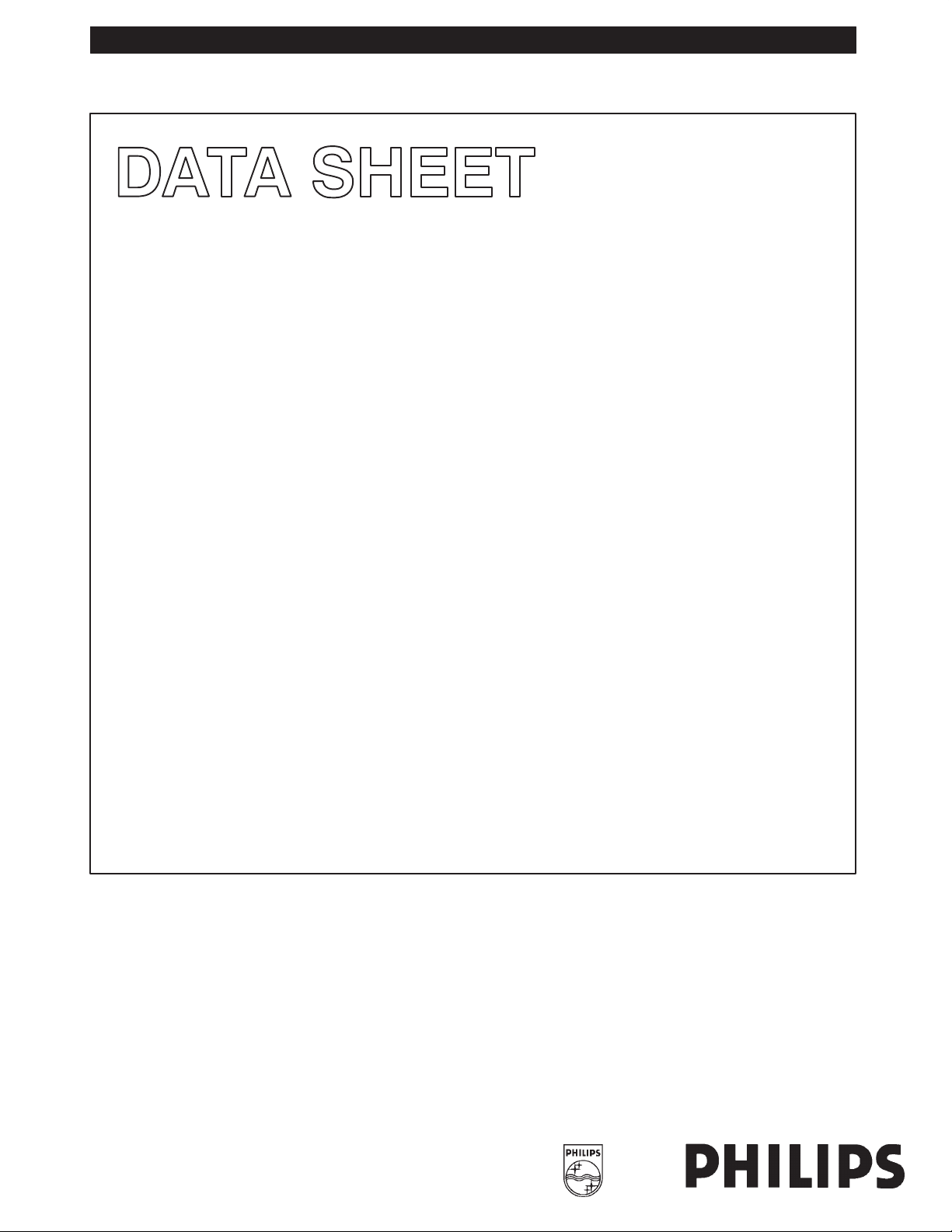

PIN CONFIGURATION

•Industrial temperature range available (–40°C to +85°C)

1

0

CP

2

DESCRIPTION

The 74F112, Dual Negative Edge-Triggered JK-Type Flip-Flop,

feature individual J, K, Clock (CP

inputs, true (Qn) and complementary (Q

The SD and RD inputs, when Low, set or reset the outputs as shown

in the Function Table, regardless of the level at the other inputs.

A High level on the clock (CP

n), Set (SD) and Reset (RD)

n) outputs.

n) input enables the J and K inputs and

K0

J0

3

S

4

D0

5

Q0

0

6

Q

Q

1

data will be accepted. The logic levels at the J and K inputs may be

allowed to change while the CP

n is High and flip-flop will perform

according to the Function Table as long as minimum setup and hold

times are observed. Output changes are initiated by the High-to-Low

transition of the CP

n.

TYPE TYPICAL PROPAGATION DELAY TYPICAL SUPPLY CURRENT (TOTAL)

74F112 100MHz 15mA

ORDERING INFORMATION

ORDER CODE

DESCRIPTION

16-pin plastic DIP N74F112N I74F1 12N SOT38-4

16-pin plastic SO N74F112D I74F1 12D SOT109-1

COMMERCIAL RANGE

VCC = 5V ±10%, T

= 0°C to +70°C

amb

VCC = 5V ±10%, T

INDUSTRIAL RANGE

= –40°C to +85°C

amb

16

15

14

13

12

11

107

98GND Q1

SF00103

V

R

R

CP1

K1

J1

SD1

CC

D0

D1

PKG DWG #

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION 74F (U.L.) HIGH/LOW LOAD VALUE HIGH/LOW

J0, J1 J inputs 1.0/1.0 20µA/0.6mA

K0, K1 K inputs 1.0/1.0 20µA/0.6mA

SD0, SD1 Set inputs (active Low) 1.0/5.0 20µA/3.0mA

RD0, RD1 Reset inputs (active Low) 1.0/5.0 20µA/3.0mA

CP0, CP1 Clock Pulse input (active falling edge) 1.0/4.0 20µA/2.4mA

Q0, Q0; Q1, Q1 Data outputs 50/33 1.0mA/20mA

NOTE:

One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state.

February 9, 1990 853–0338 98775

2

Philips Semiconductors Product specification

OPERATING MODE

74F112Dual J-K negative edge-triggered flip-flop

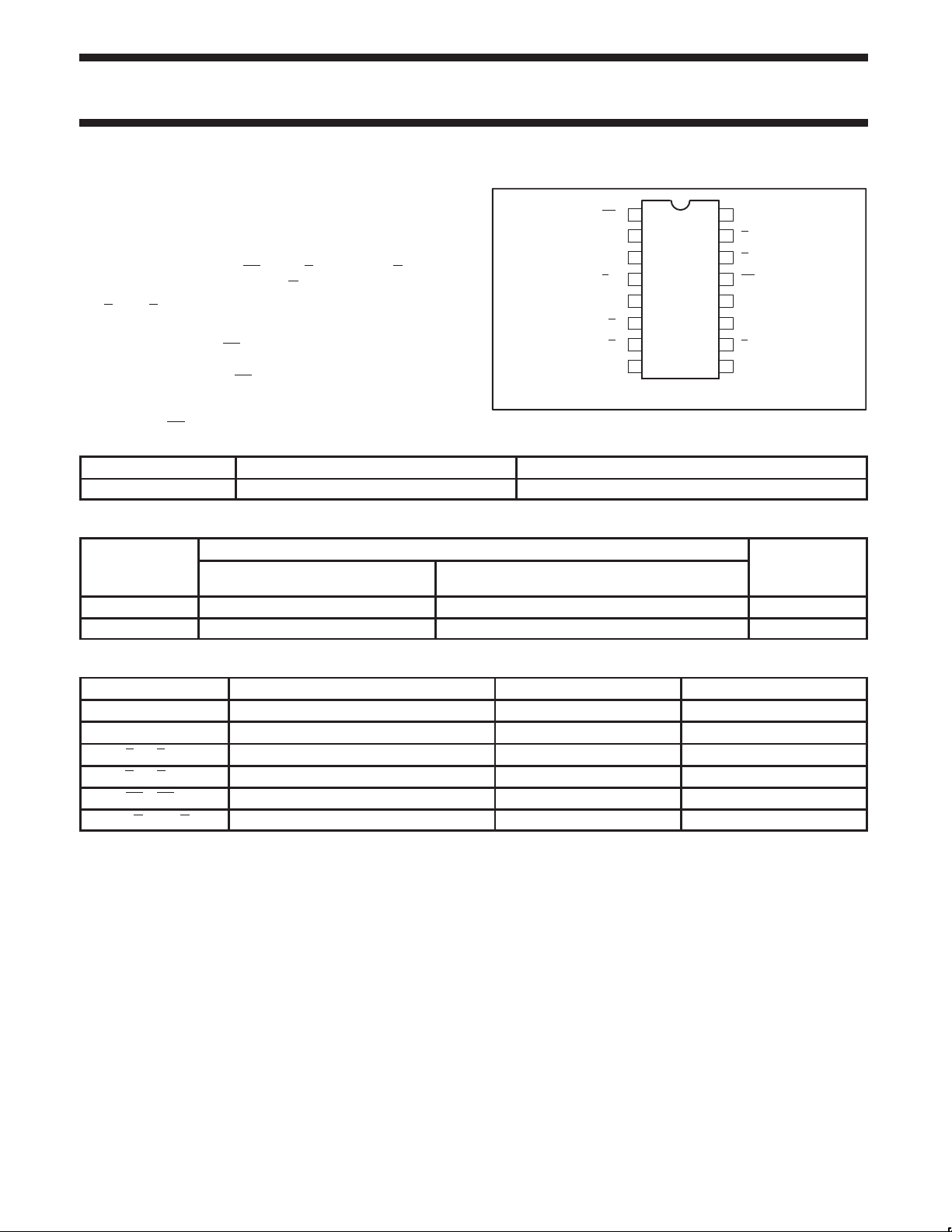

LOGIC SYMBOL

1

4

15

13

10

14

VCC = Pin 16

GND = Pin 8

LOGIC DIAGRAM

311

J1 K0

CP0

SD0

RD0

CP1

SD1

RD1

Q0 Q0 Q1 Q1

56 97

Qn

4, 10

S

Dn

2, 12

Kn

212

SF00104

5, 9

IEC/IEEE SYMBOL

3

1

K1J0

2

15

4

11

13

12

14

10

1J

C1

1K

R

S

2J

C2

2K

R

S

6, 7

n

Q

15, 14

R

Dn

3, 11

Jn

5

6

9

7

SF00105

VCC = Pin 16

GND = Pin 8

CP

1, 13

n

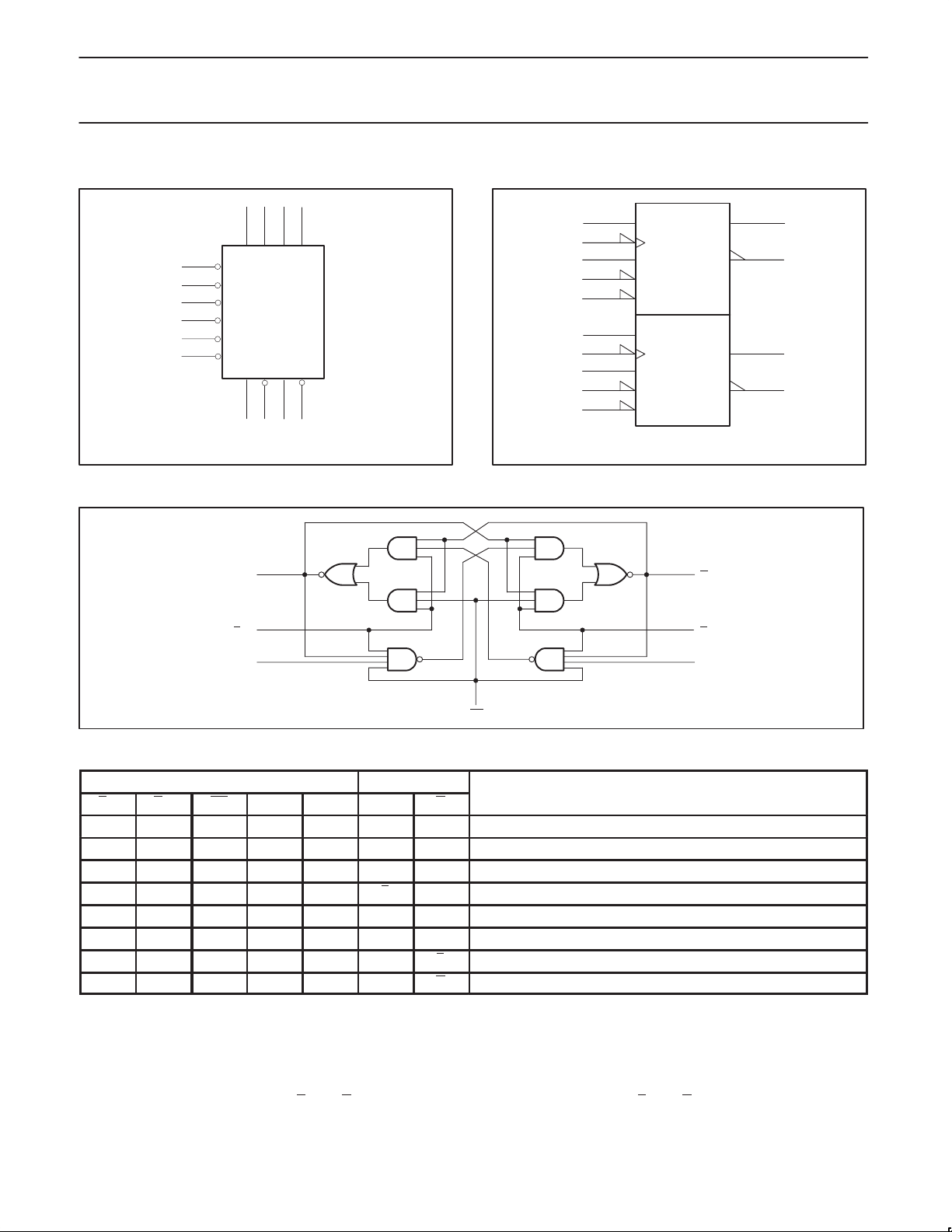

FUNCTION TABLE

INPUTS OUTPUTS

SD RD CP J K Q Q

L H X X X H L Asynchronous Set

H L X X X L H Asynchronous Reset

L L X X X H* H* Undetermined *

H H ↓ h h q q Toggle

H H ↓ l h L H Load “0” (Reset)

H H ↓ h l H L Load “1” (Set)

H H ↓ l l q q Hold “no change”

H H H X X Q Q Hold “no change”

H = High voltage level

h = High voltage level one setup time prior to High-to-Low clock transition

L = Low voltage level

l = Low voltage level one setup time prior to High-to-Low clock transition

q = Lower case letters indicate the state of the reference output prior to the High-to-Low clock transition

X = Don’t care

↓ = High-to-Low clock transition

* = Both outputs will be High while both S

D and RD are Low, but the output states are unpredictable if SD and RD go High simultaneously.

SF00106

February 9, 1990

3

Loading...

Loading...