Philips 74ALVCHS162830 Technical data

INTEGRATED CIRCUITS

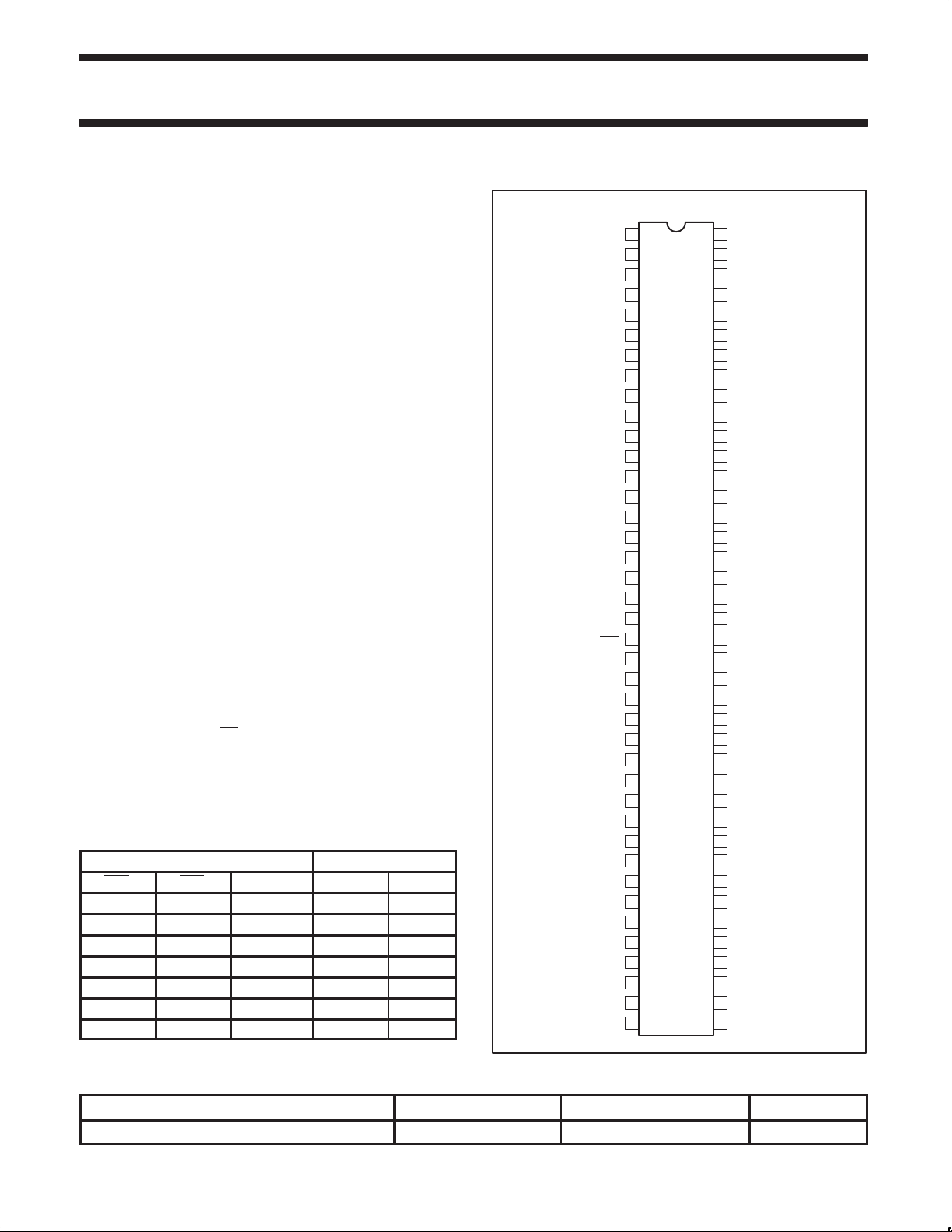

74ALVCHS162830

18-bit to 36-bit address driver

with bus hold (3-State)

Product data 2001 Sep 07

File under Integrated Circuits — ICL03

Philips Semiconductors Product data

74ALVCHS16283018-bit to 36-bit address driver with bus hold (3-State)

FEA TURES

•Output ports have equivalent 26 Ω series resistors, so no external

resistors are required

•Diodes on inputs clamp overshoot

•ESD classification testing is done to JEDEC Standard JESD22.

Protection exceeds 2000 V HBM per method A114.

•Latch-up testing is done to JEDEC Standard JESD78, which

exceeds 100 mA.

•Bus hold on data inputs eliminates the need for external

pullup/pulldown resistors

•Packaged in thin very small-outline package (TVSOP) — 0.4 mm

pitch

•Optimized for use with PCK953 in SDRAM module applications

•Balanced ±12 mA output drive

•Low noise, low skew

DESCRIPTION

The ALVCHS162830 address driver is designed for 2.3 V to 3.6 V

V

operation.

CC

Diodes to VCC have been added on the inputs to clamp overshoot.

The bus hold feature retains the inputs’ last state whenever the input

bus goes to high impedance. This prevents floating inputs and

eliminates the need for pull up or pull down resistors.

The outputs, which are designed to sink up to 12 mA, include

equivalent 26 Ω series resistors to reduce overshoot and

undershoot.

To ensure the high-impedance state during power up or power

down, the output-enable (OE

pullup resistor; the minimum value of the resistor is determined by

the current-sinking capability of the driver.

The 74ALVCHS162830 is characterized for operation from –40 to

+85 °C.

FUNCTION TABLE

Inputs Outputs

OE1 OE2 A 1Yn 2Yn

L H H H Z

L H L L Z

H L H Z H

H L L Z L

L L H H H

L L L L L

H H X Z Z

) input should be tied to VCC through a

PIN CONFIGURA TION

2Y2

1

2

1Y2

3

GND

4

2Y1

5

1Y1

6

V

CC

7

A1

8

A2

9

GND

10

A3

11

A4

12 69

GND

13

A5

14

A6

15

V

CC

16

A7

17

A8

18 63

GND

19 62

A9

20

OE1

21

OE2

22

A10

23

GND

24

A11

25 56

A12

26 55

V

CC

A13

27 54

28

A14

GND

29

30

A15

31

A16

32 49

GND

33 48

A17

34 47

A18

V

35 46

CC

36

2Y18

1Y18

37

38

GND

39

2Y17

40 41

1Y17

TOP VIEW

1Y3

80

79

2Y3

78

GND

77

1Y4

76

2Y4

75

V

CC

74

1Y5

2Y5

73

72

GND

71

1Y6

70

2Y6

GND

68

1Y7

2Y7

67

66

V

CC

1Y8

65

64

2Y8

GND

1Y9

61

2Y9

60

1Y10

59

2Y10

58

GND

57

1Y11

2Y11

V

CC

1Y12

53

2Y12

52

GND

51

1Y13

50

2Y13

GND

1Y14

2Y14

V

CC

45

1Y15

2Y15

44

GND

43

42

1Y16

2Y16

SW00723

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE ORDER CODE DWG NUMBER

80-pin plastic thin very small outline (TVSOP) –40 to +85 °C 74ALVCHS162830DGB SOT647-1

2001 Sep 07 853-2279 27052

2

Philips Semiconductors Product data

18-bit to 36-bit address driver with bus hold

(3-State)

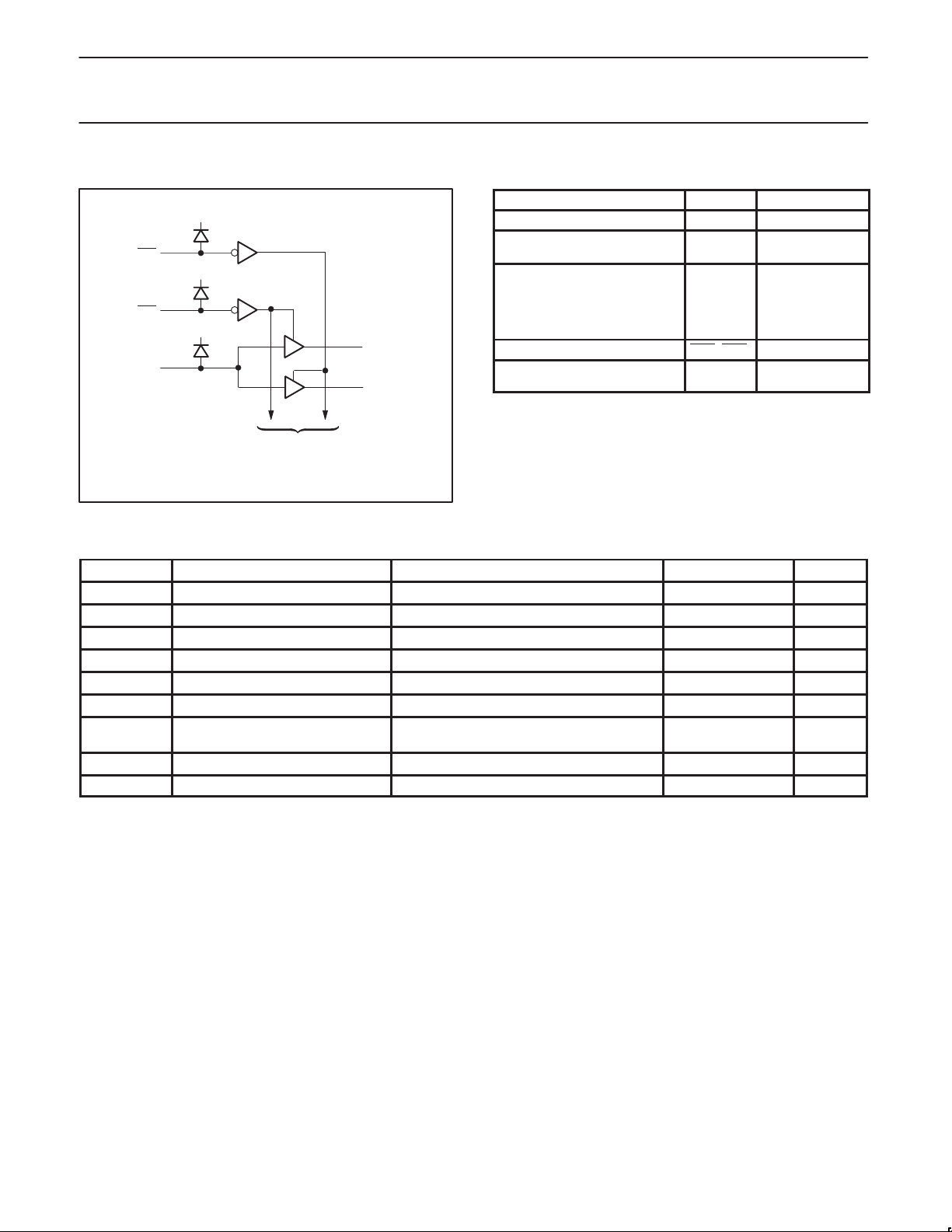

LOGIC DIAGRAM (POSITIVE LOGIC)

V

CC

21

OE2

V

CC

20

OE1

V

CC

7

A1

to 17 other channels

5

1Y1

4

2Y1

SW00724

74ALVCHS162830

PIN DESCRIPTION

PIN(S) SYMBOL FUNCTION

6, 15, 26, 35, 46, 55, 66, 75 V

7, 8, 10, 11, 13, 14, 16, 17, 19,

22, 24, 25, 27, 28, 30, 31, 33, 34

1, 2, 4, 5, 36, 37, 39, 40, 41, 42,

CC

An Inputs

1Yn, 2Yn Outputs

44, 45, 47, 48, 50, 51, 53, 54,

56, 57, 59, 60, 61, 62, 64, 65,

67, 68, 70, 71, 73, 74, 76, 77,

79, 80

20, 21 OE1, OE2 Output enable

3, 9, 12, 18, 23, 29, 32, 38, 43,

49, 52, 58, 63, 69, 72, 78

GND Ground

Supply voltage

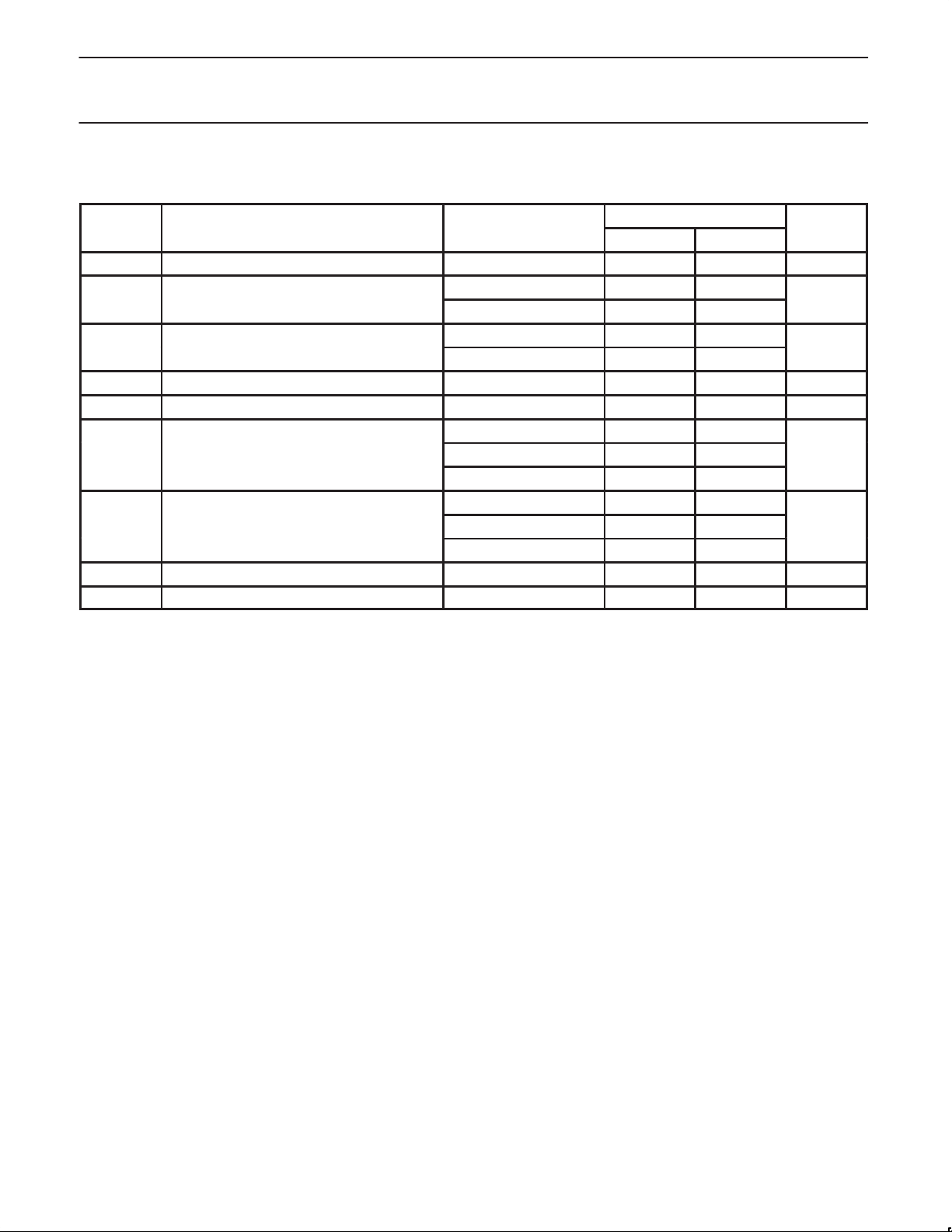

ABSOLUTE MAXIMUM RATINGS

Over recommended operating free-air temperature range (unless otherwise noted).

SYMBOL PARAMETER CONDITIONS RATING UNIT

V

ICC, I

Θ

T

CC

V

I

V

O

I

IK

I

OK

I

O

GND

JA

stg

Supply voltage range –0.5 to +4.6 V

Input voltage range See Note 2 –0.5 to +4.6 V

Output voltage range See Notes 2 and 3 –0.5 to VCC +0.5 V

Input clamp current VI < 0 –50 mA

Output clamp current VO < 0 –50 mA

Continuous output current "50 mA

Continuous current through each V

or GND

CC

Package thermal impedance See Note 4 106 °C/W

Storage temperature range –65 to +150 °C

NOTES:

1. Stresses beyond those listed under ”absolute maximum ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under ”recommended operating

conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

3. This value is limited to 4.6 V maximum.

4. The package thermal impedance is calculated in accordance with JESD 51.

1

"100 mA

2001 Sep 07

3

Philips Semiconductors Product data

SYMBOL

PARAMETER

CONDITIONS

UNIT

V

High-level input voltage

V

V

Low-level input voltage

V

18-bit to 36-bit address driver with bus hold

(3-State)

RECOMMENDED OPERATING CONDITIONS

All unused control inputs of the device must be held at VCC or GND to ensure proper device operation.

V

CC

IH

IL

V

V

O

I

OH

I

OL

∆t/∆v Input transition rise or fall rate 10 ns/V

T

amb

Supply voltage 2.3 3.6 V

p

p

Input voltage 0 V

I

Output voltage 0 V

High-level output current

Low-level output current

Operating free-air temperature –40 +85 °C

VCC = 2.3 V to 2.7 V 1.7

VCC = 2.7 V to 3.6 V 2

VCC = 2.3 V to 2.7 V 0.7

VCC = 2.7 V to 3.6 V 0.8

VCC = 2.3 V –6

VCC = 2.7 V –8

VCC = 3 V –12

VCC = 2.3 V 6

VCC = 2.7 V 8

VCC = 3 V 12

74ALVCHS162830

LIMITS

MIN MAX

CC

CC

V

V

mA

mA

2001 Sep 07

4

Loading...

Loading...