Philips 74ALVCH32501 Datasheet

INTEGRATED CIRCUITS

DATA SH EET

74ALVCH32501

36-bituniversalbustransceiverwith

direction pin; 5 V tolerant; 3-state

Product specification

File under Integrated Circuits, IC24

2000 Mar 16

Philips Semiconductors Product specification

36-bit universal bus transceiver with direction pin;

5 V tolerant; 3-state

FEATURES

• 3-state non-inverting outputs for bus oriented

applications

• Wide supply voltage range of 1.2 to 3.6 V

• Complies with JEDEC standard no. 8-1A

• Current drive ±24 mA at 3.0 V

• Universal bus transceiver with D-type latches and

D-type flip-flops capable of operating in transparent,

latched or clocked mode

• CMOS low power consumption

• Direct interface with TTL levels

• All inputs have bus-hold circuitry

• Output drive capability 50 Ω transmission lines at 85 °C

• Plastic fine-pitch ball grid array package.

DESCRIPTION

The 74ALVCH32501 is a high-performance CMOS

product designed for VCC operation at 2.5 and 3.3 V with

I/O compatibility up to 5 V.

Active bus-hold circuitry is provided to hold unused or

floating data inputs at a valid logic level.

The 74ALVCH32501 can be used as two 18-bit

transceivers or one 36-bit transceiver featuring

non-inverting 3-state bus compatibleoutputs in both send

and receive directions. Data flow in each direction is

controlledbyoutputenable(OEABandOEBA),latchenable

(LEAB and LEBA), and clock inputs (CPAB and CPBA).

For A-to-B data flow, the device operates in the

transparentmode when LEABisHIGH. When input LEABis

LOW, the A data is latched if input CPABis held at a HIGH

or LOW level. If input LEABis LOW, the A data is stored in

the latch/flip-flop on the LOW-to-HIGH transition of CPAB.

When input OEAB is HIGH, the outputs are active. When

input OEABis LOW, the outputs are in the high-impedance

state.

Data flow for B-to-A is similar to that of A-to-B, but uses

inputs OEBA, LEBA and CPBA. The output enables are

complimentary (OEAB is active HIGH, and OEBA is active

LOW).

To ensure the high-impedance state during power-up or

power-down, pin OEBA should be tied to VCC through a

pull-up resistor and pin OEAB should be tied to GND

through a pull-down resistor. The minimum value of the

resistor is determined by the current-sinking or

current-sourcing capability of the driver.

74ALVCH32501

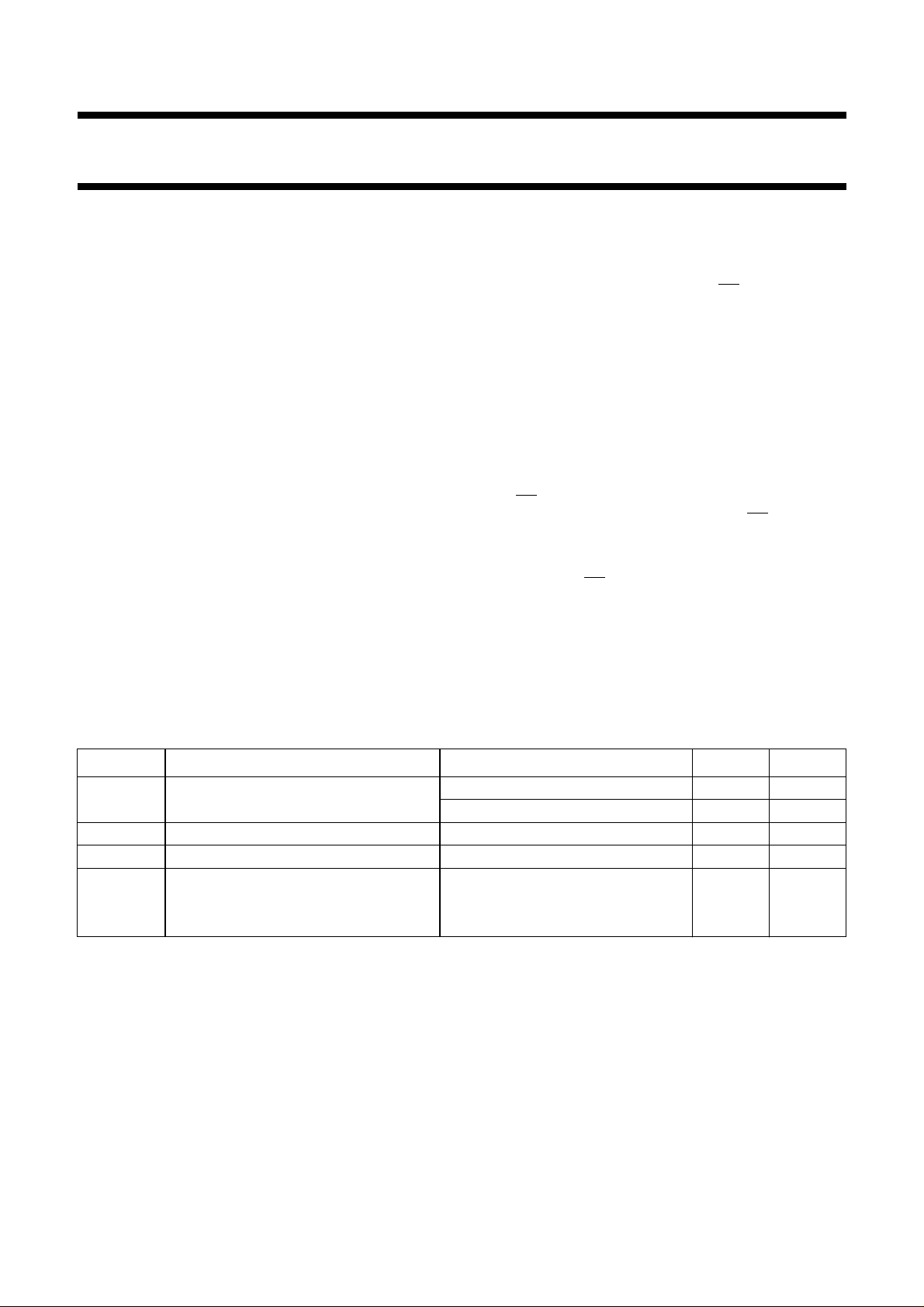

QUICK REFERENCE DATA

GND = 0 V; T

=25°C; tr=tf≤2.5 ns.

amb

SYMBOL PARAMETER CONDITIONS TYP. UNIT

t

PHL/tPLH

C

I

C

I/O

C

PD

propagation delay Anto Bn;Bnto A

n

CL= 30 pF; VCC= 2.5 V 2.8 ns

= 50 pF; VCC= 3.3 V 3.0 ns

C

L

input capacitance 4.0 pF

input/output capacitance 8.0 pF

power dissipation capacitance per latch VI= GND to VCC; note 1

outputs enabled 21 pF

outputs disabled 3 pF

Note

1. C

is used to determine the dynamic power dissipation (PDin µW).

PD

P

D=CPD

× V

2

× fi+ Σ(CL× V

CC

2

× fo) where:

CC

fi= input frequency in MHz;

fo= output frequency in MHz;

CL= output load capacitance in pF;

VCC= supply voltage in Volts;

Σ(CL× V

2

× fo) = sum of the outputs.

CC

2000 Mar 16 2

Philips Semiconductors Product specification

36-bit universal bus transceiver with direction pin;

74ALVCH32501

5 V tolerant; 3-state

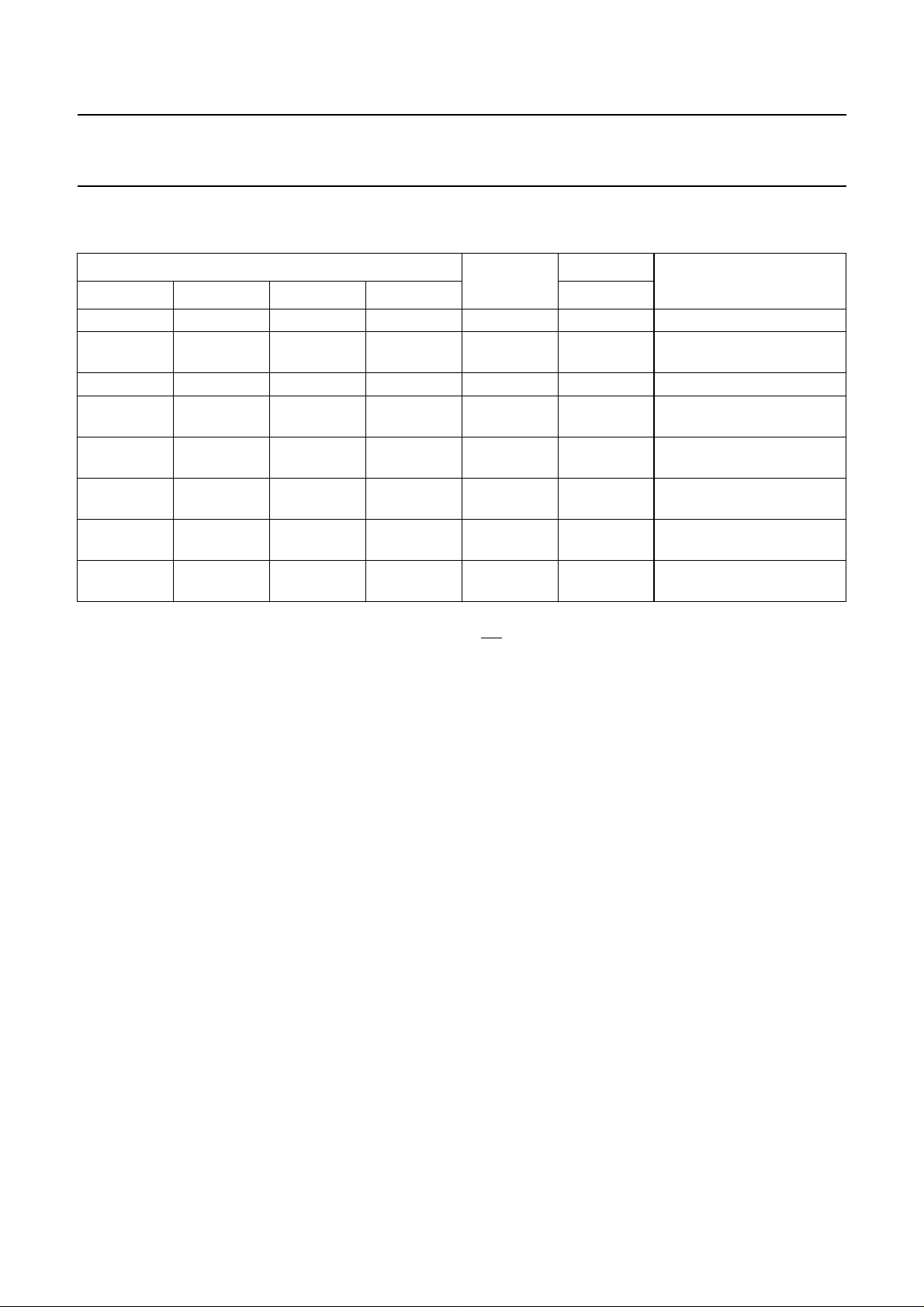

FUNCTION TABLE

See notes 1 and 2.

INPUT

nOE

AB

L H X X X Z disabled

L

L

L L H or L X NC Z disabled; hold data

L

L

H

H

H

H

H

H

H

H

nLE

AB

↓

↓

L

L

H

H

↓

↓

L

L

L

L

nCP

X

X

↑

↑

X

X

X

X

↑

↑

HorL

HorL

AB

nA

n

h

l

h

l

H

L

h

l

h

l

X

X

INTERNAL

REGISTERS

H

L

H

L

H

L

H

L

H

L

H

L

OUTPUT

nB

n

Z

Z

Z

Z

H

L

H

L

H

L

H

L

disabled; latch data

disabled; clock data

transparent

latch data and display

clock data and display

hold data and display

OPERATING MODE

Notes

1. A-to-B data flow is shown; B-to-A flow is similar but uses n

2. H = HIGH voltage level;

h = HIGH voltage level on set-up time prior to the enable or clock transition;

L = LOW voltage level;

l = LOW voltage level on set-up time prior to the enable or clock transition;

NC = no change;

X = don’t care;

↑ = LOW-to-HIGH enable or clock transition;

↓ = HIGH-to-LOW enable or clock transition;

Z = high impedance OFF-state.

OEBA, nLEBA and nCPBA.

2000 Mar 16 3

Philips Semiconductors Product specification

36-bit universal bus transceiver with direction pin;

74ALVCH32501

5 V tolerant; 3-state

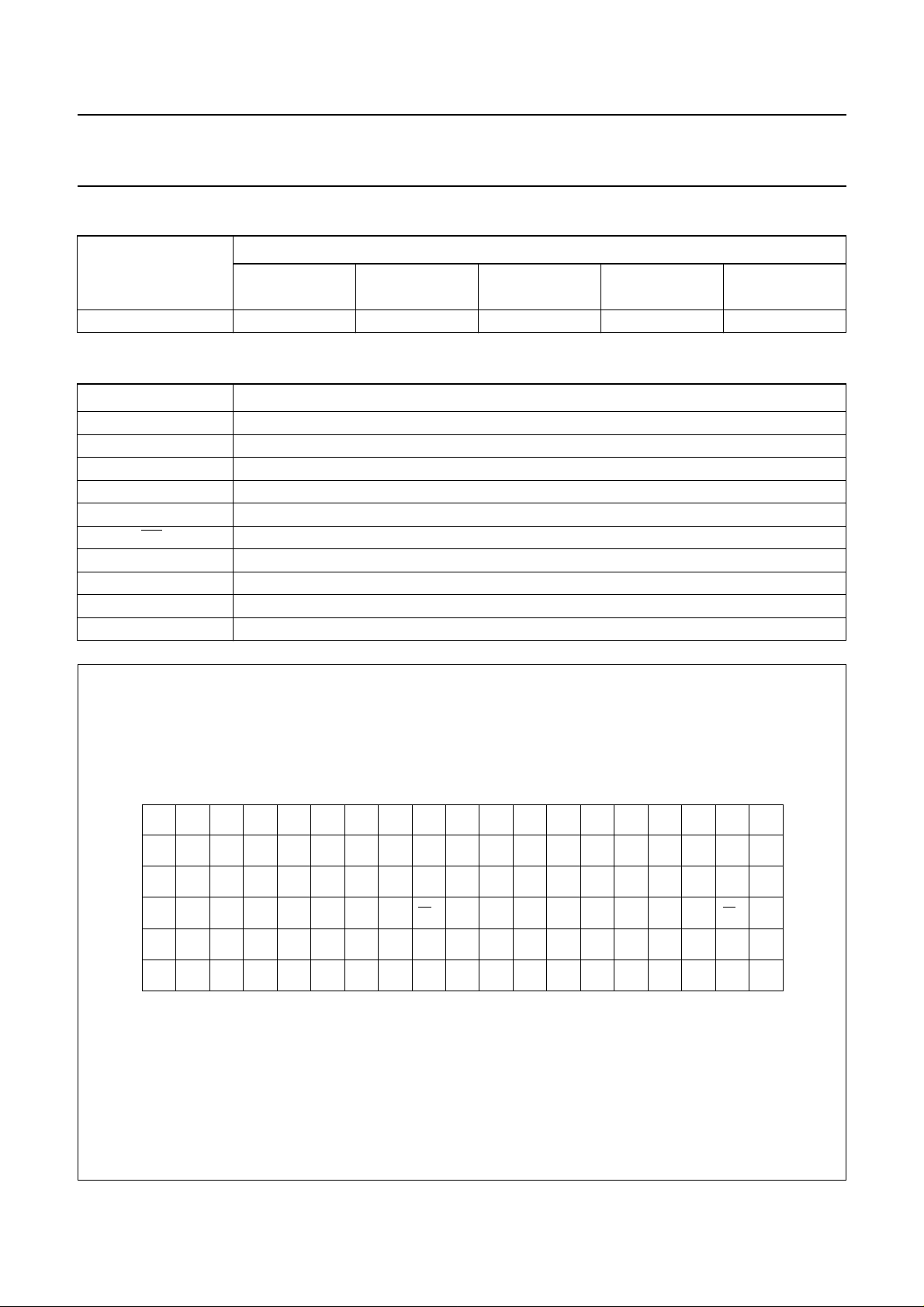

ORDERING INFORMATION

PACKAGE

TYPE NUMBER

74ALVCH32501EC −40 to +85 °C 114 LFBGA114 plastic SOT537-1

PINNING

SYMBOL DESCRIPTION

nA

n

nB

n

GND ground (0 V)

V

CC

nOE

AB

OE

n

BA

nLE

AB

nLE

BA

nCP

AB

nCP

BA

TEMPERATURE

RANGE

PINS PACKAGE MATERIAL CODE

data inputs

data outputs

DC supply voltage

output enable inputs A to B (active HIGH)

output enable inputs B to A (active LOW)

latch enable inputs A to B

latch enable inputs B to A

clock input A to B

clock input B to A

handbook, full pagewidth

1B11B31B51B71B91B111B131B141B16n.c. 2B12B32B52B72B

6

1B01B21B41B61B81B101B121B151B172CPAB2B02B22B42B62B

5

1CP

4

AB

1LE

3

AB

1A01A21A41A61A81A101A121A151A172LEAB2A02A22A42A62A

2

1A11A31A51A71A91A111A131A141A16n.c. 2A12A32A52A72A

1

AHJBDEG TUVWCF KMNRLP

GND GND GND GNDV

GND GND GND GND GNDV

1OE

AB

GND GND GND GNDV

CC

CC

V

CC

V

CC

1CP

1OE

BA

1LE

BA

Fig.1 Pin configuration.

2000 Mar 16 4

2B

2B

9

11

2B

8

10

GND

CC

BA

GND GND

AB

GND

V

CC

V

CC

V

CC

2A

8

10

2A

9

11

2B14

2B

13

2B

2B

2B

15

12

2CP

GND GND

GND2OE

2A

2A

BA

2LE

2OE

BA

2A

2A

15

12

2A

2A

14

13

MNA562

16

17

BA

17

16

Philips Semiconductors Product specification

36-bit universal bus transceiver with direction pin;

5 V tolerant; 3-state

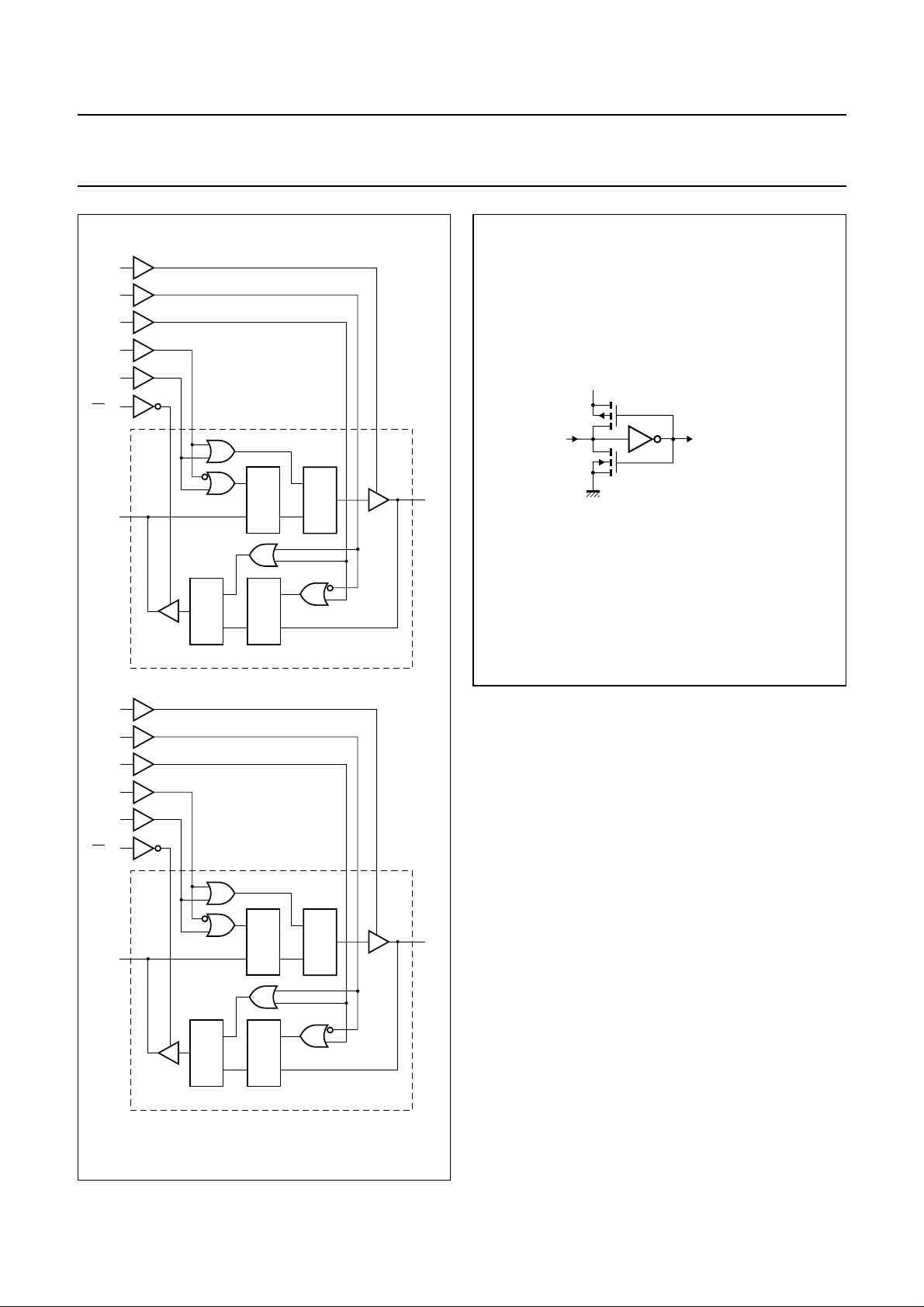

1OE

AB

1CP

BA

1LE

BA

1CP

AB

1LE

1OE

AB

BA

C1

1A

0

1D

C1

1B

1D

0

handbook, halfpage

data

input

74ALVCH32501

V

CC

to internal circuit

MNA473

2OE

2CP

2LE

2CP

2LE

2OE

18 IDENTICAL CHANNELS

AB

BA

BA

AB

AB

BA

2A

0

C1

1D

C1

1D

Fig.3 Bus-hold circuit.

C1

1D

C1

C1

1D

C1

2B

0

1D

18 IDENTICAL CHANNELS

1D

MNA563

Fig.2 Logic symbol.

2000 Mar 16 5

Loading...

Loading...