Philips 74ALVCH16952DGG Datasheet

INTEGRATED CIRCUITS

74ALVCH16952

16-bit registered transceiver (3-State)

Preliminary specification

Supersedes data of 1994 Jul

IC24 Data Handbook

1998 Sep 01

Philips Semiconductors Preliminary specification

V

C

F

74AL VCH1695216-bit registered transceiver (3-State)

FEATURES

•Complies with JEDEC standard no. 8-1A

•CMOS low power consumption

•MULTIBYTE

TM

flow-through pin-out architecture

•Low inductance, multiple center power and ground pins for

minimum noise and ground bounce

•Direct interface with TTL levels

•Output drive capability 50Ω transmission lines @ 85°C

QUICK REFERENCE DATA

GND = 0V; T

SYMBOL

t

PHL/tPLH

f

MAX

C

I

C

PD

NOTES:

is used to determine the dynamic power dissipation (PD in µW):

1. C

PD

= CPD × V

P

D

f

= input frequency in MHz; CL = output load capacity in pF;

i

= output frequency in MHz; VCC = supply voltage in V;

f

o

(C

= 25°C; tr = tf = 2.5ns

amb

Propagation delay

CPnn, to An, Bn

Maximum clock frequency

Input capacitance 3.0 pF

Power dissipation capacitance per buffer VI = GND to V

CC

2

× V

L

× fo) = sum of outputs.

CC

2

× fi + (CL × V

PARAMETER CONDITIONS TYPICAL UNIT

2

× fo) where:

CC

DESCRIPTION

The 74ALVCH16952 consists of two sections, each containing a

dual octal non-inverting registered transceiver. T wo 8-bit back to

back registers store data flowing in both directions between two

bi-directional busses. Data applied to the inputs is entered and

stored on the rising edge of the clock (CP

provided that the clock enable (CE

present at the 3-State output buffers, but is only accessible when the

output enable input (OE

outputs is the same as for B inputs to A outputs.

VCC = 3.3V, CL = 50pF

= 2.5V,

CC

= 30p

L

1

CC

p

, where X is AB or BA)

XX

) is LOW. The data is then

XX

) is LOW. Data flow from A inputs to B

XX

3.2 ns

350 MHz

30 pF

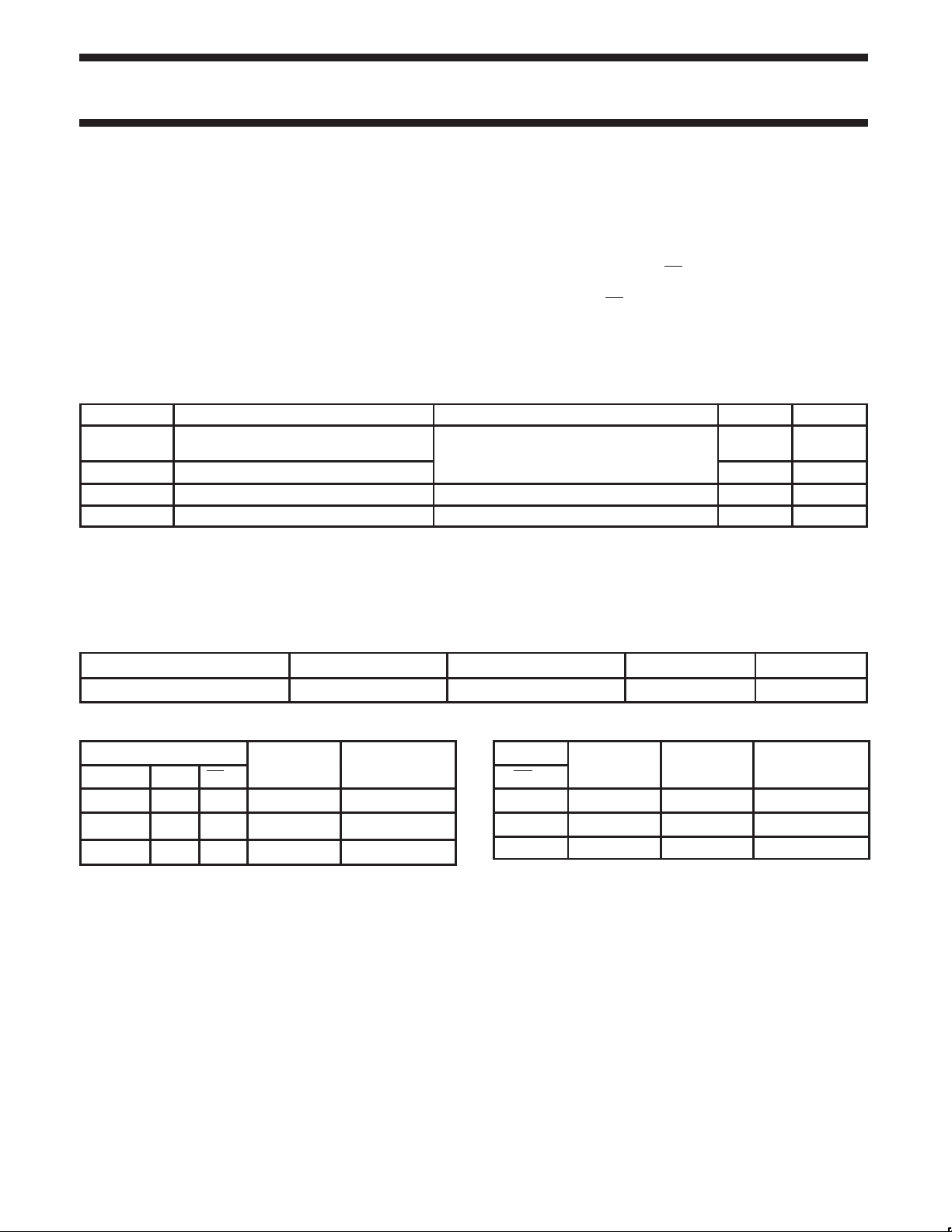

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

56-Pin Plastic TSSOP Type II –40°C to +85°C 74ALVCH16952 DGG ACH16952 DGG SOT364-1

FUNCTION TABLE for register An or Bn

INPUTS

An or Bn CP

X X H NC Hold data

L

H

H = HIGH voltage level

L = LOW voltage level

↑ = LOW-to-HIGH transition

CE

XX

INTERNAL OPERATING

XX

L L Load data

L H Load data

Q MODE

FUNCTION TABLE for output enable

INPUTS

OE

nn

H X Z Disable outputs

L L L Enable outputs

L H H Enable outputs

NC = no change

X = don’t care

Z = high impedance OFF-state

INTERNAL An or Bn OPERATING

Q OUTPUTS MODE

1998 Sep 01

2

Philips Semiconductors Preliminary specification

74AL VCH1695216-bit registered transceiver (3-State)

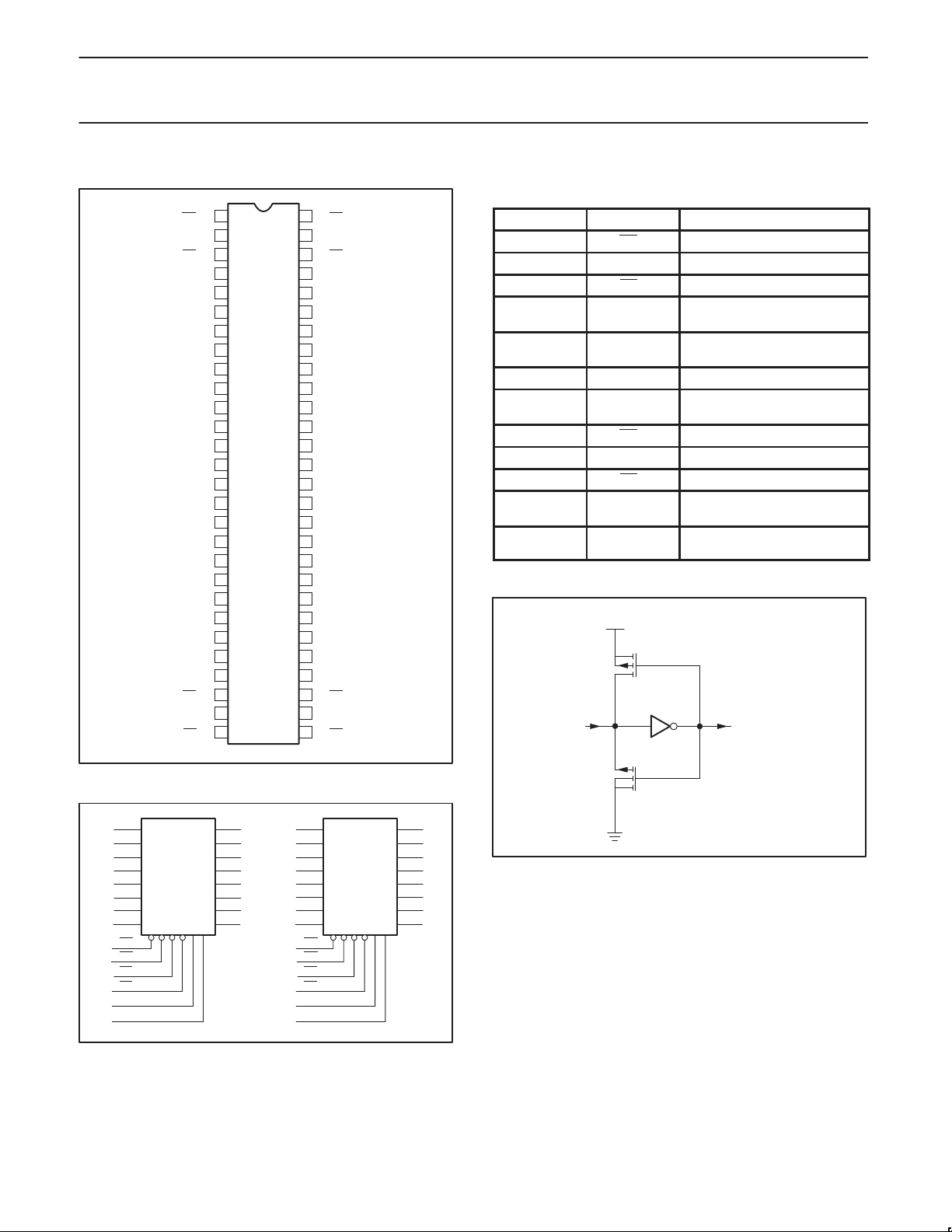

PIN CONFIGURATION

PIN DESCRIPTION

1OE

1CP

1CE

2CE

2CP

2OE

GND

1A0

1A1

V

CC

1A2

1A3

1A4

GND

1A5

1A6

1A7

2A0

2A1

2A2

GND

2A3

2A4

2A5

V

CC

2A6

2A7

GND

1

AB

2

AB

3

AB

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

AB

27

AB

28

AB

56

1OE

BA

55

1CP

BA

1CE

54

BA

GND

53

1B0

52

51

1B1

50

V

CC

49

1B2

1B3

48

1B4

47

GND

46

1B5

45

1B6

44

1B7

43

2B0

42

41

2B1

2B2

40

GND

39

2B3

38

37

2B4

36

2B5

35

V

CC

34

2B6

33

2B7

GND

32

31

2CE

BA

30

2CP

BA

29

2OE

BA

SY00026

PIN NUMBER SYMBOL NAME AND FUNCTION

1, 28 nOE

2, 27 nCP

3, 26 nCE

5, 6, 8, 9, 10,

12, 13, 14

1A0 to 1A7 Data inputs/outputs

4, 11, 18, 25,

32, 39, 46, 53

7, 22, 35, 50 V

15, 16, 17, 19,

20, 21, 23, 24

2B0 to 2B7 Data inputs/outputs

29, 56 nOE

30, 55 nCP

31, 54 nCE

42, 41, 40, 38,

37, 36, 34, 33

52, 51, 49, 48,

47, 45, 44, 43

2B0 to 2B7 Data inputs/outputs

1B0 to 1B7 Data inputs/outputs

AB

AB

AB

GND Ground (0V)

CC

BA

BA

BA

Output enable A-to-B

Clock input A-to-B

A-to-B enable

Positive supply voltage

Output enable B-to-A

Clock input B-to-A

B-to-A enable

BUSHOLD CIRCUIT

V

CC

Data Input

To internal circuit

LOGIC SYMBOL

1A0

5

1A1

6

1A2

8

1A3

9

1A4

10

1A5

12

1A6

13

1A7

14

1OE

56

BA

1OE

1

AB

1CE

3

AB

1CE

54

BA

1CP

2

AB

1CP

55

BA

1998 Sep 01

1B0

1B1

1B2

1B3

1B4

1B5

1B6

1B7

15

52

51

49

48

47

45

44

43

2A0

16

2A1

17

2A2

19

2A3

20

2A4

21

2A5

23

2A6

24

2A7

2OE

29

BA

2OE

28

AB

2CE

26

AB

2CE

31

BA

2CP

27

AB

2CP

30

BA

2B0

42

2B1

41

2B2

40

2B3

38

2B4

37

2B5

36

2B6

34

2B7

33

SY00029

SW00050

3

Philips Semiconductors Preliminary specification

74AL VCH1695216-bit registered transceiver (3-State)

LOGIC SYMBOL (one section)

CE

AB

CP

AB

OE

AB

CE

BA

CP

BA

OE

BA

CP

Q

TO 7 OTHER CHANNELS

Q

D

CP

B0

SY00027

A0

D

8 IDENTICAL CHANNELS

1998 Sep 01

4

Loading...

Loading...