Philips 74alvch16652 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

74ALVCH16652

16-bit transceiver/register with dual

enable; 3-state

Product specification

Supersedes data of 1998 Aug 31

File under Integrated Circuits, IC24

1999 Nov 23

Philips Semiconductors Product specification

16-bit transceiver/register with dual enable; 3-state 74ALVCH16652

FEATURES

• In accordance with JEDEC standard no. 8-1A

• CMOS low power consumption

• MULTIBYTE flow-through pin-out architecture

• Low inductance, multiple supply and ground pins for

minimum noise and ground bounce

• Direct interface with TTL levels

• All data inputs have bus hold

• Output drive capability 50 Ω transmission lines at 85 °C

• Current drive ±24 mA at 3.0 V.

DESCRIPTION

The 74ALVCH16652 consists of 16 non-inverting bus

transceiver circuits with 3-state outputs, D-type flip-flops

and controlcircuitry arranged for multiplexed transmission

of data directly from the data bus or from the internal

storage registers.

Data on the ‘A’ or ‘B’, or both buses, will be stored in the

internal registers, at the appropriate clock inputs

(nCPABor nCPBA) regardless of the select inputs (nS

AB

and nSBA) or output enable (nOEAB and nOEBA) control

inputs.

Depending on the select inputs nSAB and nSBA data can

directly go from input to output (real-time mode) or data

can be controlled by the clock (storage mode), when OE

inputs permit this operating mode.

Theoutput enableinputsnOEABandnOEBAdeterminethe

operation mode of the transceiver. When nOEAB is LOW,

nodata transmissionfrom nBntonAnispossible andwhen

nOEBA is HIGH, no data transmission from nBnto nAn is

possible.

When nSABand nSBAare inthe real-time transfer mode, it

is also possible to store data without using the internal

D-type flip-flops by simultaneously enabling nOEAB and

nOEBA. In this configuration each output reinforces its

input.

Active bus hold circuitry is provided to hold unused or

floating data inputs at a valid logic level.

QUICK REFERENCE DATA

Ground = 0; T

=25°C; tr=tf= 2.5 ns.

amb

SYMBOL PARAMETER CONDITIONS TYPICAL UNIT

t

PHL/tPLH

f

max

C

I

C

PD

propagation delay nAn,nBnto nBn,nA

n

maximum clock frequency 350 MHz

input capacitance 4.0 pF

power dissipation capacitance per latch notes 1 and 2

CL= 50 pF; VCC= 3.3 V 2.6 ns

outputs enabled 22 pF

outputs disabled 4.0 pF

Notes

1. C

is used to determine the dynamic power dissipation (PDin µW).

PD

PD=CPD× V

2

× fi+ Σ (CL× V

CC

2

× fo) where:

CC

fi= input frequency in MHz;

CL= output load capacitance in pF;

fo= output frequency in MHz;

VCC= supply voltage in Volts;

Σ (CL× V

2

× fo) = sum of outputs.

CC

2. The condition is VI= GND to VCC.

1999 Nov 23 2

Philips Semiconductors Product specification

16-bit transceiver/register with dual enable; 3-state 74ALVCH16652

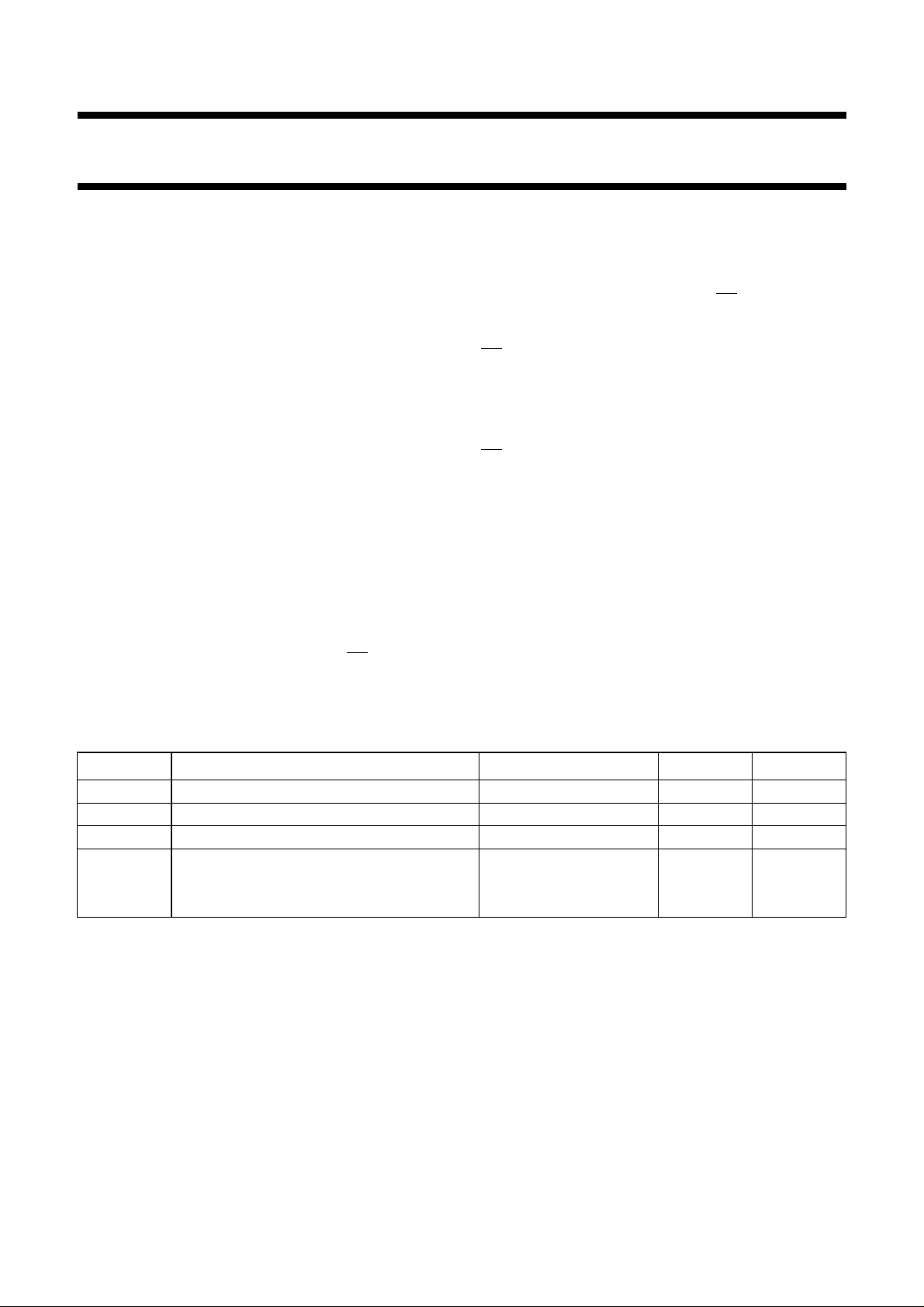

FUNCTION TABLE

See note 1.

INPUTS DATA I/O

FUNCTION

nOE

L

L

X

H

L

L

L

L

H

H

AB

nOE

H

H

H

H

X

L

L

L

H

H

nCP

BA

AB

HorL↑HorL↑X

↑

HorL↑X

↑

HorL↑↑

↑

X

X

X

HorLXX

X

HorLXX

nCP

BA

X

L

X

X

L

H

nS

AB

X

X

X

X

X

L

L

H

X

X

nS

nA0to nA

BA

input input

input

input

unspecified

output

output input

input output

nB0to nB

7

unspecified

output

(2)

input

input

7

isolation store A and B data

(2)

store A, hold B

store A in both registers

hold A, store B

store B in both registers

real-time B data to A bus

stored B data to A bus

real-time A data to B bus

stored A data to B bus

H L H or L Hor L H H output output stored A data to B bus and

stored B data to A bus

Notes

1. H = HIGH voltage level;

L = LOW voltage level;

X = don’t care;

↑ = LOW-to-HIGH.

2. The data output functions may beenabled ordisabled byvarious signals at the nOE

and nOEBAinputs. Data input

AB

functions are always enabled, i.e., data atthe businputs willbe storedon everyLOW-to-HIGH transitionon theclock

inputs.

1999 Nov 23 3

Philips Semiconductors Product specification

16-bit transceiver/register with dual enable; 3-state 74ALVCH16652

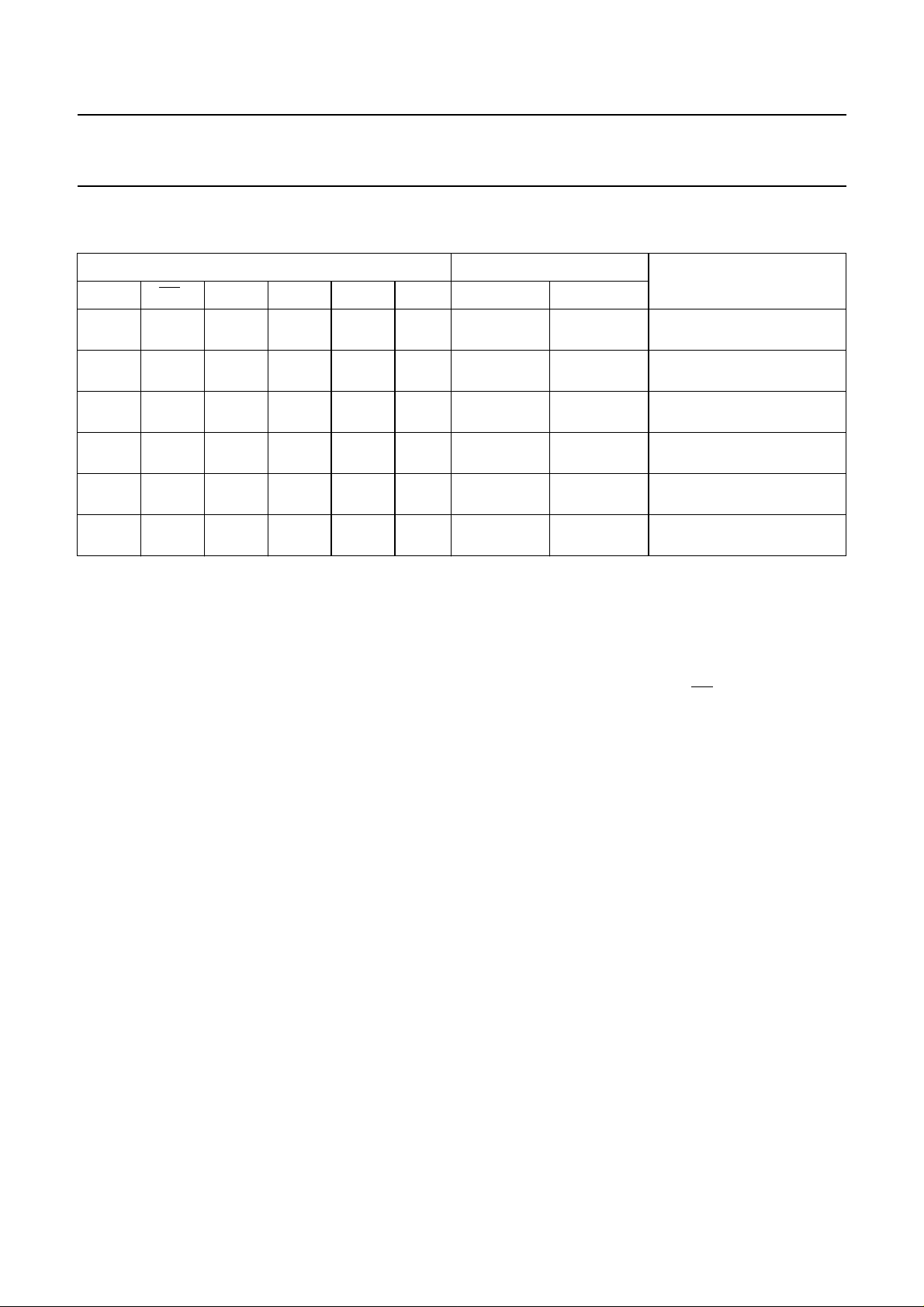

ORDERING INFORMATION

OUTSIDE NORTH

AMERICA

NORTH

AMERICA

TEMPERATURE

RANGE

PINS PACKAGE MATERIAL CODE

74ALVCH16652DGG ACH16652 DGG −40 to +85 °C 56 TSSOP plastic SOT364-1

PINNING

PIN SYMBOL DESCRIPTION

PACKAGE

1 and 28 1OE

2 and 27 1CP

3 and 26 1S

5, 6, 8, 9, 10, 12, 13 and 14 1A

AB

AB

AB

to 1A

0

, 2OE

, 2CP

, 2S

AB

AB

AB

output enable A-to-B

clock input A-to-B

select input A-to-B

7

‘1A’ data inputs/outputs

4, 11, 18, 25, 32, 39, 46 and 53 GND ground (0 V)

7, 22, 35, 50 V

CC

15, 16, 17, 19, 20, 21, 23 and 24 2A

29 and 56 2

OEBA, 1OE

30 and 55 2CP

31 and 54 2S

33, 34, 36, 37, 38, 40, 41 and 42 2B

43, 44, 45, 47, 48, 49, 51 and 52 1B

to 2A

0

BA

BA

to 2B

0

to 1B

7

, 1CP

, 1S

7

BA

BA

BA

7

0

positive supply voltage

‘2A’ data inputs/outputs

output enable B-to-A

clock input B-to-A

select input B-to-A

‘2B’ data inputs/outputs

‘1B’ data inputs/outputs

1999 Nov 23 4

Philips Semiconductors Product specification

16-bit transceiver/register with dual enable; 3-state 74ALVCH16652

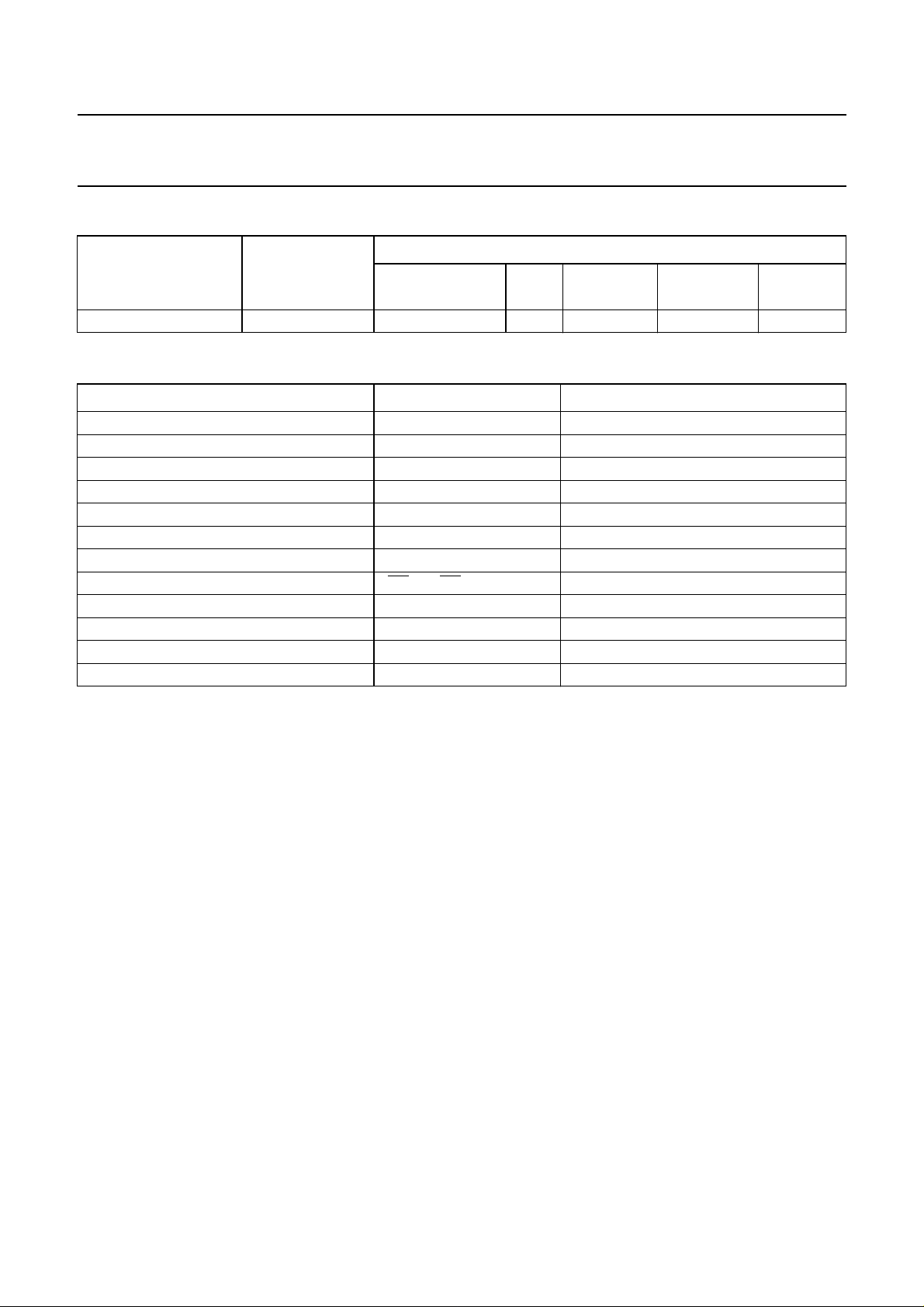

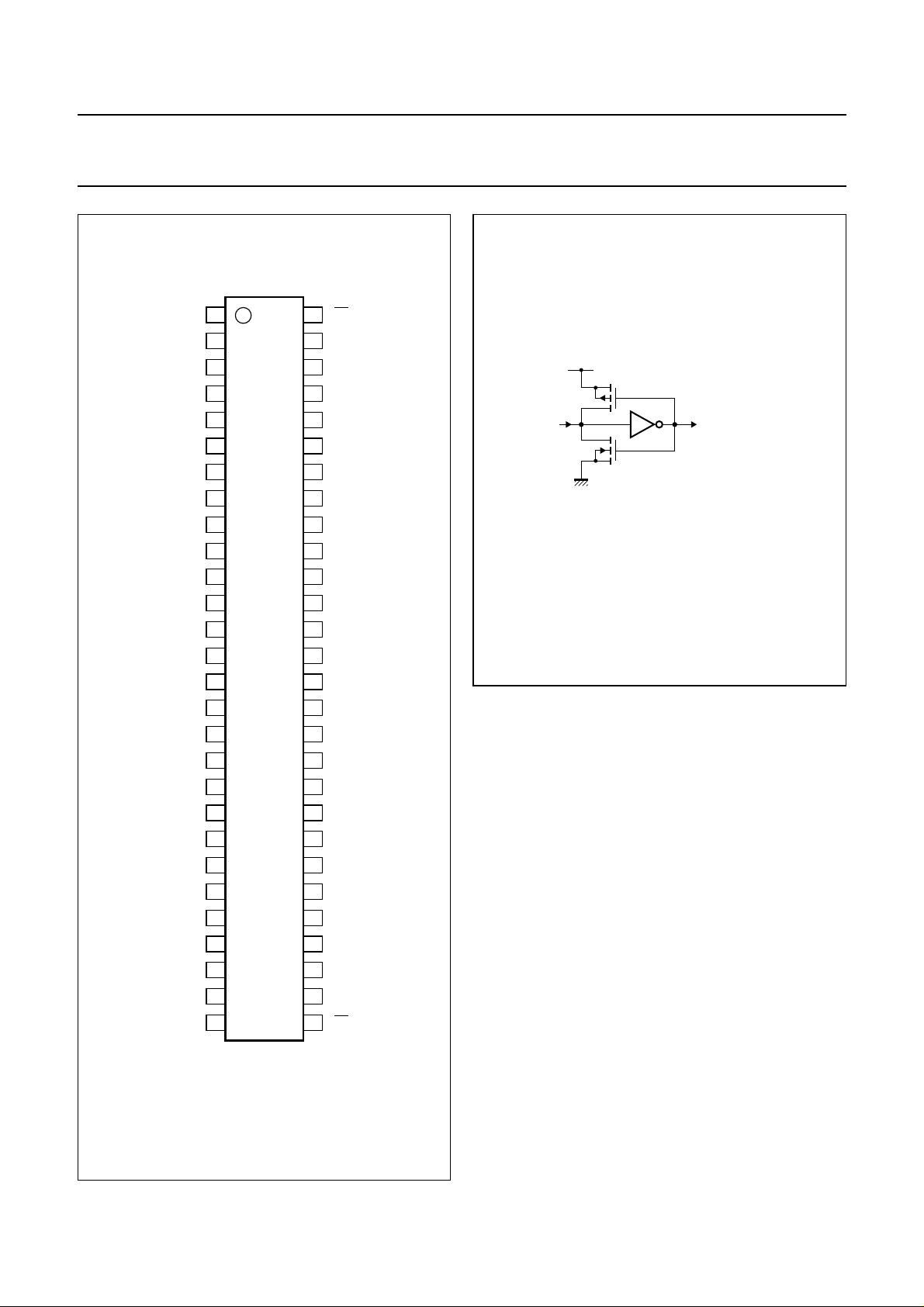

handbook, halfpage

1OE

1CP

1S

2S

2CP

2OE

AB

AB

AB

GND

1A

1A

V

CC

1A

1A

1A

GND

1A

1A

1A

2A

2A

2A

GND

2A

2A

2A

V

CC

2A

2A

GND

AB

AB

AB

1OE

MNA315

56

BA

1CP

55

BA

1S

54

BA

GND

53

1B

52

0

1B

51

1

V

50

CC

1B

49

2

1B

48

3

1B

47

4

GND

46

1B

45

5

1B

44

6

1B

43

7

2B

42

0

2B

41

1

2B

40

2

GND

39

2B

38

3

2B

37

4

2B

36

5

V

35

CC

2B

34

6

2B

33

7

GND

32

2S

31

BA

2CP

30

BA

2OE

29

BA

handbook, halfpage

data

input

V

CC

MNA318

Fig.2 Bus hold circuit.

to internal circuit

1

2

3

4

5

0

6

1

7

8

2

9

3

10

4

11

12

5

13

6

14

7

0

1

2

3

4

5

6

7

16652

15

16

17

18

19

20

21

22

23

24

25

26

27

28

Fig.1 Pin configuration.

1999 Nov 23 5

Philips Semiconductors Product specification

16-bit transceiver/register with dual enable; 3-state 74ALVCH16652

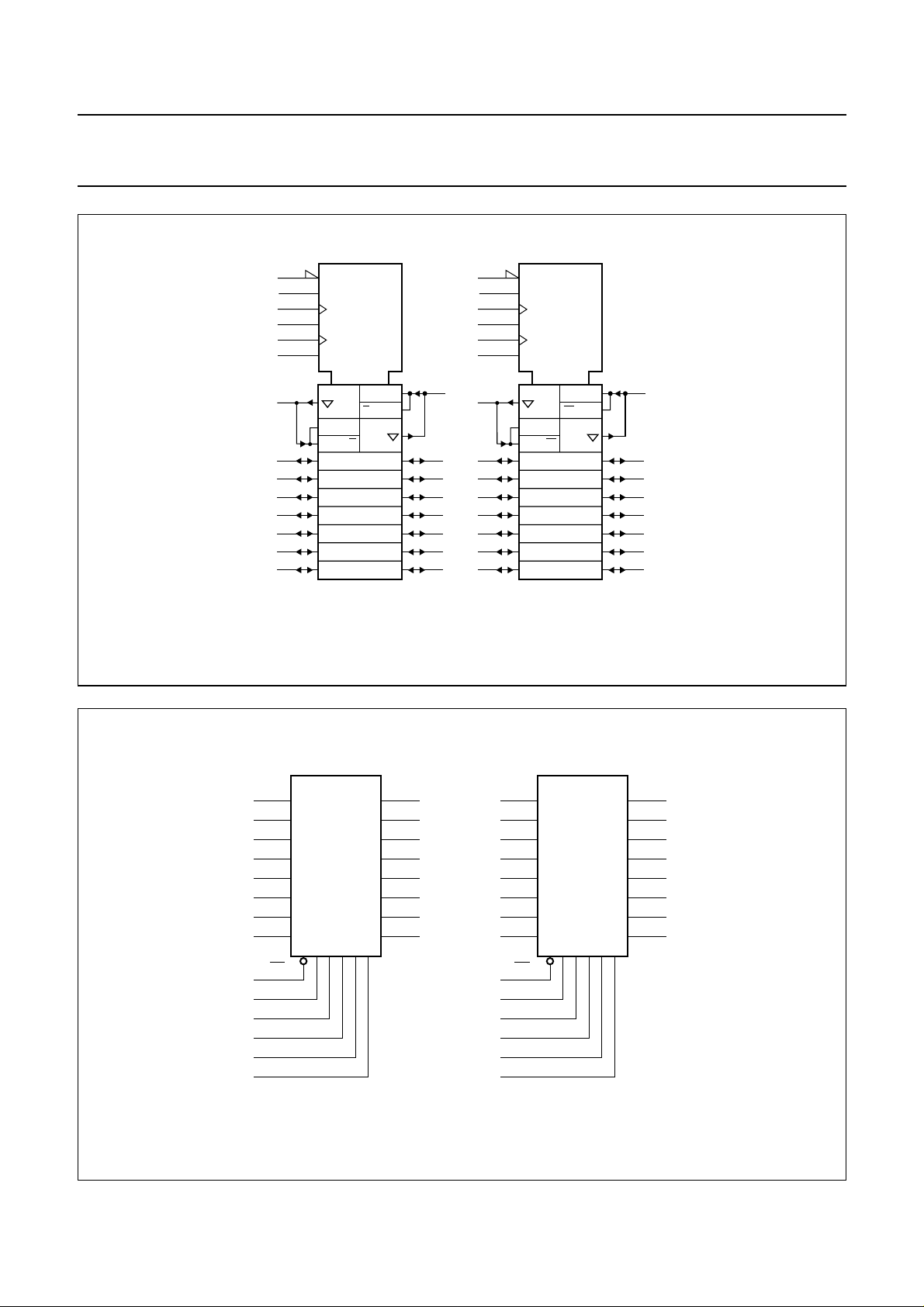

handbook, full pagewidth

56

1

55

54

2

3

5

651

8

9

10

12

13

14

EN1[BA

EN2[AB

C3

G4

C5

G6

≥1

1

5D

6

1

6

]

]

3D

4

1

4

≥1 ≥1

2

52

49

48

47

45

44

43

29

28

30

31

27

26

15

16 41

17

19

20

21

23

24

EN7[BA

EN8[AB

C9

G10

C11

G12

≥1

7

11D

12

1

12

]

]

10

10

MNA317

Fig.3 IEC logic symbol.

42

9D

1

8

40

38

37

36

34

33

handbook, full pagewidth

1A

0

5

1A

1

6

1A

2

8

1A

3

9

1A

4

10

1A

5

12

1A

6

13

1A

7

14

1OE

56

54

55

BA

1OE

AB

1

1S

AB

3

1S

BA

1CP

AB

2

1CP

BA

1B

1B

1B

1B

1B

1B

1B

1B

0

52

1

51

2

49

3

48

4

47

5

45

6

44

7

43

Fig.4 Logic symbol.

1999 Nov 23 6

2A

0

15

2A

1

16

2A

2

17

2A

3

19

2A

4

20

2A

5

21

2A

6

23

2A

7

24

2OE

BA

29

2OE

AB

28

2S

AB

26

2S

BA

31

2CP

AB

27

2CP

BA

30

2B

2B

2B

2B

2B

2B

2B

2B

MNA316

0

42

1

41

2

40

3

38

4

37

5

36

6

34

7

33

Loading...

Loading...