Philips 74ALVCH16646DGG Datasheet

INTEGRATED CIRCUITS

74ALVCH16646

16-bit bus transceiver/register (3-State)

Product specification 1998 Sep 03

IC24 Data Handbook

Philips Semiconductors Product specification

CPDPower dissipation capacitance per channel

V

GND to V

1

pF

74AL VCH1664616-bit bus transceiver/register (3-State)

FEA TURES

•Complies with JEDEC standard no. 8-1A

•CMOS low power consumption

•MULTIBYTE

•Low inductance, multiple V

and ground bounce

TM

flow-through pin-out architecture

and ground pins for minimum noise

CC

•Direct interface with TTL levels

•Current drive ± 24 mA at 3.0 V

•Output drive capability 50Ω transmission lines @ 85°C

•All inputs have bushold circuitry

DESCRIPTION

The 74ALVCH16646 consists of 16 non-inverting bus transceiver

circuits with 3-State outputs, D-type flip-flops and control circuitry

arranged for multiplexed transmission of data directly from the

internal registers. Data on the ‘A’ or ‘B’ bus will be clocked in the

internal registers, as the appropriate clock (CP

HIGH logic level. Output enable (OE

) and direction (DIR) inputs are

provided to control the transceiver function. In the transceiver mode,

data present at the high-impedance port may be stored in either the

‘A’ or ‘B’ register, or in both. The select source inputs (S

can multiplex stored and real-time (transparent mode) data. The

direction (DIR) input determines which bus will receive data when

OE

is active (LOW). In the isolation mode (OE = HIGH), ‘A’ data

may be stored in the ‘B’ register and/or ‘B’ data may be stored in the

‘A’ register.

When an output function is disabled, the input function is still

enabled and may be used to store and transmit data. Only one of

the two buses, ‘A’ or ‘B’ may be driven at a time.

To ensure the high impedance state during power up or power

down, OE should be tied to VCC through a pullup resistor; the

or CPBA) goes to a

AB

and SBA)

AB

minimum value of the resistor is determined by the

current-sinking/current-sourcing capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data

inputs at a valid logic level.

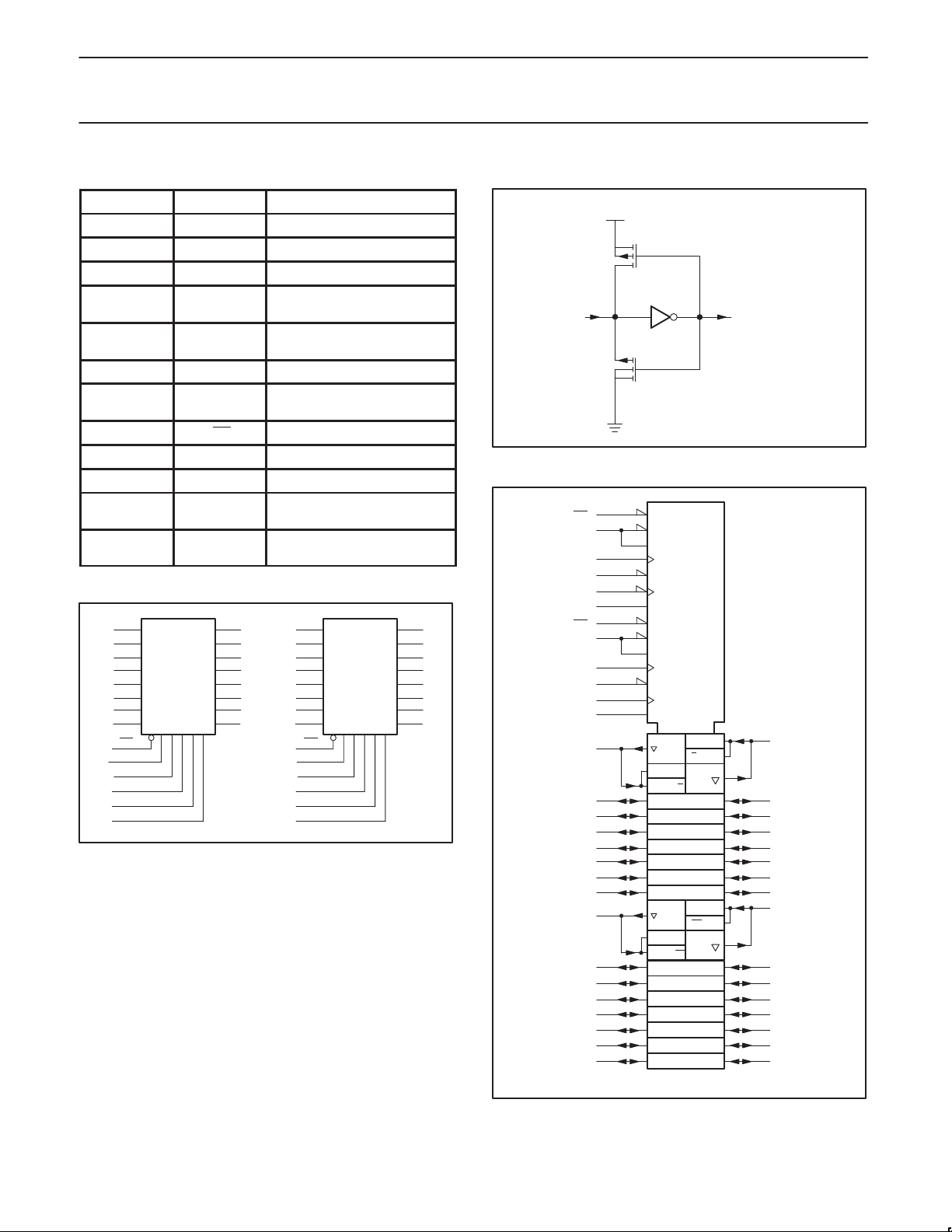

PIN CONFIGURATION

1OE

1

1DIR

2

1CP

AB

3

1S

AB

4

GND

5

1A0

6

1A1

7

V

CC

8

1A2

9

1A3

10

1A4

11

GND

12

1A5

13

1A6

14

1A7

15

2A0

16

2A1

17

2A2

18

GND

19

2A3

20

2A4

21

2A5

22

V

CC

23

2A6

24

2A7 2B7

25

GND

26

2S

AB

27

2CP

AB

28

2DIR

56

55

1CP

54

1S

53

GND

52

1B0

51

1B1

50

V

49

1B2

48

1B3

47

1B4

46

GND

45

1B5

44

1B6

43

1B7

42

2B0

41

2B1

40

2B2

39

GND

38

2B3

37

2B4

36

2B5

35

V

34

2B6

33

32

GND

31

2S

30

2CP

29

2OE

SY00011

BA

BA

CC

CC

BA

BA

QUICK REFERENCE DA TA

GND = 0V; T

SYMBOL

t

PHL/tPLH

C

I

F

max

NOTES:

is used to determine the dynamic power dissipation (PD in µW):

1. C

PD

= CPD × V

P

D

f

= input frequency in MHz; CL = output load capacity in pF;

i

= output frequency in MHz; VCC = supply voltage in V;

f

o

(C

= 25°C; tr = tf ≤ 2.5ns

amb

Propagation delay

nAx to nBx

Input capacitance 3.0 pF

Maximum clock frequency

CC

2

× V

L

× fo) = sum of outputs.

CC

2

× fi + (CL × V

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

56-Pin Plastic TSSOP Type II –40°C to +85°C 74ALVCH16646 DGG ACH16646 DGG SOT364-1

1998 Sep 03 853-21 16 19959

PARAMETER CONDITIONS TYPICAL UNIT

VCC = 2.5V, CL = 30pF

VCC = 3.3V, CL = 50pF

p

p

p

=

I

CC

Outputs enabled 36

Outputs disabled 4

VCC = 2.5V, CL = 30pF

VCC = 3.3V, CL = 50pF

2

× fo) where:

CC

2.6

2.7

300

320

2

ns

p

MHz

Philips Semiconductors Product specification

74ALVCH1664616-bit bus transceiver/register (3-State)

PIN DESCRIPTION

PIN NUMBER SYMBOL NAME AND FUNCTION

1, 28 nDIR Direction control input

2, 27 nCP

3, 26 nS

5, 6, 8, 9, 10,

12, 13, 14

1A0 to 1A7 Data inputs/outputs

4, 11, 18, 25,

32, 39, 46, 53

7, 22, 35, 50 V

15, 16, 17, 19,

20, 21, 23, 24

2A0 to 2A7 Data inputs/outputs

AB

GND Ground (0V)

CC

Clock input A-to-B

AB

Select input A-to-B

Positive supply voltage

29, 56 nOE Output enable

30, 55 nCP

31, 54 nS

42, 41, 40, 38,

37, 36, 34, 33

52, 51, 49, 48,

47, 45, 44, 43

BA

2B0 to 2B7 Data inputs/outputs

1B0 to 1B7 Data inputs/outputs

BA

Clock input B-to-A

Select input B-to-A

LOGIC SYMBOL

1A0

5

1A1

6

1A2

8

1A3

9

1A4

10

1A5

12

1A6

13

1A7

14

1OE

56

1

1DIR

2

1S

AB

54

1S

BA

2

1CP

AB

55

1CP

BA

1B0

1B1

1B2

1B3

1B4

1B5

1B6

1B7

15

52

51

49

48

47

45

44

43

2A0

16

2A1

17

2A2

19

2A3

20

2A4

21

2A5

2A6

23

2A7

24

2OE

29

2DIR

28

2S

26

AB

2S

31

BA

2CP

27

AB

2CP

30

BA

2B0

2B1

2B2

2B3

2B4

2B5

2B6

2B7

42

41

40

38

37

36

34

33

SY00013

BUSHOLD CIRCUIT

V

CC

Data Input

LOGIC SYMBOL (IEEE/IEC)

56

1OE

1

1DIR

55

1CP

BA

54

1S

BA

2

1CP

AB

3

1S

AB

29

2OE

28

2DIR

30

2CP

BA

31

2S

BA

27

2CP

AB

26

2S

AB

5

1A0

6

1A1 1B1

8

1A2

9

1A3

10

1A4

12

1A5

13

1A6

14

1A7

15

2A0

16

2A1

17

2A2

19

2A3

20

2A4

21

2A5

23

2A6

24

2A7

G3

3EN1[BA]

3EN2[AB]

C4

G5

C6

G7

G10

10EN8[BA]

10EN9[AB]

C11

G12

C13

G14

3

1

1

6D 7

17

1

8

13D 14

114

54D

1

5

3

1

2

12 11D

12

1

1

9

To internal circuit

SW00050

52

1B0

51

49

1B2

48

1B3

47

1B4

45

1B5

44

1B6

43

1B7

42

2B0

41

2B1

40

2B2

38

2B3

37

2B4

36

2B5

34

2B6

33

2B7

1998 Sep 03

SY00014

3

Philips Semiconductors Product specification

FUNCTION

74ALVCH1664616-bit bus transceiver/register (3-State)

LOGIC DIAGRAM (one section)

OE

DIR

S

BA

CP

BA

S

AB

CP

AB

V

CC

S

YD

1

An

MUX

D

QD

2

FF

n

CP

V

CC

S

YD

1

8 IDENTICAL CHANNELS

CP

MUX

D

QD

FF

n

2

Bn

SY00012

FUNCTION TABLE

INPUTS DATA I/O *

nOE nDIR nCP

X

X

H

H

L

L

L

L

X

X

X

X

L

L

H

H

↑

X

↑

H or L↑H or LXX

X

X

X

H or LXX

* The data output functions may be enabled or disabled by various signals at the OE and DIR inputs. Data input functions are always enabled,

i.e., data at the bus inputs will be stored on every LOW-to-HIGH transition on the clock inputs.

un = unspecified

H = HIGH voltage level

L = LOW voltage level

X = don’t care

↑ = LOW-to-HIGH level transition

AB

nCP

BA

X

↑

X

H or LXX

nS

X

X

L

H

AB

nS

BA

X

X

X

X

L

H

X

X

nAx nBx

input

un*

un*

input

input input

output input

input output

store A, B unspecified*

store B, A unspecified*

store A and B data, isolation

hold storage

real-time B data to A bus

stored B data to A bus

real-time A data to B bus

stored A data to B bus

1998 Sep 03

4

Loading...

Loading...