DATA SH EET

Product specification

Supersedes data of 1998 Aug 31

File under Integrated Circuits, IC24

1999 Sep 20

INTEGRATED CIRCUITS

74ALVCH16623

16-bit transceiver with dual enable;

3-state

1999 Sep 20 2

Philips Semiconductors Product specification

16-bit transceiver with dual enable; 3-state 74ALVCH16623

FEATURES

• Complies with JEDEC standard

no. 8-1A

• CMOS low power consumption

• Direct interface with TTL levels

• MULTIBYTE flow-through

standard pin-out architecture

• All data inputs have bus hold

circuitry

• Output drive capability 50 Ω

transmission lines at 85 °C

• Current drive ±24 mA at 3.0 V.

DESCRIPTION

The 74ALVCH16623 is a high-performance, low-power, low-voltage, Si-gate

CMOS device, superior to most advanced CMOS compatible TTL families.

The 74ALVCH16623 isa16-bit transceiver featuring non-inverting 3-state bus

compatible outputs in both send and receive directions.

This 16-bit bus transceiver is designed for asynchronous two-way

communication between data buses. The control function implementation

allows maximum flexibility in timing. This device allows data transmission from

the A bus to the B bus or from the B bus to the A bus, depending upon the logic

levels at the enable inputs (nOEAB,nOEBA). The enable inputs can be used to

disable the device so that the buses are effectively isolated. The dual enable

function configuration gives this transceiver the capability to store data by

simultaneous enabling ofnOEABand nOEBA. Each output reinforces its input in

this transceiver configuration. Thus, when all control inputs are enabled and all

other data sources to the four sets of the bus lines are at high-impedance

OFF-state, all sets of bus lines will remain at their last states. The 8-bit codes

appearing on the two double sets of buses will be complementary. This device

can be used as two 8-bit transceivers or one 16-bit transceiver.

To ensure the high-impedance state during power-on or power-down, OE

BA

shouldbetied to VCCthrougha pull-up resistor and OEABshouldbetied to GND

through a pull-down resistor; the minimum value of the resistor is determined

by the current-sinking/current-sourcing capability of the driver.

Active bus hold circuitry is provided to hold unused or floating data inputs at a

valid logic level.

QUICK REFERENCE DATA

Ground = 0; T

amb

=25°C; tr=tf= 2.5 ns.

Notes

1. C

PD

is used to determine the dynamic power dissipation (PDin µW).

P

D=CPD

× V

CC

2

× fi+ Σ (CL× V

CC

2

× fo) where:

fi= input frequency in MHz;

CL= output load capacitance in pF;

fo= output frequency in MHz;

VCC= supply voltage in Volts;

Σ (CL× V

CC

2

× fo) = sum of outputs.

2. The condition is VI= GND to VCC.

SYMBOL PARAMETER CONDITIONS TYPICAL UNIT

t

PHL/tPLH

propagation delay nAn,nBnto nBn,nAnCL= 30 pF; VCC= 2.5 V 2.0 ns

C

L

= 50 pF; VCC= 3.3 V 1.9 ns

C

I/O

input/output capacitance 10.0 pF

C

I

input capacitance 3.0 pF

C

PD

power dissipation capacitance per buffer notes1 and 2

outputs enabled 35 pF

outputs disabled 5 pF

1999 Sep 20 3

Philips Semiconductors Product specification

16-bit transceiver with dual enable; 3-state 74ALVCH16623

ORDERING INFORMATION

FUNCTION TABLE

See note 1.

Note

1. H = HIGH voltage level;

L = LOW voltage level;

Z = high-impedance OFF-state.

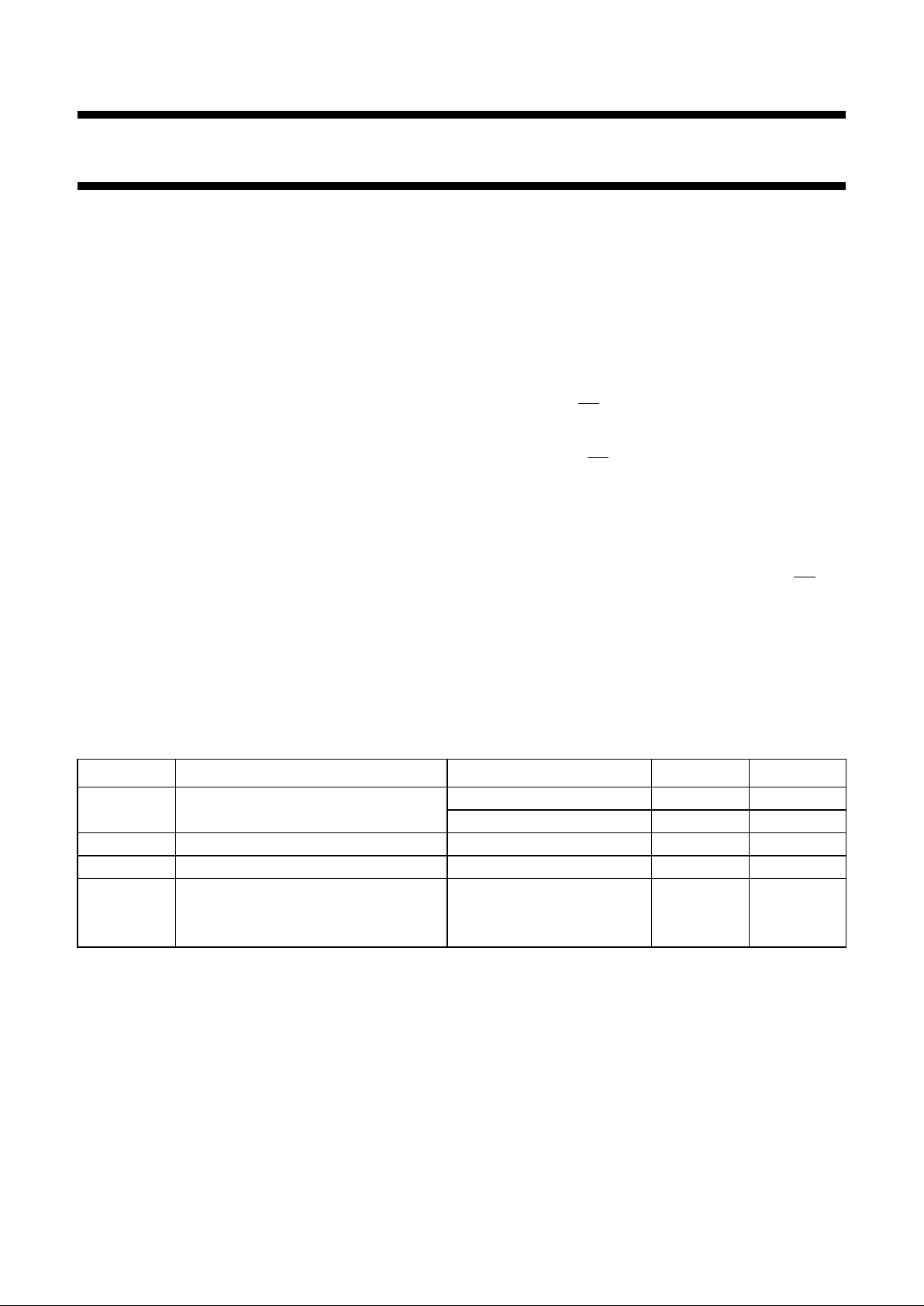

PINNING

TYPE NUMBER

PACKAGE

TEMPERATURE RANGE PINS PACKAGE MATERIAL CODE

74ALVCH16623DGG −40 to +85 °C 48 TSSOP plastic SOT362-1

INPUTS INPUTS/OUTPUTS

nOE

AB

nOE

BA

nA

n

nB

n

L L A = B inputs

H H inputs B = A

LHZZ

H L A=B B=A

PIN SYMBOL DESCRIPTION

1, 24 1OEAB, 2OE

AB

output enable input (active HIGH)

2, 3, 5, 6, 8, 9, 11, 12 1B

0

to 1B

7

data inputs/outputs

4, 10, 15, 21, 28, 34, 39, 45 GND ground (0 V)

7, 18, 31, 42 V

CC

DC supply voltage

13, 14, 16, 17, 19, 20, 22, 23 2B

0

to 2B

7

data inputs/outputs

25, 48 2

OEBA, 1OE

BA

output enable input (active LOW)

26, 27, 29, 30, 32, 33, 35, 36 2A

7

to 2A

0

data inputs/outputs

37, 38, 40, 41, 43, 44, 46, 47 1A

7

to 1A

0

data inputs/outputs

1999 Sep 20 4

Philips Semiconductors Product specification

16-bit transceiver with dual enable; 3-state 74ALVCH16623

Fig.1 Pin configuration.

page

16623

MNA307

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

26

25

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

1OE

AB

1B

0

1B

1

GND

1B

2

1B

3

V

CC

1B

4

1B

5

GND

1B

6

1B

7

2B

0

2B

1

GND

2B

2

2B

3

V

CC

2B

4

2B

5

GND

2B

6

2B

7

2OE

AB

1OE

BA

1A

0

1A

1

GND

1A

2

1A

3

V

CC

1A

4

1A

5

GND

1A

6

1A

7

2A

0

2A

1

GND

2A

2

2A

3

V

CC

2A

4

2A

5

GND

2A

6

2A

7

2OE

BA

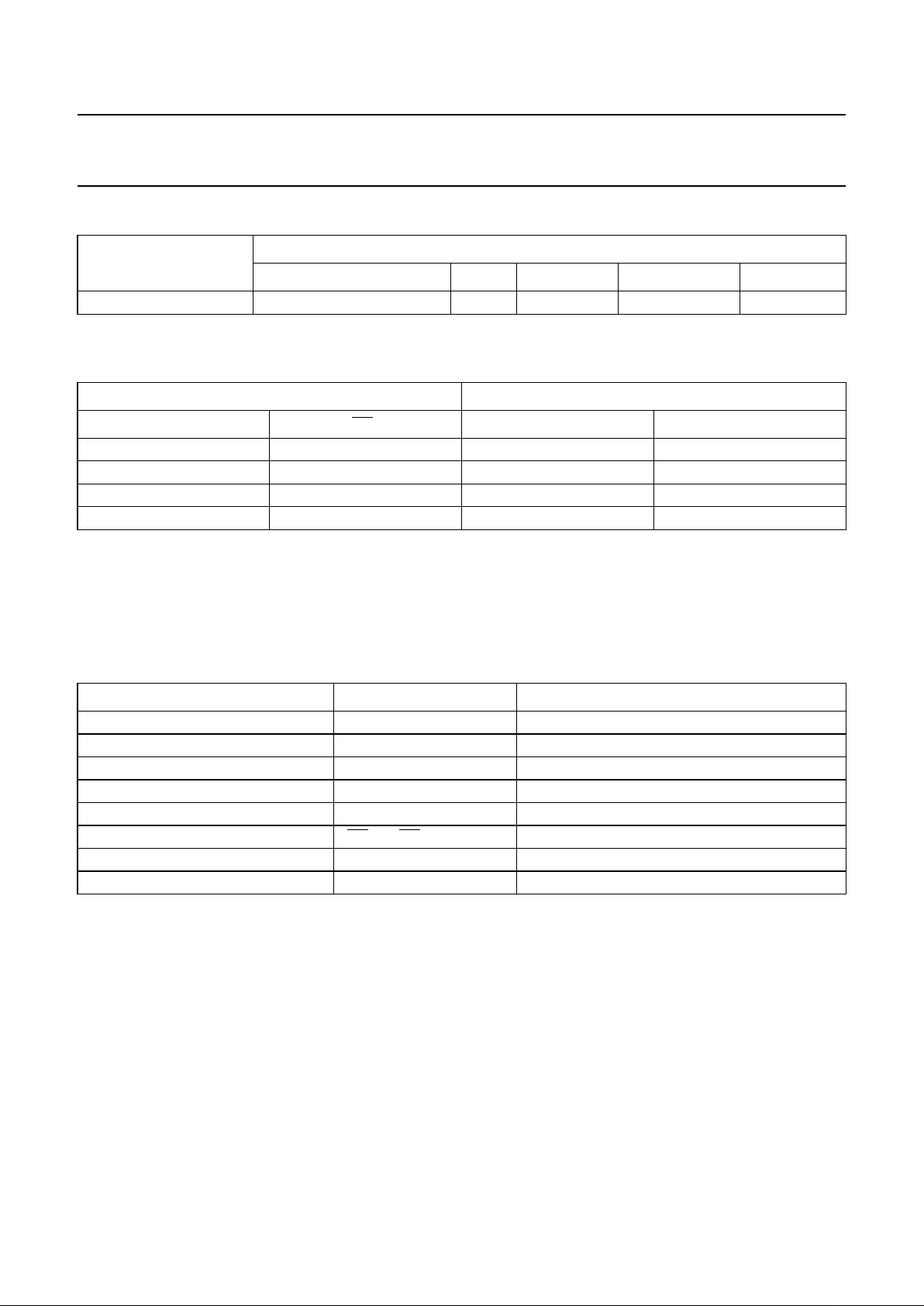

Fig.2 Logic symbol.

47

2

1B

0

1B

1

1B

2

1B

3

1B

4

1B

5

1B

6

1B

7

2B

0

2B

1

2B

2

2B

3

2B

4

2B

5

2B

6

2B

7

46

3

44

5

43

6

41

8

40

9

38

11

37

1A

0

1A

1

1A

2

1A

3

1A

4

1A

5

1A

6

1A

7

2A

0

2A

1

2A

2

2A

3

2A

4

2A

5

2A

6

2A

7

12

36

13

35

14

33

16

32

17

30

19

29

20

27

22

26

23

MNA308

1

24

48

1OE

AB

1OE

BA

2OE

AB

2OE

BA

25

1999 Sep 20 5

Philips Semiconductors Product specification

16-bit transceiver with dual enable; 3-state 74ALVCH16623

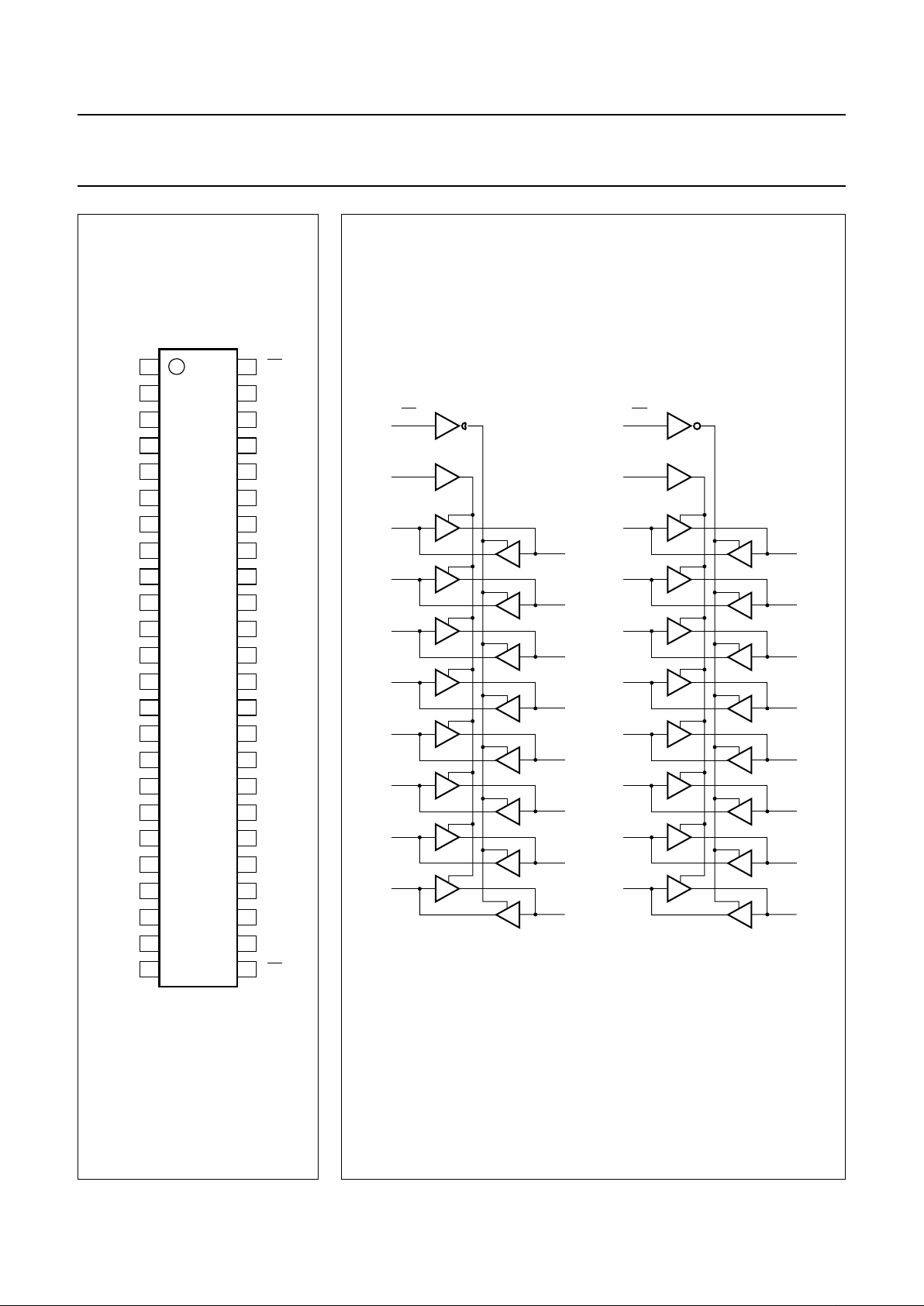

Fig.3 IEC logic symbol.

handbook, halfpage

346

1

48

2

1

5

44

6

43

8

41

9

40

11

38

1237

2

1EN1

1EN2

47

1435

24

25

2

1

16

33

17

32

19

30

20

29

22

27

2326

13

2EN1

2EN2

36

MNA309

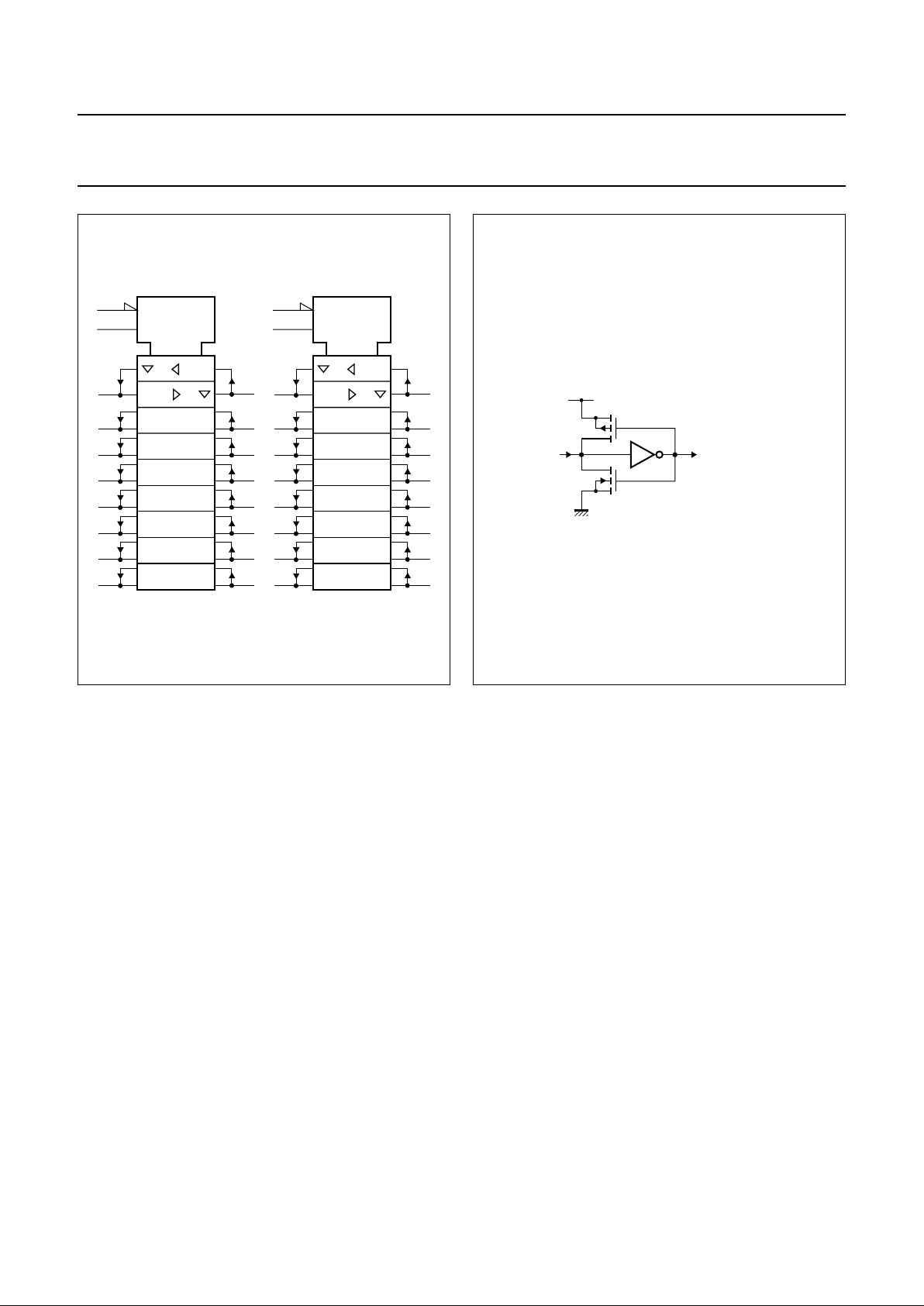

Fig.4 Bus hold circuit.

handbook, halfpage

to internal circuit

MNA310

V

CC

data

input

Loading...

Loading...