Philips 74ALVC16835DGG Datasheet

74ALVC16835A

18-bit registered driver (3-State)

Product specification

Replaces datasheet 74ALVC16835 of 1999 Mar 18

IC24 Data Handbook

2000 Mar 14

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

74AL VC16835A

18-bit registered driver (3-State)

2

2000 Mar 14 853–2190 23314

FEA TURES

•Wide supply voltage range of 1.2 V to 3.6 V

•Complies with JEDEC standard no. 8-1A.

•CMOS low power consumption

•Direct interface with TTL levels

•Current drive ± 24 mA at 3.0 V

•MULTIBYTE

TM

flow-through standard pin-out architecture

•Low inductance multiple V

CC

and GND pins for minimum noise

and ground bounce

•Output drive capability 50 Ω transmission lines @ 85°C

•Input diodes to accommodate strong drivers

DESCRIPTION

The 74ALVC16835A is a 18–bit registered driver. Data flow is

controlled by active low output enable (OE

), active low latch enable

(LE

) and clock inputs (CP).

When LE

is LOW, the A to Y data flow is transparent. When LE is

HIGH and CP is held at LOW or HIGH, the data is latched; on the

LOW to HIGH transient of CP the A-data is stored in the

latch/flip-flop.

When OE

is LOW the outputs are active. When OE is HIGH, the

outputs go to the high impedance OFF–state. Operation of the OE

input does not affect the state of the latch/flip-flop.

To ensure the high-impedance state during power up or power

down, OE

should be tied to VCC through a pullup resistor; the

minimum value of the resistor is determined by the current-sinking

capability of the driver.

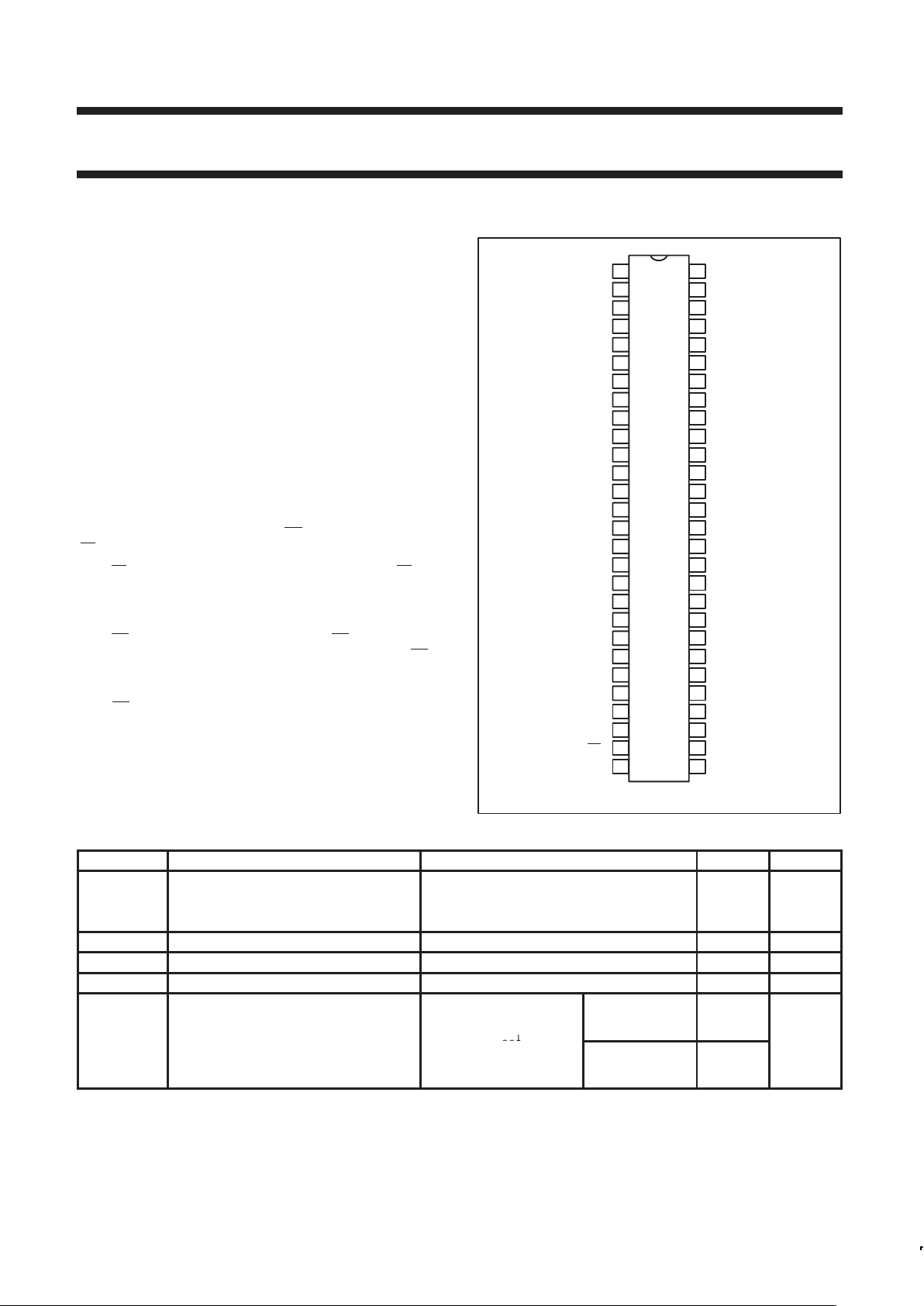

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28 29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56NC

NC

Y

1

Y

2

Y

3

Y

4

Y

5

Y

6

GND

V

CC

GND

Y

7

Y

8

Y

9

Y

10

Y

11

Y

12

GND

Y

13

Y

14

Y

15

V

CC

Y

16

Y

17

GND

Y

18

OE

LE

GND

NC

A

1

GND

A

2

A

3

V

CC

A

4

A

5

A

6

GND

A

7

A

8

A

9

A

10

A

11

A

12

GND

A

13

A

14

A

15

V

CC

A

16

A

17

GND

A

18

CP

GND

SH00188

QUICK REFERENCE DA TA

GND = 0 V; T

amb

= 25°C; tr = tf ≤ 2.5 ns

SYMBOL

PARAMETER CONDITIONS TYPICAL UNIT

t

PHL/tPLH

Propagation delay

An to Yn;

LE to Yn;

CP to Yn

VCC = 3.3 V, CL = 50 pF

2.3

2.6

2.5

ns

f

max

Maximum clock frequency VCC = 3.3 V, CL = 50 pF 350 MHz

C

I

Input capacitance 4.0 pF

C

I/O

Input/Output capacitance 8.0 pF

p

p

p

transparent mode

Output enabled

Output disabled

13

3

p

CPDPower dissipation capacitance per buffer

V

I

=

GND to V

CC

1

Clocked mode

Output enabled

Output disabled

22

15

pF

NOTES:

1. C

PD

is used to determine the dynamic power dissipation (PD in µW):

P

D

= CPD × V

CC

2

× fi + S (CL × V

CC

2

× fo) where: fi = input frequency in MHz; CL = output load capacitance in pF;

f

o

= output frequency in MHz; VCC = supply voltage in V; S (CL × V

CC

2

× fo) = sum of outputs.

Philips Semiconductors Product specification

74AL VC16835A

18-bit registered driver (3-State)

2000 Mar 14

3

ORDERING INFORMATION

PACKAGES

TEMPERATURE

RANGE

ORDER CODE

DRAWING

NUMBER

56-Pin Plastic Thin Shrink Small Outline (TSSOP) Type II –40°C to +85°C 74ALVC16835A DGG SOT364-1

PIN DESCRIPTION

PIN NUMBER SYMBOL NAME AND FUNCTION

1, 2, 55 NC No connection

3, 5, 6, 8, 9, 10, 12, 13,

14, 15, 16, 17, 19, 20,

21, 23, 24, 26

Y1 to Y18Data outputs

4, 11, 18, 25, 32, 39, 46,

53, 56

GND Ground (0V)

7, 22, 35, 50 V

CC

Positive supply voltage

27 OE

Output enable input

(active LOW)

28 LE

Latch enable input

(active LOW)

30 CP Clock input

54, 52, 51, 49, 48, 47,

45, 44, 43, 42, 41, 40,

38, 37, 36, 34, 33, 31

A1 to A18Data inputs

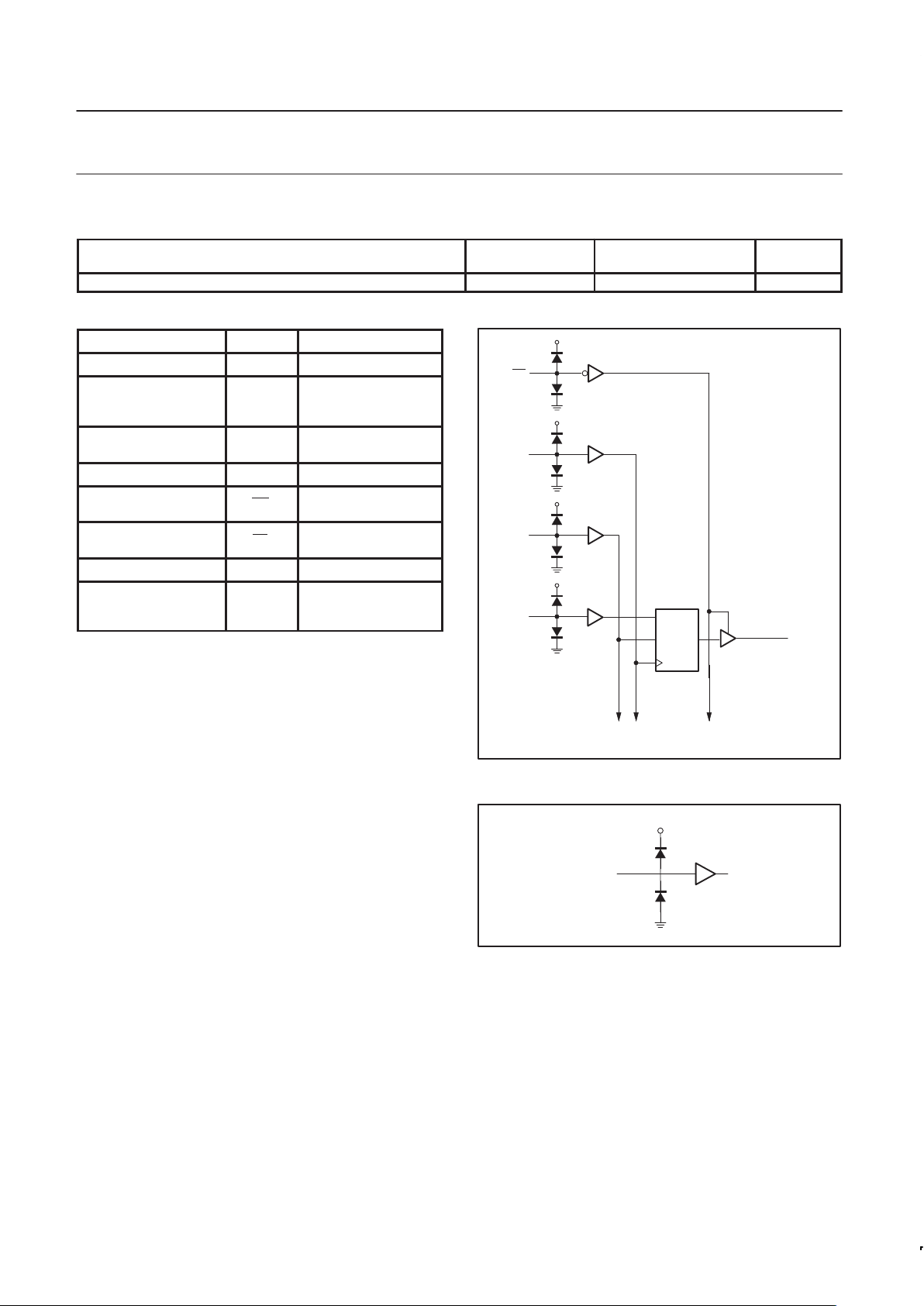

LOGIC SYMBOL

SH00203

CP

LE

D

OE

LE

A

1

Y

1

TO THE 17 OTHER CHANNELS

CP

TYPICAL INPUT (DATA OR CONTROL)

SH00200

A1

V

CC

Philips Semiconductors Product specification

74AL VC16835A

18-bit registered driver (3-State)

2000 Mar 14

4

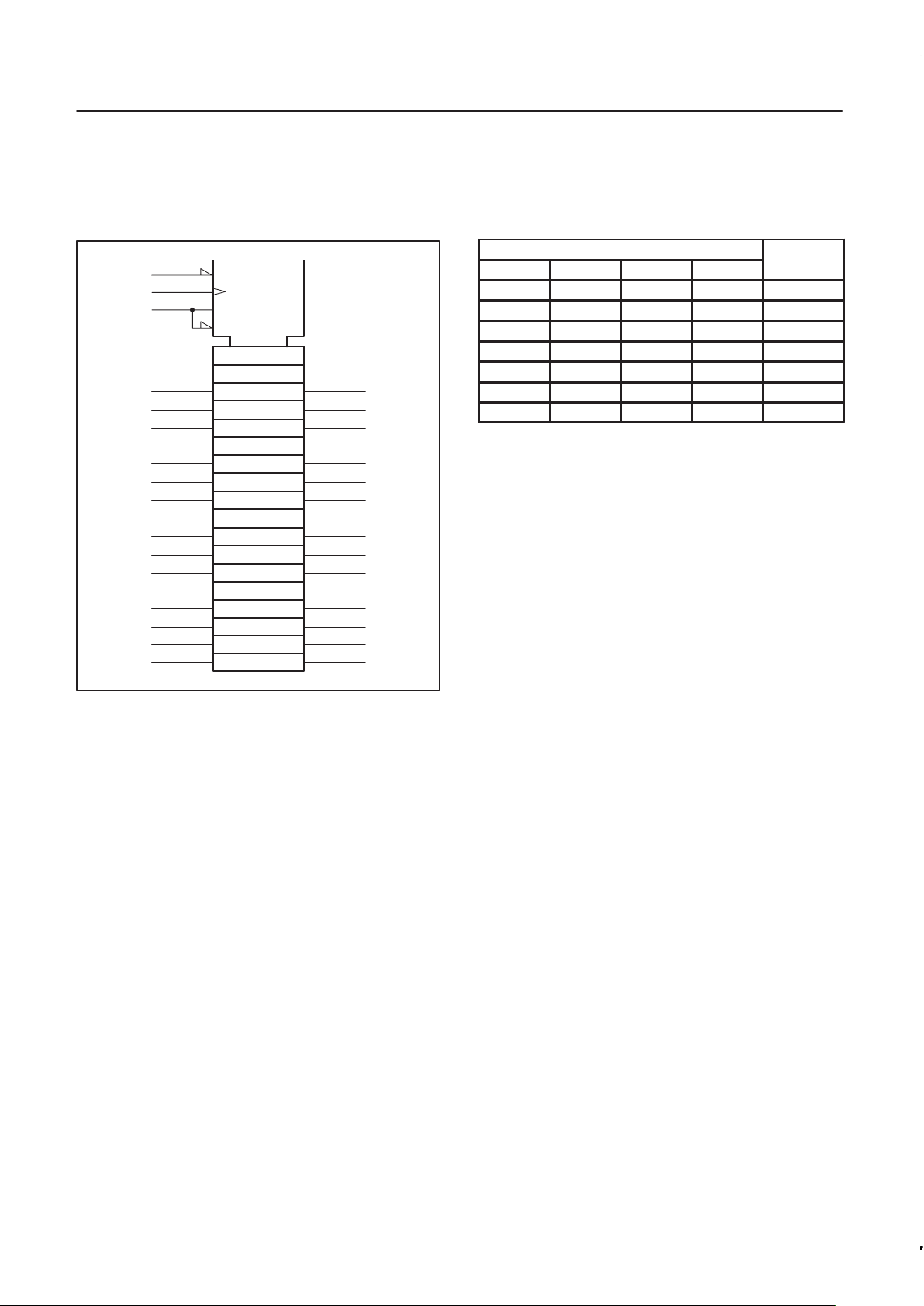

LOGIC SYMBOL (IEEE/IEC)

1, 2 ∇

5, 6 ∇

30

28

54

52

51

49

48

47

45

44

43

42

41

40

38

37

36

34

33

31

3

5

6

8

9

10

12

13

14

15

16

17

19

20

21

23

24

25

4D

8D

27

3C4

EN5

G7

A

18

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

8

A

9

A

10

A

11

A

12

A

13

A

14

A

15

A

16

A

17

OE

CP

Y

18

Y

1

Y

2

Y

3

Y

4

Y

5

Y

6

Y

7

Y

8

Y

9

Y

10

Y

11

Y

12

Y

13

Y

14

Y

15

Y

16

Y

17

LE

SH00190

FUNCTION TABLE

INPUTS

OE LE CP A

OUTPUTS

H X X X Z

L H X L L

L H X H H

L L ↑ L L

L L ↑ H H

L L H X Y

0

1

L L L X Y

0

2

H = HIGH voltage level

L = LOW voltage level

X = Don’t care

Z = High impedance “off” state

↑ = LOW-to-HIGH level transition

NOTES:

1. Output level before the indicated steady-state input conditions

were established, provided that CP is high before LE goes low.

2. Output level before the indicated steady-state input conditions

were established.

Loading...

Loading...