Philips 74ALS164N, 74ALS164D Datasheet

INTEGRATED CIRCUITS

74ALS164

8–bit serial–in parallel–out shift register

Product specification

IC05 Data Handbook

1991 Feb 08

Philips Semiconductors Product specification

74ALS1648-bit serial-in parallel-out shift register

FEA TURES

•Gated serial data inputs

•Typical shift frequency of 75MHz

•Asynchronous master reset

•Buffered clock and data inputs

•Fully synchronous data transfer

DESCRIPTION

The 74ALS164 is an 8-bit edge-triggered shift register with serial

data entry and an output from each of the eight stages. Data is

entered serially through one of two inputs (Dsa, Dsb); either input

can be used as an active-high enable for data entry through the

other input. Both inputs must be connected together or an unused

input must be tied High.

Data shifts one place to the right on each Low-to-high transition of

the clock (CP) input, and enters into Q0 the logical AND of the two

data inputs (Dsa, Dsb) that existed one setup time before the rising

edge. A Low level on the Master reset (MR

inputs and clears the register asynchronously, forcing all outputs

Low.

) input overrides all other

PIN CONFIGURATION

V

14

CC

Q7

13

Q6

12

Q5

11

Q4

10

MR

9

87

CP

TYPICAL

SUPPLY CURRENT

(TOTAL)

TYPE

Dsa

Dsb

Q0

Q1

Q2

Q3

GND

1

2

3

4

5

6

TYPICAL

f

MAX

74ALS164 75MHz 10mA

ORDERING INFORMATION

ORDER CODE

DESCRIPTION COMMERCIAL RANGE

V

= 5V ±10%,

CC

T

= 0°C to +70°C

amb

14-pin plastic DIP 74ALS164N SOT27-1

14-pin plastic SO 74ALS164D SOT108-1

DRAWING

NUMBER

SF00717

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

Dsa, Dsb Data inputs 1.0/1.0 20µA/0.1mA

CP Clock Pulse input (active rising edge) 1.0/1.0 20µA/0.1mA

MR Master Reset input (active-Low) 1.0/1.0 20µA/0.1mA

Q0 – Q7 Data outputs 20/80 0.4mA/8mA

NOTE: One (1.0) ALS unit load is defined as: 20µA in the High state and 0.1mA in the Low state.

LOGIC SYMBOL

8

9

= Pin 14

V

CC

GND = Pin 7

12

CP

MR

Dsa Dsb

Q0

Q1 Q3 Q4

3 4 5 6 10 11 12 13

Q0 Q1 Q3 Q4

SF00713

IEC/IEEE SYMBOL

74ALS (U.L.)

HIGH/LOW

8

9

1

2

R

SRG8

C1/→

&

1D

LOAD VALUE

HIGH/LOW

3

4

5

6

10

11

12

13

SF00714

1991 Feb 08 853–1510 01670

2

Philips Semiconductors Product specification

OPERATING MODE

Shift

74ALS1648-bit serial-in parallel-out shift register

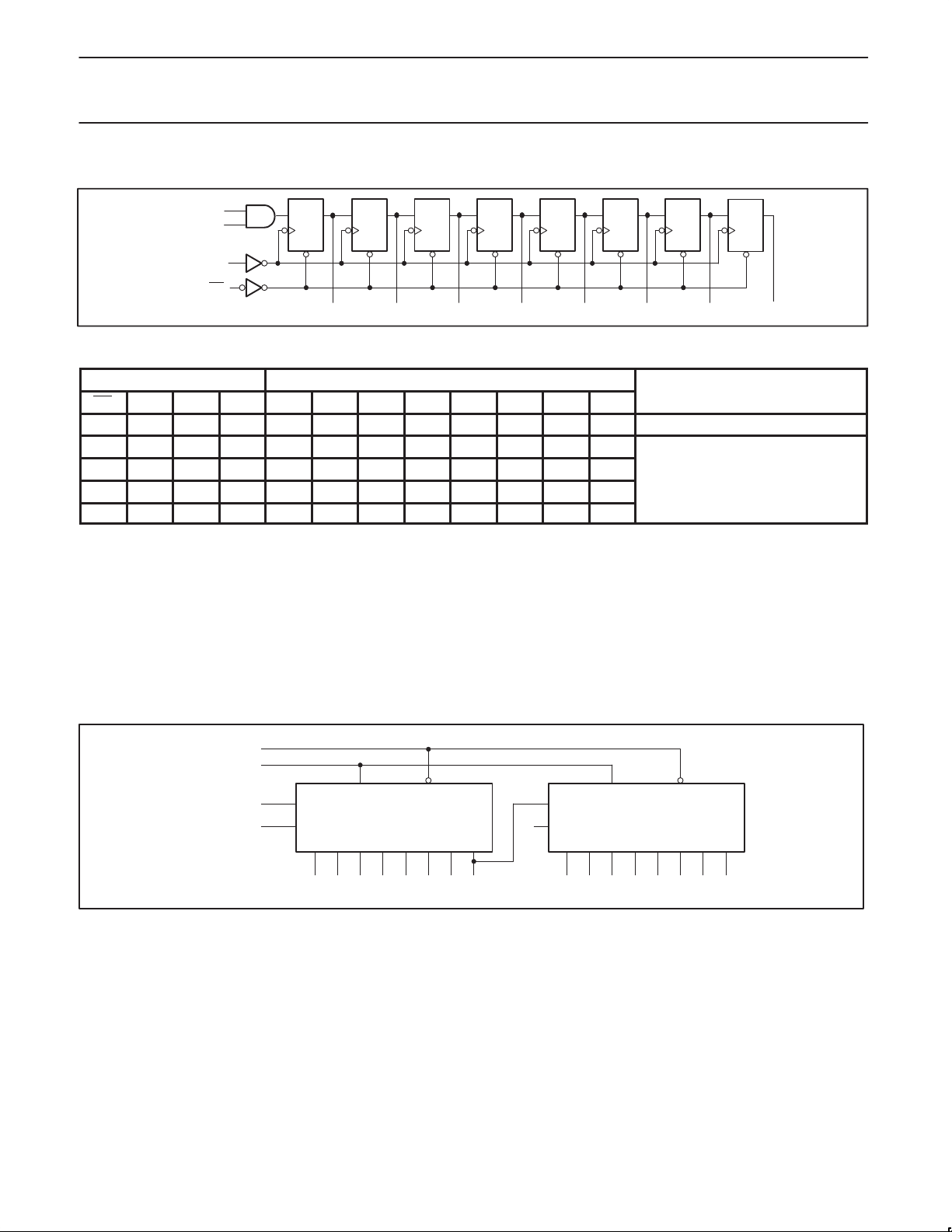

LOGIC DIAGRAM

1

Dsa

2

Dsb

8

CP

9

= Pin 14

V

CC

GND = Pin 7

MR

MODE SELECT FUNCTION TABLE

INPUTS OUTPUTS

MR CP Dsa Dsb Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

L X X X L L L L L L L L Reset (Clear)

H ↑ l l L q0 q1 q2 q3 q4 q5 q6

H ↑ l h L q0 q1 q2 q3 q4 q5 q6

H ↑ h l L q0 q1 q2 q3 q4 q5 q6

H ↑ h h H q0 q1 q2 q3 q4 q5 q6

NOTES:

H = High voltage level

h = High voltage level one setup time prior to the Low-to-High clock transition

L = Low voltage level

l = Low voltage level one setup time prior to the Low-to-High clock transition

qn = Lower case letter indicate the state of the referenced output one setup time prior to the Low-to-High clock transition.

X = Don’t care

↑ = Low-to-High clock transition

DQ

RD

Q0

3

DQ

RD

Q1

DQ

4

RD

Q2

DQ

5

RD

Q3

DQ

6

RD

Q4

10

DQ

RD

Q5

11

DQ

RD

Q6

12

DQ

CPCPCPCPCPCPCPCP

RD

Q7

13

SF00715

APPLICATION

The 74ALS164 can be cascaded to form synchronous shift registers of longer length.

Here, two devices are combined to form a 16-bit shift register.

CLEAR

CLOCK

DATA

ENABLE

Dsa

Dsb

CP MR

74ALS164 74ALS164

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

D0 D1 D2 D3 D4 D5 D6 D7

H

Dsa

Dsb

CP MR

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

D8 D9 D10 D11 D12 D13 D14 D15

SC00063

1991 Feb 08

3

Loading...

Loading...