Philips 74als153 DATASHEETS

INTEGRATED CIRCUITS

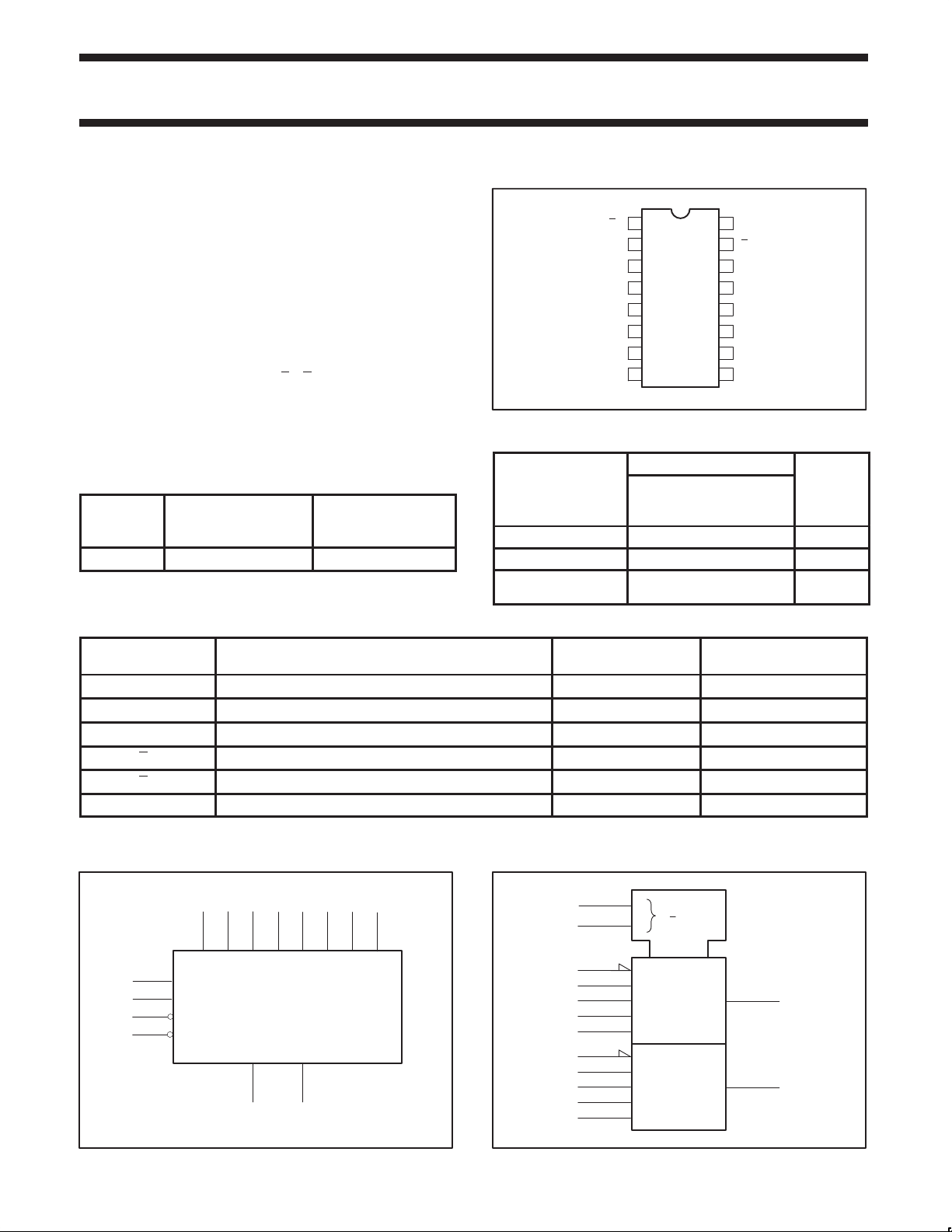

74ALS153

Dual 4-input multiplexer

Product specification 1991 Feb 08

IC05 Data Handbook

Philips Semiconductors Product specification

74ALS153Dual 4-input multiplexer

FEA TURES

PIN CONFIGURATION

•Non–inverting outputs

E

1

•Common select outputs

•Separate enable for each section

•See 74ALS253 for 3–State version

DESCRIPTION

The 74ALS153 has two identical 4–input multiplexer with 3–State

outputs which selects two bits of data from four sources by using

common select inputs (S0, S1). The two 4–input multiplexer circuits

have individual active–Low enables (E

strobe the outputs independently. Outputs (Ya, Yb) are forced Low

when the corresponding enable is high.

The 74ALS153 is the logic implementation of a 2–pole, 4–position

switch where the position of the switch is determined by the logic

levels supplied to the common select inputs.

TYPE

TYPICAL

PROPAGATION DELAY

74ALS153 7.0ns 6.5mA

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

Ioa – I3a Port A data inputs 1.0/1.0 20µA/0.1mA

Iob – I3b Port B data inputs 1.0/1.0 20µA/0.1mA

S0, S1 Common select inputs 1.0/1.0 20µA/0.1mA

Ea Port A enable input 1.0/1.0 20µA/0.1mA

Eb Port B enable input 1.0/1.0 20µA/0.1mA

Ya, Yb Data outputs 130/240 2.6mA/24mA

NOTE: One (1.0) ALS unit load is defined as: 20µA in the High state and 0.1mA in the Low state.

a, Eb) which can be used to

TYPICAL

SUPPLY CURRENT

(TOTAL)

ORDERING INFORMA TION

DESCRIPTION COMMERCIAL RANGE

16-pin plastic DIP 74ALS153N SOT38-4

16-pin plastic SO 74ALS153D SOT109-1

16-pin plastic SSOP

Type II

a

2

S1

3

I3a

4

I2a

5

I1a

6

I0a

Ya

74ALS (U.L.)

HIGH/LOW

ORDER CODE

V

= 5V ±10%,

CC

T

= 0°C to +70°C

amb

74ALS153DB SOT338-1

16

V

CC

b

15

E

S0

14

13

I3b

12

I2b

11

I1b

107

I0b

98GND Yb

LOAD VALUE

HIGH/LOW

SF00146

DRAWING

NUMBER

LOGIC SYMBOL

I1a I2a

43

I3aI0a

Ya

7

10 11

Yb

9

I1b I2b

12 13

I3bI0b

SF00147

65

14

2

1

15

V

= Pin 16

CC

GND = Pin 8

S0

S1

Ea

Eb

1991 Feb 08 853–1376 01670

IEC/IEEE SYMBOL

2

14

2

1

6

5

4

3

15

10

11

12

13

EN

0

0

G

3

1

MUX

0

1

2

3

7

9

SF00148

Philips Semiconductors Product specification

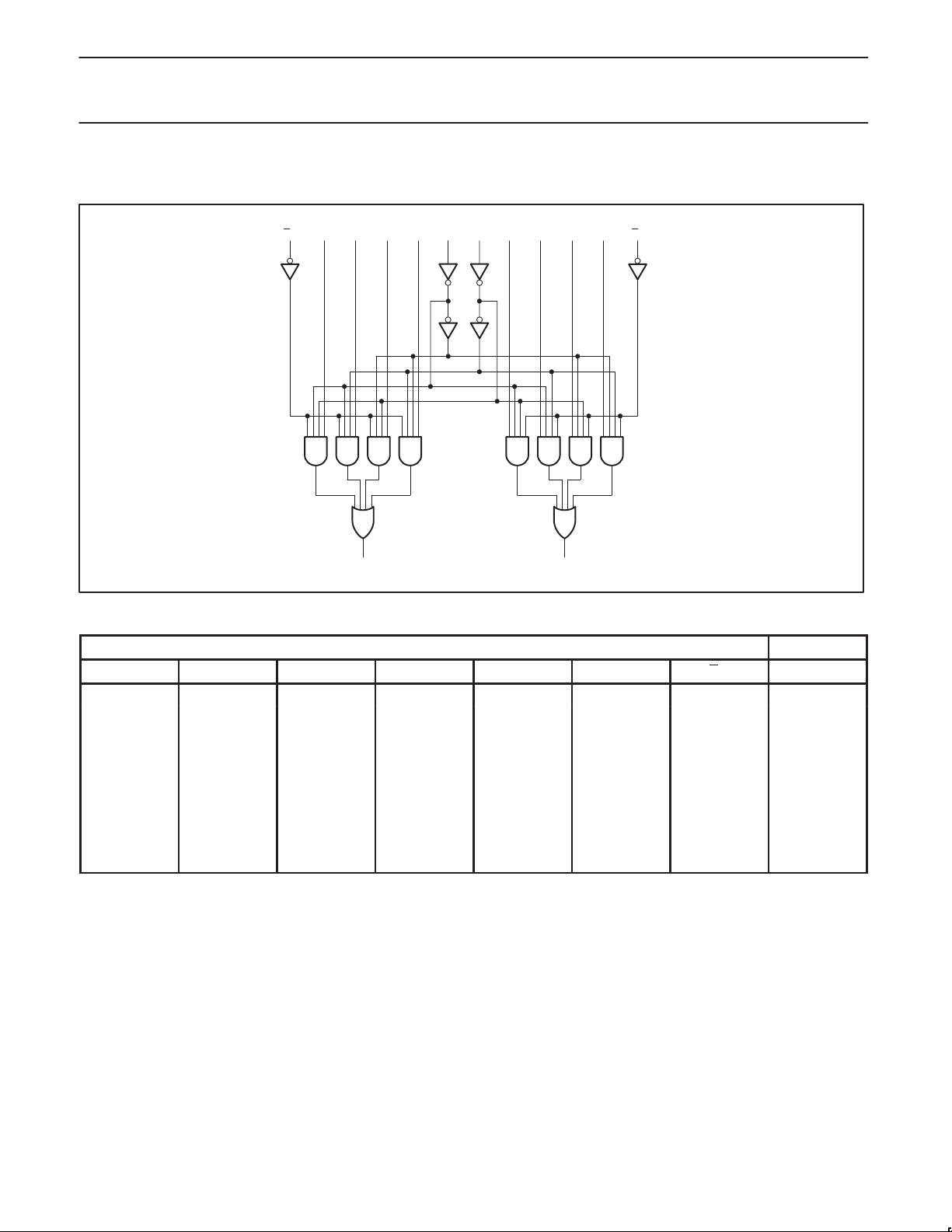

74ALS153Dual 4-input multiplexer

LOGIC DIAGRAM

a EbI0a I1a I2a I3a S1 S2 I0b I0b I2b I3b

E

1 65432141011121315

= Pin 16

V

CC

GND = Pin 8

7

Ya Yb

9

FUNCTION TABLE

INPUTS OUTPUT

S0 S1 I0n I1n I2n I3n En Yn

L L L X X X L L

L L H X X X L H

H L X L X X L L

H L X H X X L H

L H X X L X L L

L H X X H X L H

H H X X X L L L

H H X X X H L H

H = High voltage level

L = Low voltage level

X = Don’t care

SF00149A

1991 Feb 08

3

Loading...

Loading...